通用高精度时钟同步单元的设计方案

张园园,吴 宁,周 磊,周 芳,葛 芬

(1. 南京航空航天大学 电子信息工程学院,江苏 南京 211106;2. 扬州大学 信息工程学院,江苏 扬州 225127)

0 引言

高精度同步时钟装置在电力系统故障录波、靶场时统和地震监测等诸多测量系统中得到了广泛的应用[1- 4]。该类装置通常使用全球定位系统(GPS)接收机作为同步时钟参考源,当GPS信号受到干扰而不稳定时,使用高精度晶振进行本地守时[5]。目前,对于同步时钟装置的研究主要集中在对GPS秒脉冲随机误差和晶振频率漂移的抑制[6]。文献[7]中利用时间差预设补偿法产生精度为300 ns的同步时钟信号。文献[8]中使用均值法抑制GPS秒脉冲的随机误差,产生精度为100 ns、守时漂移为500 ns/h的同步时钟信号。文献[9-12]根据数字锁相环原理,通过对GPS秒脉冲的跟踪锁定,在本地维持一个接近理想秒脉冲的同步信号,从而实现高精度同步时钟信号的产生。现有的同步时钟装置设计方案在精度上已达到较高的水平,但仍存在着一些不足,如通过较高的现场可编程门阵列(FPGA)主频提高同步时钟精度,导致所设计的系统无法满足时序约束,抗干扰能力低,难以实用[13];采用FPGA+CPU的硬件设计架构,增加了系统的硬件复杂度和设计成本,缺乏通用性。

近年来,随着PULPino、Rocket等一批性能优异的开源处理器的出现以及ARM公司对Cortex-M0和Cortex-M3内核的免授权处理,基于开源处理器在FPGA中定制片上系统(SoC)已经成为嵌入式系统一种新的设计模式[14]。这种设计可以融合FPGA和CPU各自的优势并有利于减小系统面积。同时,当芯片需求较大时,可直接将现有设计投入供专门应用的集成电路(ASIC)的生产,进一步提高性能。

本文首先通过对同步时钟装置守时误差的分析研究,针对装置中的测量误差,提出一种可进一步提高守时精度的优化设计方案。该方案使用内插时钟和多周期测量的方法降低GPS秒脉冲的周期测量误差,对均值计算过程进行余数补偿,消除计算误差,最终实现高精度同步时钟的生成。同时,根据基于开源处理器定制SoC的设计模式,将所设计的同步时钟单元进行知识产权(IP)化,设计并实现一个具有APB总线接口的同步时钟IP核,其能够灵活地挂载在各个处理器内核上,使设计的同步时钟单元可应用于电力故障录波、地震监测等诸多系统,从而增加了同步时钟单元的通用性,避免了重复开发。

1 同步时钟守时误差分析

当GPS接收机失步后,GPS秒脉冲的周期均值成为守时系统的唯一先验信息,其与标准秒脉冲的误差将直接决定系统的守时精度。设GPS接收机失步前GPS秒脉冲周期均值和理想秒脉冲之间存在大小为δ的偏差,则守时1 h后守时脉冲的误差为3 600δ。由秒脉冲周期均值的计算原理可知,当硬件平台选定后,偏差δ受GPS秒脉冲自身误差Δgps、周期测量误差Δcal、均值计算误差Δavr和均值求取长度L的联合影响。

1.1 平台选型分析

高精度同步时钟装置选用不同的平台架构将对装置的精度、体积和通用性产生较大影响。目前,高精度同步时钟装置的实现平台主要有CPU、FPGA+CPU、FPGA和FPGA+软核4种。基于CPU的时钟同步装置由于CPU执行指令的不确定性,增加了时间测量的误差;基于FPGA开发的同步时钟装置虽然精度较高但通用性差[15];采用FPGA+CPU架构设计的同步时钟装置,系统的硬件复杂度和设计成本都较高;FPGA+软核架构则充分融合了FPGA的高性能和CPU的通用性,能够以较小的成本实现高精度时钟同步,本文设计的同步时钟装置即采用该结构。

1.2 GPS秒脉冲误差分析

GPS接收机生成的秒脉冲信号与标准秒脉冲之间存在一定的随机误差Δgps,该误差服从正态分布[15],对于1个N点误差样本有:

(1)

其中,标准差σgps与所使用的GPS接收机有关[16],通用型GPS接收机的σgps在40 ns左右,而部分授时型GPS接收机的σgps可低至20 ns左右,如NEO-6M型GPS接收机的σgps为30 ns,本系统采用的UM220-ⅢGPS接收机的σgps为20 ns。

GPS秒脉冲的随机误差将会影响系统对晶振频率的估计,从而导致在守时阶段同步时钟产生较大的偏移。

1.3 测量误差分析

同步时钟装置测量误差主要由GPS秒脉冲周期测量误差和秒脉冲周期均值计算误差两部分构成。由于GPS接收机输出的秒脉冲相对于FPGA时钟为一个异步信号,如果直接使用FPGA时钟对GPS秒脉冲信号进行边沿检测,那么会产生一个服从U(0,T)分布的边沿检测误差。根据均匀分布的和差公式可知,该测量方法引入的GPS秒脉冲周期测量误差概率密度函数为:

(2)

其中,T为FPGA时钟周期。根据GPS秒脉冲周期测量误差的概率密度可计算GPS秒脉冲周期测量误差的标准差σcal为:

(3)

GPS秒脉冲周期均值计算单元是同步时钟装置的重要组成部分,用于计算GPS秒脉冲信号周期的算术平均值,减少秒脉冲周期随机误差对守时精度的影响。已有设计通常对均值计算的余数进行四舍五入,这在GPS秒脉冲周期均值中引入了服从在(-0.5/T,0.5/T)上均匀分布的测量误差。该误差的标准差σavr为:

(4)

在目前的同步时钟装置设计过程中,GPS秒脉冲周期测量误差和秒脉冲周期均值计算误差通常会被忽略,但当守时精度不断提高后,GPS秒脉冲周期测量误差在守时误差中所占比重逐渐升高,已成为制约同步时钟装置守时精度进一步提高的一大阻碍。

1.4 守时误差分析

根据统计学中的中心极限定理,从一个方差为σ2的样本容器中以长度L进行均值求取,当L足够大时样本的算数平均值近似满足方差为σ2/L的正态分布,可得到δ的标准差σkeep如式(5)所示。

(5)

将1.1与1.2节中计算得到的各误差结果代入式(5),得到:

(6)

2 同步时钟单元优化设计与实现

2.1 守时精度优化方案

根据对同步时钟守时误差的分析,从降低GPS秒脉冲周期测量误差的角度,提出了一种优化设计方案以提高同步时钟装置的守时精度。该方案使用长时间均值求取抑制GPS秒脉冲随机误差Δgps,通过内插时钟来降低秒脉冲测量时的量化误差Δcal,同时修正均值余数以消除计算误差Δavr。

(7)

由于在周期测量过程中对秒脉冲的周期进行了以8 s为单位的平均值计算,所以GPS秒脉冲随机误差的标准差变为:

(8)

(9)

结合1.4节分析,将所提出的优化方案与文献[8]中的均值法进行对比。文献[8]中均值法的步骤如下:

a. 对GPS秒脉冲周期测量值进行16个周期的均值计算;

b. 将步骤a计算得到的均值与最新一个GPS秒脉冲周期求平均;

c. 将步骤b得到的计算结果进行L次平均,作为GPS失步后的系统秒脉冲周期。

(10)

GPS秒脉冲随机误差的标准差可表示为:

(11)

(12)

对本文所提出的优化方案、传统守时方案和文献[6]中的均值法方案进行守时性能对比,为便于直观比较,各表达式中的GPS秒脉冲误差的标准差设为20 ns,时钟周期T设为10 ns,均值长度L设为8 192 s,对比结果如表1所示。

表1 守时精度对比表Table 1 Comparison of time-keeping accuracy

由表1可知,本文设计的优化方案可在较大程度上提高同步时钟装置的守时精度,在GPS失步后的1 h内,理论上仍可维持300 ns的时钟精度。

2.2 同步时钟单元设计

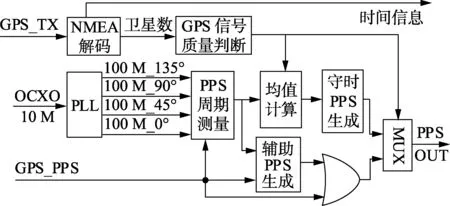

根据本文提出的守时优化方案,设计了一种高精度同步时钟产生单元,其结构如图1所示。

图1 高精度同步时钟单元结构Fig.1 Structure of synchronous clock unit with high precision

图1所示的单元以恒温晶振和GPS接收机作为参考时钟,最终可输出高精度秒脉冲信号和解码GPS得到的时间信息。

2.2.1 GPS秒脉冲周期测量模块

本文充分利用了FPGA中锁相环的相位设定功能,采用时钟内插方法提高对GPS秒脉冲周期的测量精度。针对GPS秒脉冲进行8倍时钟内插周期测量的原理如图2所示。

图2 周期测量示意图Fig.2 Schematic diagram of cycle measurement

利用锁相环产生4路相位差为45°、占空比为50%的时钟信号,使用4路时钟的上下边沿分别对GPS秒脉冲信号进行采样,实现最大误差为T/4的周期测量。本系统的时钟周期T为10 ns,即秒脉冲周期测量引入的最大量化误差为2.5 ns。

为了进一步降低GPS秒脉冲周期测量量化误差对精度的影响,同时抑制GPS秒脉冲信号本身的随机误差,在周期测量时以8个GPS秒脉冲为单位进行多周期测量,则可将2.5 ns的量化误差均分至8个周期,最大测量误差降低至312.5 ps。使用该方法引入的量化误差已远小于GPS秒脉冲本身存在的随机误差,能够在较大程度上提高GPS秒脉冲周期的测量精度。

2.2.2 周期均值计算模块

同步时钟单元中以8 192 s为长度对采集的GPS秒脉冲周期进行算数平均值的计算。由于测得的秒脉冲周期以32位无符号数进行保存,所以使用45位加法器进行8 192次累加即可实现均值求取,其中累加结果高32位为均值整数部分,低13位为均值小数部分。该方法占用逻辑资源小且计算精度高。

2.2.3 同步时钟信号生成

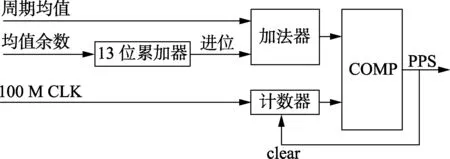

同步时钟单元共有GPS秒脉冲、辅助秒脉冲和守时秒脉冲3个同步时钟信号,系统根据GPS是否失步选取其中1个信号作为高精度同步时钟信号进行输出。GPS接收机工作正常时直接将GPS秒脉冲信号作为同步时钟进行输出;当GPS接收机已失步但尚未被检测到时,辅助秒脉冲信号将作为同步时钟输出;系统检测到GPS失步时系统进入守时状态,输出守时秒脉冲信号。守时秒脉冲生成模块结构如图3所示。

图3 守时秒脉冲模块结构Fig.3 Structure of time-keeping pulse module

守时秒脉冲生成模块以均值计算模块得到的前8 192个GPS秒脉冲的周期均值为基准对锁相环输出的100 M时钟进行计数,从而产生守时秒脉冲信号。同时,对均值计算产生的余数进行累加,利用累加进位信号对阈值进行补偿,从而消除均值除法计算产生的误差。

2.3 基于APB总线的通用同步时钟IP核设计

同步时钟装置被广泛应用于电力录波、靶场时统和地震监测等系统,本文对同步时钟生成功能进行IP化,使用标准的片上总线作为IP核的交互配置通道,使得设计的高精度同步时钟单元具有良好的可重用性,能够满足多种系统的时钟同步需求。

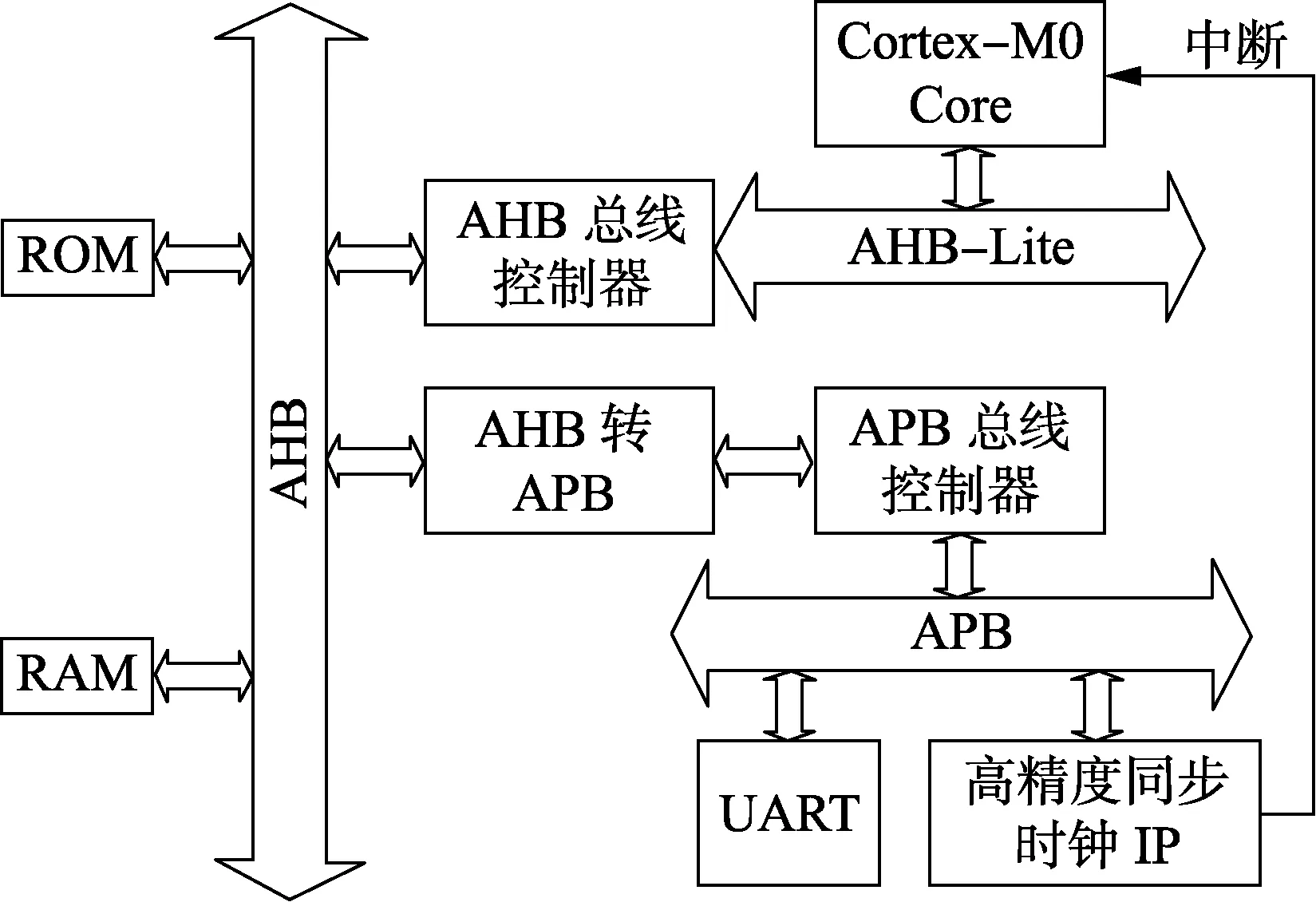

基于高精度同步时钟单元设计的具有APB总线接口的IP核可直接应用于具有APB总线的SoC,并可通过桥接挂载在AHB和AXI等片上总线。所设计的高精度同步时钟IP核整体结构如图4所示。

图4 高精度同步时钟IP核结构图Fig.4 Structure of synchronous clock IP core with high precision

同步时钟IP核由高精度同步时钟单元、系统时间生成单元、SoC中断生成单元和总线接口单元组成。系统时间生成单元根据提取到的GPS时间信息和每秒脉冲数(PPS)信号维持稳定的系统时间。高精度同步时钟单元为系统提供脉宽可配置的高精度脉冲信号,当GPS信号丢失时维持同步脉冲信号的精度。中断生成单元可根据系统配置产生秒中断、分中断、时中断和闹铃中断。总线接口单元支持APB总线,系统可对挂载在总线上的同步时钟IP进行数据交互和参数配置。

3 验证平台构建与测试

3.1 同步时钟IP核验证平台构建

基于ARM Cortex-M0内核在FPGA上设计一个具有高精度同步时钟生成功能的SoC。所构建的SoC由Cortex-M0内核、2 kB只读存储器(ROM)、8 kB 随机存取存储器(RAM)、通用异步收发传输器(UART) IP、高精度同步时钟IP和总线控制器组成,其结构如图5所示。

图5 SoC结构图Fig.5 Structure of SoC

FPGA选用Cyclone IV EP4CE115型,开发语言为Verilog,ARM软件开发环境使用MDK5,SoC外接UM220-III GPS接收机和10 MHz恒温晶振。

SoC中的 2 kB ROM用于程序存储,8 kB RAM作为堆栈空间,UART作为测试接口。各模块地址分布如表2所示。

3.2 同步时钟IP核性能测试

同步时钟装置的性能可由随机误差和守时误差两部分进行衡量。基于在FPGA上构建的具有同步时钟生成功能的SoC,对所设计的高精度同步时钟单元进行性能测试。测试系统记录同步时钟的周期并用串口进行输出,用于分析同步时钟的随机误差。在完成8 192 s的同步后,断开GPS接收机与FPGA的连接,使用高精度示波器观测守时阶段同步时钟信号和GPS秒脉冲信号的误差。

表2 SoC地址空间分布表Table 2 SoC address space mapping

GPS随机误差测试过程共重复3次,每次采集8 000个同步时钟周期样本,通过计算误差的概率密度,得到图6所示的概率密度曲线。由图6可知,同步时钟随机误差的概率密度符合正态分布的基本特征,同步时钟随机误差的方差为2.93,置信度99%的置信区间为[-5.14,5.14]ns。

图6 同步时钟随机误差概率密度曲线Fig.6 Curve of random error probability density of synchronous clock

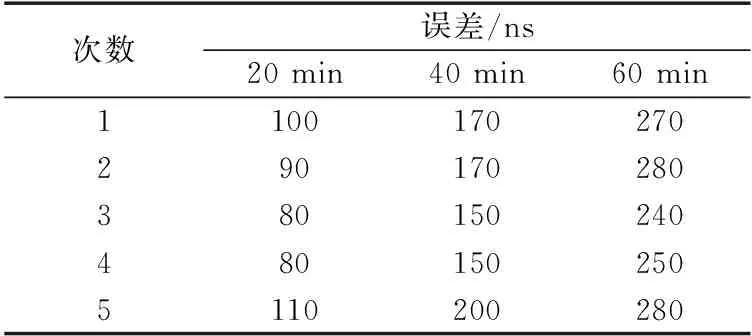

利用高精度示波器测量守时误差,每20 min记录一次守时误差,每次守时持续1 h。为避免偶然性,共计进行5次守时误差测量,测量结果如表3所示。

表3 守时误差测量结果Table 3 Measured results of time-keeping error

由表3可知,基于守时优化方案设计的高精度同步时钟单元在GPS接收机失步后,能够保持优于300 ns/h的守时精度。

4 结论

本文通过对同步时钟装置测量误差的分析研究,提出了一种提高守时精度的优化方案,根据该优化方案设计并实现了一个具有APB总线接口的通用高精度同步时钟IP核。在FPGA中构建了以Cortex-M0为核心的SoC对IP核进行了性能测试。测试结果表明,本文设计的同步时钟IP核所生成的秒脉冲精度优于20 ns,在GPS失步1 h内仍可保持300 ns/h的守时精度,满足电力录波、靶场时统和地震监测等系统的同步需求。同时,本文所设计的具有APB总线接口的同步时钟IP核也具有很强的通用性,可以灵活地应用于多种测量系统,符合嵌入式系统的发展潮流,具有良好的应用前景。