一种硅基新结构TG VDC SOI LIGBT

张海鹏,何 健,白建玲,张 强,王 颖,王 彬

(杭州电子科技大学 电子信息学院,浙江 杭州 310018)

绝缘层上半导体(Semiconductor on Insulator,SOI)高压集成电路因其绝缘性能好、工作速度快、热稳定性好和抗辐照能力强等优点己成为功率集成电路(Smart Power Integrated Circuits,SPIC)的重要发展方向[1-3]。基于SOI材料的横向绝缘栅极双极晶体管(Lateral Insulated Gate Bipolar Transistor,LIGBT)由于隔离性能好、寄生电容小、漏电流小及集成度高等优点被广泛应用到智能功率集成电路中[4-8]。Ey Goo Kang等人首次将槽栅(Trench Gate,TG)电极引入到了SOI LIGBT中,提高了器件的通态电流密度和击穿电压[9],但传统的槽栅SOI LIGBT已不能满足日益发展的SPIC对耐压性能和大电流处理能力的要求。因此,探索新器件结构、进一步改善器件性能已成为SPIC领域研究的热点之一。

在本文中,针对实际应用中SOI LIGBT耐压性能和大电流处理能力遭遇瓶颈的问题,在文献[10~12]的基础上,根据现有的具有P埋层(Buried P-type Layer,BPL)和槽栅极SOI LIGBT结构,结合已有BPL SOI LIGBT器件结构特点及其工作机理,提出一种槽栅极纵向双单元(Vertical Double Cells,VDC) SOI LIGBT器件结构。采用世界权威的嵌有TSUPREM-IV的TCAD (Technology Computer Aided Design)软件对这种TG VDC SOI LIGBT器件进行电学特性仿真,试验结果证明其具有良好的电学特性,可以满足SPIC的发展需要[13-14]。

1 器件结构及工作原理

1.1 器件结构

图1(a)和图1(b)分别图示出TG SOI LIGBT、TG VDC SOI LIGBT结构示意图。为了描述方便,本文简称TG SOI LIGBT为TG结构、TG VDC SOI LIGBT为TG VDC结构。图1中,D为漏极,G为栅极,S为源极,P-well为P阱,最下层为硅衬底(Silicon-Substrate,Si-Sub)。TG VDC结构是在TG结构的漂移区(N-type drift region,N-drift region)中沿纵向适当位置再引入了一个平行于初始埋氧层(Buried Oxide,BOX)的第二埋氧层。在第二埋氧层的上下两侧形成并联的两个TG结构单元的新结构。TG结构和TG VDC结构的对应区域掺杂浓度均相同。TG结构横向P阱结界面与集电结界面间距为9 μm,第一埋氧层厚度为0.05 μm,二者栅极长度均为3.24 μm,栅极对应的沟槽深度为3.5 μm,栅氧化层厚度为40 nm。第二埋氧层长度为10.5 μm,厚度为1.5 μm。BPL层的杂质浓度为4e18·cm-3。

图1 SOI LIGBT器件横向截面结构示意图

1.2 工艺可实现性

TG VDC SOI LIGBT的结构特点和工艺难点在于新引入的第二埋氧层部分。随着集成电路工艺的发展,选择性外延技术和DTI(Deep Trench Isolation)刻蚀技术的工艺也已经比较成熟。对于新结构引入的第二埋氧层可先在初始SOI衬底上进行顶层硅膜掺杂,再刻蚀氧化层、外延N型硅、刻蚀掩膜窗口,最后经两次横向选择性外延和DTI刻蚀完成。其他工艺步骤和常规槽栅LIGBT的工艺相同。

1.3 工作原理

器件内部的阳极P+区-N漂移区-P阱构成了横向PNP晶体管。工作时,通过在栅极—源极(或称阴极)之间加大于阈值电压VT的正向偏置电压,使得纵向栅极的硅一侧侧表面形成强反型N沟道[15]。同时,漏极(或称阳极)与源极之间接上一定的正向电压,此时源极下方的N+层便向沟道注入大量的电子,在N漂移区中向P+阳极扩散漂移,到达集电结的边界并开始积累。降低该PN结在漂移区一侧的电位,当该PN结正偏电压达到开启电压时,P+区的空穴就会大量注入到N型漂移区, 为横向PNP晶体管提供空穴电流[15],使得横向PNP晶体管进入大注入导通状态,从而器件充分导通。导通后,P+阳极层注入到N漂移区空穴和源极经沟道注入道漂移区的电子形成等离子体,调制漂移区电导率,使得电流密度大大提高,N漂移区的通态电阻大大降低。

2 电学特性仿真与分析

利用世界权威的嵌有TSUPREM-IV的TCAD软件中的器件仿真工具ATLAS对TG SOI LIGBT与TG VDC SOI LIGBT在可比条件下进行了电学特性仿真测试实验,实验结果分通态特性、击穿特性和转移特性三方面进行讨论。

2.1 通态特性仿真与分析

图3为TG 结构、TG VDC结构在栅极电压分别为2 V,5 V,10 V时的ID-VD输出特性曲线。从图3可以看出,TG 结构和TG VDC结构的集电结开启电压比较接近,约为0.7 V。但栅压为5 V时,可以看到TG 结构产生了明显的翘曲效应[16],这主要和器件的浮体效应有关。TG VDC结构两层N型漂移区中下层单元在通态时为上层单元的体区提供了背栅偏置,消除了上层单元的浮体效应的影响,从而减弱了翘曲效应。

图2 ID-VD特性曲线

图3对图2漏极电压从0 V~5 V部分进行了放大。根据图3所示结果,栅压为10 V条件下,当二者通态压降同取3 V时,TG结构通态电流为0.28 mA·μm-1,TG VDC结构通态电流为0.63 mA·μm-1,数值约为TG SOI LIGBT的2.25倍。当二者通态电流同取0.6 mA·μm-1,TG 结构的通态压降为2.8 V,而TG VDC结构的通态压降为4.3 V,约比前者降低了65%。同理,通态电阻也降低了65%。

TG VDC结构通态电流大、通态电阻小是因为器件导通时,该结构上下两单元都形成N型导电沟道,两层N型漂移区也更有利于导通时双极载流子疏运,从而有利于提高器件导通态电流密度。TG VDC结构上下两个单元漂移区都将产生电导率调制效应,通过降低N型漂移区的电阻率来降低器件的通态电阻。

图3 ID-VD特性曲线部分放大

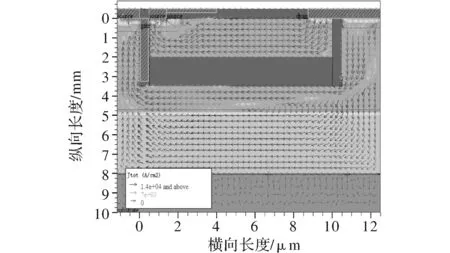

图4为栅压为10 V,漏极电压为20 V,源极和衬底接地时TG VDC结构的电流二维分布TCAD仿真结果。由图4可见,器件的栅极两侧分别形成了导电沟道,两层漂移区使得电流疏运能力更强。

图4 TG VDC SOI LIGBT二维通态电流分布

2.2 正向阻断态击穿电压仿真与分析

图5为TG 结构和TG VDC结构的正向阻断态击穿电压曲线。从图5中可知,TG结构的正向阻断态击穿电压约为47 V,而可比条件下,TG VDC结构的正向阻断态击穿电压约为100 V,超过TG 结构的2倍。

图5 正向阻断态击穿电压曲线

图6(a)和图6(b)分别图示出TG结构和TG VDC临界击穿电场分布图。从图6中可见,当器件达到临界击穿状态时,TG结构的电场尖峰只出现在P埋层/N漂移区结界面。而可比条件下,TG VDC结构上层单元中P阱/N漂移区结的拐角处、源极场板边缘下的硅表面及下层单元的源极侧纵向N漂移区与横向N漂移区拐点处及P埋层/N漂移区结一侧的电场尖峰几乎同时达到了各自位置的临界击穿电场,整体上改善了电场分布的均匀性。这主要和器件的结构有关,根据RESURF原理,TG VDC结构下层的N型漂移区可抽象为上层漂移区的阻性场板,消除了P阱/N漂移区耗尽层在N型区域侧下表面扩展受抑制现象,从而消除了下表面优先击穿的缺点。此外,呈凹形状的下层LIGBT漂移区加大了N型漂移区的长度,相比于TG结构,下层的LIGBT的电场分布也会更均匀。

图6 器件击穿等势线分布图

2.3 转移特性的仿真与分析

图7为TG结构和TG VDC结构在漏极电压为3 V时的转移特性曲线图。从图7中可以看出,TG结构的阈值电压约为1.8 V,而TG VDC结构的阈值电压都在2 V左右,符合开关器件的设计要求。阈值电压既不能设计的太大也不能太小,太小时,环境中存在的噪声等脉冲尖峰可能会导致器件的误导通;太大时,栅极的控制电压也要相应提高,增大了器件的输入功率和开启时间。

图7 转移特性曲线图

图8为TG结构和TG VDC结构转移特性的半对数坐标曲线。从图8中可见,二者的亚阈值斜率几乎相等,而在器件的亚阈值区,TG VDC结构的漏电流约比TG结构的漏电流低一个数量级;而当器件处于截止去时,前者的泄漏电流比后者的降低了一个数量级,有效的减小器件关断态静态功耗。

3 结束语

本文提出了一种新结构TG VDC SOI LIGBT。当器件处于导通态时,利用栅极两侧分别形成强反型层及上下两层N漂移区来增强电子的注入效率及增强漂移区电导调制效应,从而提高器件大电流处理能力,减小器件的导通电阻。当器件处于正向阻断态时,TG VDC SOI LIGBT的第二埋氧层将器件分成上下两层,下层的LIGBT的漂移区呈现凹形状,加大了N型漂移区的长度,可充当上层单元漂移区的阻性场板,从而改善器件电场分布的均匀性,使得器件在完全耗尽时可以得到更高的击穿电压。采用半导体器件仿真软件TCAD对TG SOI LIGBT和TG VDC SOI LIGBT进行了器件的电学特性模拟,结果表明,在可比结构参数下,TG VDC SOI LIGBT的通态电流提高了1.2倍,击穿电压提高了1倍,通态电阻降低了65%,泄漏电流降低了一个数量级。若通过合理的版图设计则可进一步显著提高TG VDC SOI LIGBT器件的电学性能。这对于SPIC等电力电子应用的节能降耗、低碳环保、可持续发展具有一定的现实意义。