X波段FMCW导航雷达射频前端设计与实现

蒋 青,罗栋梁,刘 峰

(重庆邮电大学 移动通信技术重点实验室,重庆 400065)

0 引 言

导航雷达作为当代雷达技术的一项重要应用领域,继20世纪40年代以来一直受到各国的重视,不论是在军事上的反恐作战、敌情预警,还是民用上的防撞规避、灾害救援等方面,都具有广泛的应用前景。1988年,Philips实验室将调频连续波(frequency modulated continuous wave, FMCW)技术引入到导航雷达系统中[1]。与传统脉冲雷达相比较,FMCW雷达系统的主要优点在于易实现极高的距离分辨率、不存在距离盲区、发射功率低、抗截取能力强,在近距离测量领域得到了广泛的应用[2],且X波段天线尺寸小、距离及方位分辨率高,有利于近距离目标探测[3]。

目前产生线性调频信号的方案主要有:①直接数字频率合成器(direct digital synthesizer,DDS)+锁相环技术;②多次倍频方案;③多次变频方案。这3种方案最终都能够产生满足频率、带宽要求的射频信号,但也存在缺陷,例如,无法兼顾线性调频时间、频率间隔和变频时间的关系。文献[4]指出,虽然锁相环技术可以改善输出信号的杂散和噪声性能,但是锁相环为负反馈系统,相位的锁定过程耗时相对较长,无法满足快速变频的要求。使用多个倍频器或者变频器,插入损耗较大,增加了对功率放大器增益的要求,可能会影响系统的线性度[5]。倍频器会引入相位噪声,多次倍频后相位噪声不断增大,多次变频引入谐波较多,两者都会严重影响信号质量并且增大硬件的调试难度。DDS技术可较好地弥补以上的不足,DDS是一种把一系列数字信号通过D/A转换器转换为模拟信号的合成技术,随着电子技术水平的提高,尤其是高速GaAs器件的快速发展,为DDS克服带宽限制提供了技术支持,使得DDS技术在雷达领域得到更广泛的应用[6]。DDS在相对带宽、频率转换时间、相位连续性正交输出、分辨率等指标方面远远超过了传统的频率合成技术的水平,其频率切换时间短、分辨率高、相对带宽较宽、频谱纯净、相位和频率调整灵活、输出的变频信号相位连续、易于编程控制[7-8]。

本设计综合考虑FMCW导航雷达信号的中心频率、带宽、变频时间、稳定度和准确度等因素,设计并实现了一种基于DDS技术、上变频技术、倍频技术的雷达射频前端,其具有频率范围宽、频率切换迅速且信号频率稳定度和准确度高的优点,能准确、快速、高质量发射并接收不同带宽、频率的FMCW雷达信号。

1 系统方案设计

1.1 系统技术指标

发射机主要技术指标:工作中心频率为9 350 MHz;工作带宽为75 MHz;输出功率为20 dBm;相位噪声为-95 dBc/Hz@10 kHz。

接收机主要技术指标:噪声系数5 dB;接收机灵敏度为-95 dBm;接收机动态范围>86 dB。

1.2 系统方案设计

本系统采用DDS+上变频+倍频的方案,由DDS快速产生一定带宽的高稳定度、准确度、频谱纯净的线性调频信号,经过一次上变频和一次二倍频至目标发射信号。由于大带宽的混频器成本较高,而且从DDS输出频率直接变频至目标射频频率,其对本振频率源的要求很高,频率源结构较复杂,可能引入的较大噪声、调试困难,所以本设计先将DDS产生的线性调频信号经过一次上变频至FRF/2处,再由经二倍频器将信号倍频至FRF。

接收机通常有零中频方案和超外差方案。与超外差方案相比较,零中频方案不受镜像频率影响,不需要特意选取镜像抑制滤波器,而且其结构简单、体积小、易调试、成本低,本设计选取零中频接收机方案。系统框图如图1所示。

图1 系统框图Fig.1 System block diagram

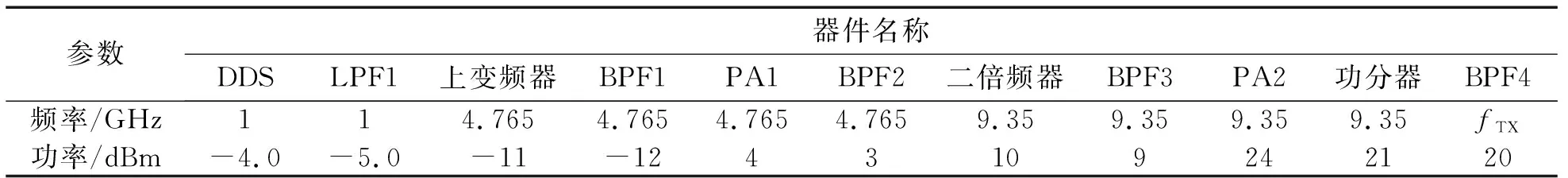

2 电路设计

表1为发射链路的相关预算分析;表2为接收链路的相关预算分析。此链路预算分析是以总体方案为依据,将系统方案框架具体化的一个预算过程,为后期器件选型做好相关参数的预算。其中,LPF1,LPF2,LPF3是低通滤波器;BPF1,BPF2是带通滤波器;BPF3,BPF4,BPF5是定制的腔体带通滤波器;PA1,PA2,PA3,PA4是功率放大器;fTX表示发射信号;fRX表示接收信号;fb表示差拍信号;fb=fTX-fRX。由于发射频率中心频点设定为9.35 GHz,则二倍频之前信号中心频率应该为4.675 GHz,又因为DDS最大输出频率为1.4 GHz,为了预留一定的余量,选择1 GHz输出,则上变频器本振端频率为3.675 GHz。考虑各部分的衰减和器件的输入输出要求,对发射信号功率进行相应放大,最终达到发射功率要求。对整个接收链路的噪声系数影响较大的是前级的器件,所以接收链路前级尽量选择噪声系数小的器件;为了充分滤除高频对差拍信号的影响,下变频之后必须用低通滤波器滤除带外干扰频率;为了方便调整差拍频率的功率,加入一个可控衰减器和2个功率放大器,根据情况调节放大倍数。

表1 发射链路预算分析

表2 接收链路预算分析

2.1 发射链路设计

DDS选用ADI公司的AD9914芯片,该芯片集成12位DAC,采用先进的DDS技术,构成数字可编程的完整高频合成器,能输出高达1.4 GHz的频率捷变模拟正弦波,且具有快速调频和精密调谐分辨率。由于DAC输出信号是以正弦信号采样的方式产生,则DAC输出信号必须过滤,以消除采样过程中的伪像以及滤波器带外的杂散。

混频器采用Mini-Circuits公司的MCA1-60LH+,该混频器变频损耗低至6.2 dB且具有1 700~6 000 MHz的工作带宽。由于混频器内部的非线性元件的作用,变频过程会产生很多谐波分量,需使用带通滤波器进行过滤,此处选择Mini-Circuits公司的BFCN-4440+,该芯片采用低温共烧陶瓷(low temperature co-fired ceramic, LTCC)技术,外形尺寸小且具有1.2的良好电压驻波比,通带损耗小于1 dB,满足目标信号选择和系统设计要求。

倍频器选用Hittite公司的HMC368LP4E,该倍频器具有较宽的输出频率范围,可输出9~16 GHz的信号频率,且具有较宽的输入功率范围,0~10 dBm均可满足要求;其还集成了2个功率放大器,输入功率达到+2 dBm时,输出功率可达+15 dBm,大大降低射频功率放大器的放大要求,简化电路设计;其相位噪声低至-140 dBc/Hz@100 kHz,一定程度上优化了发射信号的质量,且其3次谐波隔离度为18 dB,从而提高测距能力。该倍频器输出信号经过功率放大、定制腔体带通滤波器和功分器后由发射天线辐射至空中。发射链路结构图如图2所示,由控制模块通过串口配置DDS寄存器,产生1 GHz的线性调频信号,与频率为3.675 GHz的本振信号混频至4.675 GHz中频信号,经过滤波、放大、二倍频至9.35 GHz,最后进行功率放大、滤波、功分后由发射天线耦合至空中。

2.2 接收链路设计

接收链路采用的是零中频方案,任何接收机都受到噪声(外部噪声和内部噪声)的影响,降低噪声系数可提高接收机性能。外部噪声一般具有时间性、空间性和频率性,可采取一定的措施抑制或消除。而内部噪声来源于器件,不具有以上特性,其可能造成放大器饱和甚至不具放大作用[9]。所以,控制噪声系数对于接收机而言是至关重要的。接收链路多级放大器级联总噪声系数计算公式为

(1)

(1)式中:Fi(i=1,2,…,n)为噪声系数;Ai(i=1,2,…,n)为增益。根据(1)式可知,越靠近接收天线的器件对噪声系数的影响越大。为确保性能指标满足设计要求,提高接收机的灵敏度,应降低前级单元的噪声系数、减少损耗并提高增益。该接收机前级选取Hittite公司的HMC903LP3E低噪声放大器,其噪声系数低至1.7 dB,增益18 dB。

图2 发射链路结构图Fig.2 Structure diagram of the transmitter link

图3 接收链路框图Fig.3 Block diagram of the receiver link

下变频器选择Hittite的HMC220AMS8,此混频器为双平衡混频器,具有宽带高隔离特性,对偶次谐波有良好抑制作用。虽然双平衡混频器隔离度比较高,但为确保得到的差拍信号尽量不受本振端和射频端信号泄露的影响,在混频器后进行2次滤波,分别选用LFCN-6700+和LFCN-80+,2个低通滤波器,抑制泄漏和混频器产生的谐波分量。接收链路框图如图3所示,接收天线接收到雷达信号经过定制的腔体滤波器滤除带外杂波,再经过低噪声放大器进行功率放大和控制接收链路噪声系数,再与发射链路功分信号下变频至零中频,经过2级滤波、零中频放大后进行基带处理。

2.3 时钟频率源设计

时钟频率源模块主要为DDS模块提供工作参考时钟频率和为发射链路上变频模块提供本振频率,其主要由2片ADF4350芯片组成。ADF4350差分输出频率为137.5~4 400 MHz,具有良好的相位噪声性能,压控振荡器(voltage controlled oscillator, VCO)在载波为3.3 GHz处,频偏10 kHz的相位噪声为-86 dBc/Hz,频偏100 kHz的相位噪声为-110 dBc/Hz,此时钟频率源配置简单,只需要控制模块通过串口访问其内部寄存器即可完成所需配置。时钟模块的结构框图如图4所示,在有源晶振提供时钟源的情况下,控制模块通过串口配置ADF4350寄存器使其输出目标频率,再经过巴伦结构转换为单端信号输出。结构框图中的有源晶振为温补振荡器,本设计选择的是TC53-NAGIC-26 MHz,其频率温度稳定度为±1.0×106,相位噪声为-148 dBc/Hz@10 kHz;控制模块选择工业级单片机STM32F103_LQFP64;巴伦TC1-1-43A+的作用是将ADF4350产生的差分信号转换成单端信号。

图4 时钟模块结构框图Fig.4 Block diagram of the clock module

3 接收链路仿真

接收机性能指标的好坏直接影响接收信号的质量,从而影响测量的准确度,为更好地验证此设计的可实现性,此处选用ADS2012仿真软件对接收链路进行链路仿真。首先在元器件面板中选择需要的器件模型,按照实际电路设计在ADS原理图中按顺序放入滤波器、低噪声放大器(low noise amplifier, LNA)、混频器、放大器等器件并连接完整,并对选择的模型进行参数的设置,最后添加BUDGET控制器,并在标签页中进行参数设置;完成所有设置后进行仿真[10]。ADS原理图如图5所示。

图5 ADS接收链路仿真原理图Fig.5 ADS simulation schematic of the receiver link

仿真结果如图6所示,其中,图6a为接收链路噪声系数仿真结果,整个接收链路噪声系数为4.004 dB,满足设计要求;图6b为接收链路动态范围仿真结果,动态范围为-96~-24 dBm,稍低于设计指标,但基本能满足要求。

图6 接收链路仿真结果Fig.6 Simulation results of the receiver link

4 系统测试

系统测试环境如图7所示,图7a为搭建的“阵列天线+射频收发前端”系统测试平台,图7b为收发天线,测试地点位于实验室楼顶,测试目标墙面与收发天线的水平距离约为37 m。图8为射频收发硬件系统实物图。

4.1 发射链路测试

发射链路主要由DDS输出线性调频信号经过上变频、二倍频、功率放大和功分器功分至射频发射信号,主要对DDS输出中心频率为1 GHz的线性调频信号和射频发射中心频率为9.35 GHz的目标信号进行测试。

4.1.1 DDS输出信号测试

将AD9914设置为数字斜坡调制模式,在时钟模块1提供的3.5 GHz参考频率下输出1 GHz线性调频信号,如图9所示,DDS输出信号中心频率为1 GHz,带宽为20 MHz,输出功率值为-4.099 dBm。

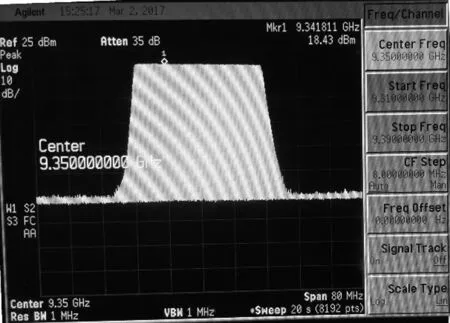

4.1.2 发射信号测试

DDS输出1 GHz的线性调频信号与时钟模块2提供的3 675 MHz的本振信号进行上变频得到4 625 MHz的信号,此信号经过二倍频、功率放大、带通滤波以及功分器功分后得到目标发射信号。本次测试带宽为30 MHz,中心频点为9.35 GHz,发射功率为18.43 dBm。实测发射信号频谱图如图10所示,从图10可以看出信号稳定性较好。

图10 发射信号测试图Fig.10 Test chart of the transmitter signal

为了更好地验证此系统的性能,对发射信号进行相位噪声测试,分别测试9 300 MHz和9 280 MHz处的相位噪声,如图11所示。

图11 发射信号相位噪声测试图Fig.11 Phase noise test chart of the transmitter signal

通过计算可以得到这2处的相位噪声为-89.3 dBc/Hz@10 KHz和-89.4 dBc/Hz@10 KHz,稍低于设计理论值,但基本满足设计需求。

4.2 接收链路测试

接收链路测试主要对差拍信号测试。由于测试环境的局限性,测试目标距离较近,需要增大距离分辨率,则将发射信号带宽设置为80 MHz。图12是根据导出数据,利用Matlab绘制出的差拍信号频谱图,从频谱图可以看出目标差拍频率为16.92 KHz,根据距离计算公式(2)计算结果可知,测试值与目标实际距离吻合。从测试结果看出此雷达系统具有较高的稳定性和测距精度。

38.07

(2)

(2)式中:R为目标距离;fb为差拍频率;c为光速;T为扫频时间;B为测试信号带宽。

图12 差拍信号频谱图Fig.12 Spectrogram of the beat signal

5 结束语

从实际的需求出发,本文采用“DDS技术+上变频技术+倍频技术”的发射机方案和零中频接收机方案设计出一种线性调频连续波导航雷达射频前端。有效地利用了DDS频率切换时间短、分辨率高、相对带宽较宽、相位和频率调整灵活、输出的变频信号相位连续、易于编程控制等优点,实现了高稳定性和高准确度地发射信号,并精确地接收到回波信号。实测结果表明,此设计基本满足线性调频连续波雷达的基本设计要求,从而验证了此方案的正确性和合理性。