运动位置传感器信号实时解析与控制系统设计*

阮玮琪,贾文红,郑丽芳,李 瑞

(1.中国科学院上海应用物理研究所,上海 201204;2.中国科学院大学,北京 100049)

同步辐射光束线站运动控制系统是通过调节狭缝、单色器、聚焦镜箱等光学设备上的高精度步进电机,为用户实验提供有能量、光斑、通量要求的同步辐射光[1-2]。储存环高频系统的电磁干扰,地面振动、水冷和液氮冷却系统引起的机械振动及电噪声等,致使高精度运动位置传感信号伴随有复杂电磁噪声背景。随着同步辐射实验技术的发展,上海光源要求联动地控制多个设备、实时调节多个物理量以及实时触发并采集多路实验数据。

本文设计的多路运动位置传感器信号实时解析与控制系统的三大基本要求是:①处理并行多路信号[3];②提取强噪声背景下信号[4];③实时解析高精度传感信号[5]。模拟电路系统的噪声滤除率不高,且由于电阻、电容与电感的值在各自的精度范围内波动,其组成的多路模拟滤波电路对于多路信号易产生不一致延迟。传统的数字电路系统,通过并联多个位置信号解析芯片产生控制信号,由于芯片内部固定,适应性差,在特定噪声下无法解析信号,而且芯片间信号延迟不确定,不具有实时性。本文设计的运动位置传感器信号实时解析与控制系统,通过数字采样、基于线性反馈移位寄存器LFSR(Linear Feedback Shift Register)的数字滤波[6]、矫正识别计数及冗余计数的方法,结合可编程逻辑门阵列芯片FPGA(Field Programmable Gate Array),在复杂噪声背景下,实现并行多路运动位置传感信号的实时解析及控制信号的实时输出。相比于模拟电路与传统数字电路实现方式,系统实时性更好、并行集成度更高。

1 系统设计

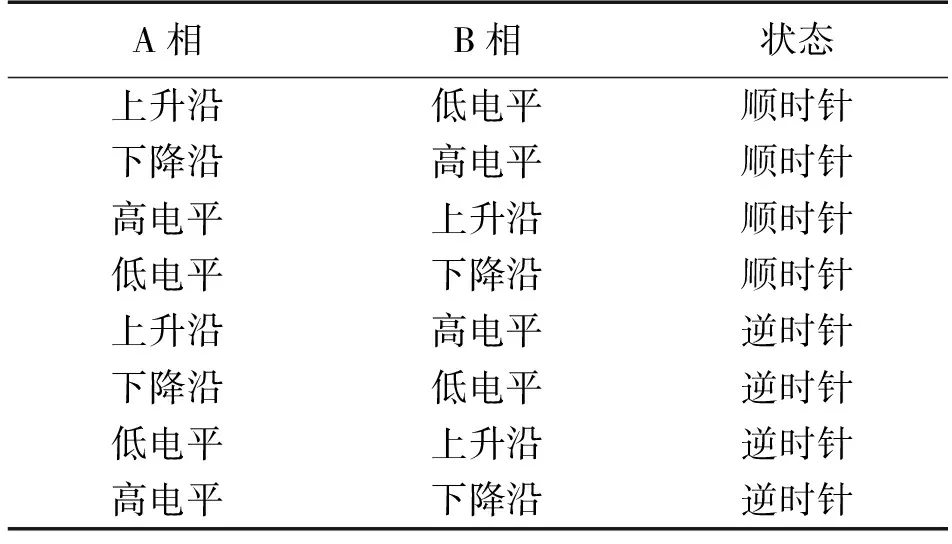

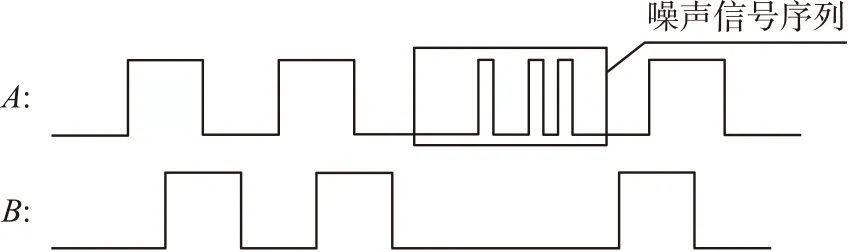

本系统输入的运动位置信号由德国Heidenhain公司RPN 886型超高精密编码传感器与IBV 660B型细分转换器组成的运动编码传感系统[7]产生。RPN 886编码传感器主要结构为环绕于直径200 mm圆盘上的圆形带状光栅,内刻有7 200万道光栅刻痕,刻痕间距为8 nm~9 nm。IBV 660B转换器最高输出方波频率为2.5 MHz,最高编码分辨率为0.087 2 μrad。RPN 886传感器每转动一周,IBV 660B转换器将产生7 200万个周期方波。编码系统产生的运动位置传感信号为实时正交差分信号(下称原信号S(t)),通过等长度信号通道输入实时解析与控制系统中。如图1 所示,C1与C2为输入的两路外界背景噪声,C3与C4为4路差分信号合成后的AB两相正交信号。图中方框区域内,可以明显地观察到噪声信号N(t)对运动位置传感信号S(t)的影响,主要表现为S(t)上升沿、下降沿以及高低电平处出现jitter类型抖动[8]。本质上是能量较小的噪声信号作用于能量较大的原信号改变后者电平状态。

图1 输入正交差分运动位置传感信号

图2 运动位置传感器信号实时解析与控制系统

系统结构如图2所示,正交差分运动位置传感信号S(t)与噪声N(t)耦合的输入信号H(t)依次经过差分与单端信号转换、数字信号采样、基于线性反馈移位寄存器LFSR的数字滤波、矫正识别计数、冗余计数、信号计数触发过程,系统输出实时的触发控制信号C(t),其中信号计数是实时的。

2 系统实现方法

强噪声信号对原信号影响较大,系统需要通过不同的方法实时提取与解析有用的运动位置传感信号,并实时输出触发控制信号。

2.1 数字采样与滤波

如图3所示,为达到并行多路信号同步的目标,在FPGA芯片内部,系统采用同一采样时钟Sampling Clock及系统时钟System Clock,滤波时钟Filter Clock可等效看作同一时钟源计数分频得到。通过调用Xilinx公司可编程原语IBUFDS,输入的差分信号H(t)直接转换为单端信号,再经Flip-Flop触发器的数字采样以滤除高频噪声信号。Flip-Flop触发器由输入采样时钟Sampling Clock控制,高于采样频率Sampling Clock的噪声被滤除。这一过程可表述如下:

图3 多通道数字采样与滤波

(1)

h(n)=H(nTsampling)=S(nTsampling)+N(nTsampling),n≥0

(2)

式中:S(t)表示原始正交信号,N(t)表示噪声信号,Tsampling为采样时钟周期,h(n)表示经过采样后的数字信号序列。h(n)与H(t)电压幅值都被归一化。

数字信号序列h(n)输入由3级串联D触发器、1级 JK触发器及门电路组成的基于线性反馈移位寄存器LFSR的数字滤波电路[9]。滤波电路只允许3个及以上连续滤波时钟Filter Clock上升沿时刻都为同一个值的信号序列h(n)经过,最终滤波时钟Filter Clock的3个上升沿之间的噪声尖峰被滤除,因此允许输入50%占空比的信号序列的频率为滤波时钟频率的六分之一。在系统实现时,系统时钟System Clock与采样时钟Sampling Clock相同,滤波时钟Filter Clock与采样时钟Sampling Clock的初始相位一致,滤波时钟周期Tfilter是采样时钟周期Tsampling的整数α倍。这有利于控制α值以调整不同通道的数字滤波器带宽,同时也兼顾更高的采样和系统时钟频率以及更窄的滤波器通带。α取值过大可致使原信号S(t)采样失真,发生信号重叠而无法计数,取值太小可导致较多频带的噪声信号N(t)输入,增大系统误差率,所以α取值的上限与下限由原信号频率与噪声信号频率以及它们的占空比决定,可表示为

Tfilter=αTsampling=αTsystem

(3)

(4)

式中:当输入系统的方波信号占空比减小时,式(4)中等效信号频率相应增大,即fsignal增大。

3级D触发器每一级延迟时间为Tfilter,h(n)经过各级D触发器输出的信号分别定义为Q[1](n)、Q[2](n)、Q[3](n),表示如下

Q[1](n)=h(n-α)=H(nTsampling-Tfilter)

(5)

Q[2](n) =Q[1](n-α)=h(n-2α)

=H(nTsampling-2Tfilter)

(6)

Q[3](n)=Q[2](n-α)=h(n-3α)

=H(nTsampling-3Tfilter)

(7)

Q[1](n)、Q[2](n)、Q[3](n)经过与门及或非门后输入到JK触发器,而后其输出的信号序列JK(n)连接到后续计数电路。图中多级并联通道电路与通道一Channel 1电路保持一致,都可用同一通道公式表示,只是α取值不一致。JK触发器处理信号过程可表示为

J(n)=Q[1](n)&Q[2](n)&Q[3](n)

(8)

K(n)=Q[1](n)+Q[2](n)+Q[3](n)

(9)

JK(n)=J(n)&JK(n-1)+K(n)&JK(n-1)

(10)

式(10)中:JK(n-1)表示JK触发器前一时刻状态。

至此,系统对输入信号H(t)进行数字采样与数字滤波后,单通道总延迟时间Tdelay是5级串联触发器延迟时间的和,可表示为

Tdelay=Tsampling+3Tfilter+Tsystem=(3α+2)Tsampling

(11)

为实现多通道并行处理的要求,系统采取不同通道不同α值的策略。系统所有m通道总延迟可表述为所有单通道延迟的组合向量tdelay,即

(12)

tdelay=Ac1

(13)

2.2 矫正识别计数

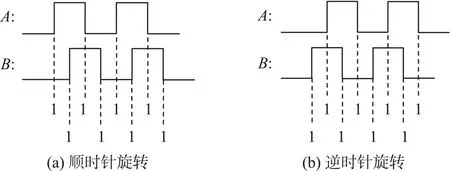

系统通过矫正识别[10]的数学方法识别原信号S(t),并对S(t)进行有效计数,而冗余计数[11]方式则可以大幅提高计数准确度。如表1所示,由于编码器输出A、B两路信号正交,A信号和B信号上升沿、下降沿、高电平、低电平的8种组合表示编码器顺时针或者逆时针旋转一个刻度。编码传感器旋转一周产生7 200万个A、B正交信号并产生1个Z信号脉冲。实际工作环境下编码器运动角度小于π/6且AB信号计数至少在几十万后才产生一个Z信号,因此A、B信号序列的精确识别与计数极为重要。

表1 正交编码器信号

图4 运动位置传感信号抖动识别与矫正

识别与矫正计数用于剔除运动位置传感信号中混和的抖动噪声,图4所示为运动位置编码传感器顺时针旋转产生的两路正交信号,方框内噪声信号表现为jitter抖动特征。系统首先识别A信号上升沿与B信号低电平,增加计数值,而后如果检测到A信号下降沿与B信号高电平,则再次增加计数器值,但是若检测到A信号下降沿与B信号低电平,说明此时检测到噪声信号,则计数器值减一。若系统接收到Z信号高电平脉冲,则自动矫正计数值。本质上,通过判别信号特征,系统识别区分正交信号与噪声信号,并自动矫正计数值。系统用于识别与矫正的时钟为系统时钟System Clock。至此,系统单通道总延迟Tdelayall与总延迟向量tdelayall表示为

Tdelayall=Tdelay+Tsystem=(3α+3)Tsampling

(14)

tdelayall=Ac2

(15)

式中:tdelayall=[Tdelayall(1)…Tdelayall(m)]T表示m通道总延迟向量,c2=Tsampling[1 3 2]T表示所有通道状态向量,转移矩阵A(α矩阵)依然保持不变。

2.3 冗余计数

系统采用如图5所示的运动位置传感信号边沿与电平双识别计数方式作为冗余计数方式。理论上,输入混合有噪声的编码器信号H(t)在经过上述数字采样、数字滤波以及矫正识别后,计数误差仅来源于与编码信号特征一致的噪声信号。根据表1所述的8种顺时针与逆时针旋转的A、B信号序列状态,图5(a)与图5(b)分别描述的顺时针旋转编码器信号与逆时针旋转编码器信号的计数方式,系统对每一个编码器旋转刻度计数4次以降低噪声信号序列所带来的误差,误差值减少4倍。

图5 运动位置传感信号边沿与电平双识别计数

2.4 信号触发与输出

系统各通道计数值与电脑上位机通过串口输入FPGA中的判别值进行比较,当通道的计数值达到判别值后,系统输出上升沿触发信号以控制外部传感器采样。这一判断行为在FPGA中采用组合逻辑电路实现,其延迟时间为一个ps级别的门电路延迟,不计入系统总的延迟时间内。系统输出触发控制信号具有高实时性。

图6 系统FPGA数字信号处理板

3 实验结果

系统采用如图6所示的FPGA高速信号处理板,其芯片采用Xilinx公司XC7K325T-3FFG900C型号FPGA,具有30万以上等效逻辑资源且能运行高频率时钟,满足多通道信号同步实时处理的要求。滤波时钟与系统时钟取400 MHz,即Tsampling与Tsystem都为2.5 ns。

本实验系统的运动装置采用PK266DB步进电机与传动比为10 000的传动装置,最小运动角度为3.14 μrad,编码系统使用分辨率为0.087 2 μrad的RPN 886编码器与IBV 660B细分器,最小步进角度对应编码系统36个计数值,运动装置每1.44 ms控制步进3.14 μrad以控制编码信号频率为25 kHz。由式(4)知α必须小于2 666,为防止输入系统的信号占空比小于50%,最终α取值为250。噪声信号N(t)由信号发生器产生并耦合到输入信号通道上。

传感信号解析结果如表2所示,信噪比由1∶0.5提升至1∶1后,系统误差值增大。在运动角度大于9 420 μrad情况下,当信噪比为1∶0.5时,系统的误差稳定在0.04%左右,信噪比为1∶1时,系统误差稳定在0.05%左右。这是因为当运动角度较大时,随着运动角度的增加,运动位置传感信号S(t)以及噪声信号N(t)的作用时间同步成比例增加,误差计数值与理论计数值都同比例增加,导致误差值恒定。而当运动角度减小到9 420 μrad以下时,系统误差随运动角度减小明显增大。因为在控制运动角度较小时步进电机实际响应角度小,且系统容易受到其他静态误差及输入噪声影响,误差值增大。理论上,高精度实验系统会导致实际计数值在理论计数值上下抖动,而表2中实际计数值都比理论计数值大,说明系统除噪声信号N(t)外,还受到静态误差影响。

表2 运动位置传感信号计数解析结果

实验系统不变,研究不同α取值下的编码器信号频率与系统平均误差的关系,如图7所示,此时信噪比取1∶1,运动角度为9 420 μrad至15 700 μrad间。实验系统通过控制步进电机运动速度改变运动位置传感信号频率,正常工作频率在25 kHz至800 kHz,极限频率在800 kHz至1.2 MHz。根据式(4)并作10倍余量后计算得到α值,采用10倍余量主要是为防止信号占空比失真(小于50%)。

由图7可知,当编码信号频率为25 kHz至800 kHz时,α取值介于8~11间的系统误差小于0.05%。而当频率25 kHz至1.2 MHz时,α介于8~250间的系统整体误差小于0.5%。α小于8时,由式(4)可知系统噪声滤除率较低,误差率明显高于0.05%且一直浮动。说明不同频率下,α取值的窗口不同,编码器输出信号S(t)频率越高α取值窗口越小。

系统实时解析频率为100 kHz的混有噪声的正交信号S(t)。由示波器测得输入正交信号S(t)与实时输出数字信号序列JK(n)的延迟差[12]如表3所示。不同α取值下,系统实际延迟时间比式(15)表述的理论延迟时间多3 ns左右,这主要为测量延时及信号通道静态延时。实验表明信号通道延迟时间固定且可预测,系统具有实时性。

表3 系统延迟时间测量结果

4 结语

本文阐述一种运动位置传感器信号实时解析与控制系统的设计与实现方法。系统创新地采用基于线性移位反馈寄存器LFSR的并行多路可控数字滤波器,灵活调节它们的通带频率以适应多路高精密运动位置编码传感器信号的实时解析,通过矫正识别及冗余计数方式区分噪声信号与有效信号并有效降低计数误差。实验测试表明,系统实现了并行多路、强噪声背景下信号提取、信号实时解析与控制的三大目标。信噪比为1∶1环境下,系统能并行检测多路运动位置传感器信号,且α介于8~250间的系统整体误差小于0.5%;对频率在25 kHz至800 kHz的位置传感信号,α介于8~11间的系统误差小于0.05%。各单通道信号的解析时间与α成正比,为(3α+3)Tsampling,系统具有实时性。