一种分布式电力电子环网拓扑及时钟同步算法

刘杨洋,苏建徽

(1.合肥工业大学 电气与自动化工程学院,合肥 230009; 2.教育部光伏系统工程研究中心,合肥 230009)

0 引 言

目前大多数电力电子系统,其控制部分往往采用中央集中式控制,这种控制方式使得系统不具备模块化功能,大量内部连接线导致系统可靠性与维护性差,控制与通讯复杂[1-2]。因此在中、大功率电力电子系统设备中,可以采用基于以太环网的分布式电力电子控制,即可以实现电力电子模块标准化[3-5],提高通用性,同时通信结构简单易维护,大幅度改善了电力电子系统的可靠性。

如在大容量的多相变频器以及电力电子变压器系统中,若是采用传统的集中式控制结构,每一个控制单元均需单独与主控芯片连接,传输采样、驱动等信号,存在大量点对点电气连接线,同时对处理单元提出较高要求。而如果采用基于环网的分布式电力电子控制,仅需将各个模块,如单个H桥之间单独连线,大大简化了系统,减少了点对点连接线,增加系统可靠性。

由于环网拓扑中各个站点位置不同,以及网络固有存在的网络延时问题,必须对系统中各个站点的时钟进行同步,否则无法满足控制算法的实时性要求。为实现分布式系统中的时钟同步,近年来国内外很多学者进行了分析研究。文献[6-7]采用绝对时钟同步,即把外部时间基准引入分布式系统,如利用全球定位系统(GPS)进行授时,这种时钟同步方式需要设备添加专用接收装置,而且需要单独的接线,应用较为简单但成本较高,而且因为无线传输等限制,同步精度不高,仅为亚毫秒级,基本无法应用在分布式电力电子控制场合。文献[8-10]使用IEEE1588精密时钟同步标准对系统进行同步,主要利用以太网及其他支持多播技术的网络使各个终端时钟同步,时钟同步精度达到亚微秒级[7],可以满足微电网中测量、控制设备的要求,对于分布式电力电子系统,如模块化多电平换流器,电力电子变压器等控制场合,同步精度略显不足。文献[11-12]中将EtherCAT工业以太网技术应用在分布式电力电子系统中,支持多种拓扑结构,传输速率快,同步精度高。但此种方法成本很高,需使用昂贵的专用设备,而且由于EtherCAT系统中主站采用Windows等非实时系统,相对于各个从站的时钟同步精度,主站的实时性不高,这限制了部分应用。文献[13-14]提出了一种新颖的高速可切换式光纤环网拓扑,可以省略环网通讯中的转发步骤,达到很高的时钟同步精度,而且实现了十五相推进变频器的分布式控制,但其时钟同步算法是以各个站点之间等间距且此延时精确可测量为前提,因此只能适用于专用系统中,对于普通电力电子系统,各个站点之间线路长度可能不同,上述拓扑与方法便不能使用。

鉴于上文所述,针对分布式电力电子中时钟同步的需求,提出了一种基于以太网的环网拓扑,以及简便易行的时钟同步算法,可以实现分布式系统中全部站点的通讯与时钟同步功能,并搭建了通用分布式电力电子控制平台,验证了所提拓扑及时钟同步算法的可行性。

1 控制平台拓扑与基本功能

在大型电力电子系统中,要实现分布式控制,既要实现对所有站点的时钟进行精确同步,也要实现主站和下属从站间的信息交互,包括主控制器向下属从控制器发送数据及控制命令,以及从控制器向主控制器或其他从控制器发送数据。所提出的同步控制方案,一方面可以实现系统中所有站点都时钟同步,方便主站直接向其他从站发送包含时间信息的控制指令,另一方面,提高了时钟同步精度。

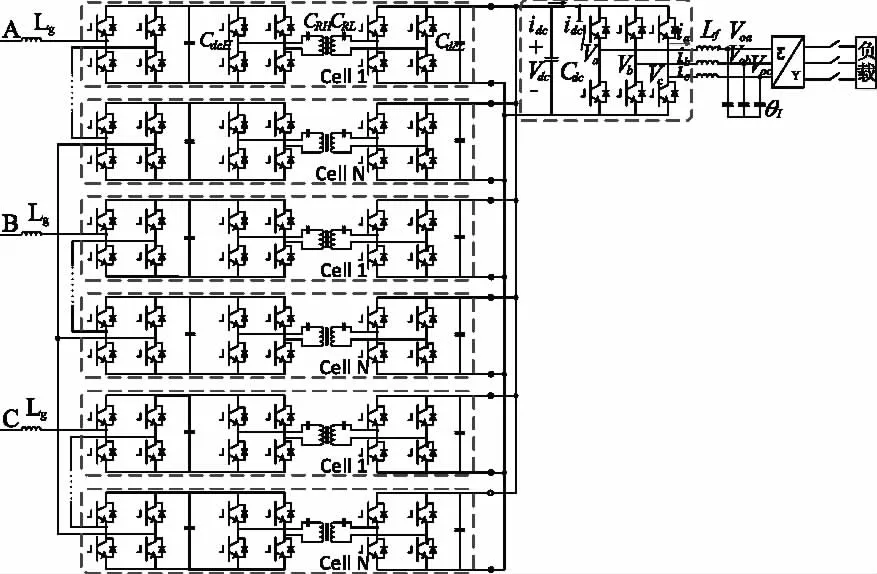

为方便大型系统的控制,可以采用系统集成技术,将一个电力电子控制系统分成多个标准模块,每个模块都包含功率器件和控制部分,以模块为单位组成分布式电力电子系统。图1中的电力电子变压器系统,可以把每个虚线框中的部分分成单位模块[15-17],每个模块单独控制,并互相通讯以协调工作,满足整体系统功能。

图1 电力电子变压器主电路拓扑

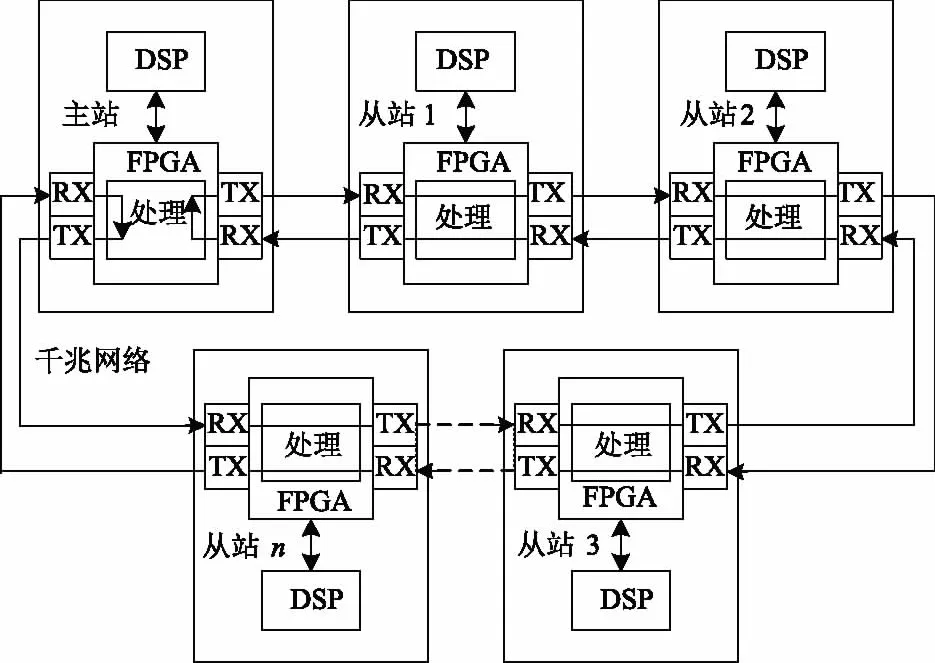

分布式电力电子系统的高速通信及同步控制的结构如图2所示。该控制拓扑由单个主站和若干个从站组成,每一个站点对应即控制系统中的单个模块。

图2 分布式环网拓扑

在此系统中,主站和从站的硬件架构相同,包括主站在内的所有站点都对应分布式电力电子系统中的节点,每个节点都有一个站点进行控制。站点主要由负责控制算法和保护的DSP,负责高速通讯及时钟同步算法的FPGA以及相关外围电路组成。高性能的DSP主要负责具体电力电子控制算法,包括ADC采样、PWM输出、故障保护等功能,而高密度的FPGA主要负责各站点间高速通讯,执行时钟同步算法,使DSP处理器实现同步动作等。网络物理层芯片和连接线均支持千兆网络标准,物理层芯片与FPGA处理器使用同一晶振提供输入时钟。

2 时钟同步算法

提出的时钟同步方案分为两部分:进行时间戳的传输延时测量和时钟初始偏移补偿的全同步过程,以及补偿时钟偏移以进一步提高时钟同步精度的自同步过程。

分布式系统中各个站点间时钟的误差,主要包括时钟初始偏差,线路传输延时,晶振漂移误差,以太网转发误差。时钟初始位置的偏差主要因为各个站点通电时刻不同,使时钟开始计时的时刻不同,同一时刻的各站点时钟的值存在初始偏差;各站点在拓扑中所处位置不同,因此与参考时钟间存在不同的线路传输延时;各个站点的时钟由板载晶振倍频而得,因此由于晶振固有的漂移特性,各个时钟间同时存在动态的误差;以太网转发误差主要受以太网物理层和数据链路层对传输时延的影响。

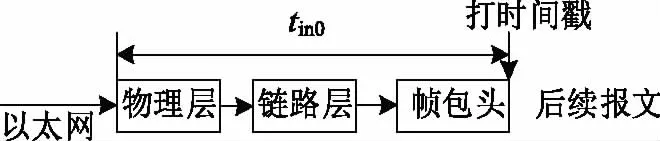

在IEC 61850协议中,将记录报文到达或离开同步设备的时刻,称为打时间戳,打时间戳的位置对同步精度有较大的影响。在一个完整的时钟同步过程中,将打时间戳的位置定为各站点接收完时钟同步报文帧包头的时刻,以确保站点开始接收报文到打时间戳的时间固定,以免产生误差。考虑到报文在传输中,经过物理层与数据链路层的时间无法测量,因此在所提出的时钟同步方案中,所有报文长度相同,可以确保传输过程中经过物理层与数据链路层的时间保持一致,因此报文开始进入物理层到打时间戳的时间为恒定值tin0,如图3所示;同时各个站点处理报文的过程保持相同,以确保报文在FPGA中的处理时间相同。

图3 打时间戳示意图

因此可以认为,同步报文经过站点的时间,包括报文两次从不同端口进入站点内部又发出的时间固定,且全部相等,设为固定值tin。

2.1 全同步过程算法

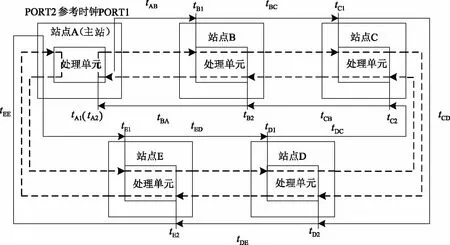

下面所述的算法主要对时钟初始偏差和线路传输延时进行补偿。在时钟同步报文循环传输过程中,各个站点在打时间戳时记录报文两次到达本站的时刻,各个从站根据本地记录的时刻及接收到的主站时刻,计算出从站与主站的时钟延时。如图4所示,以具有5个站点,即1主站、4从站的分布式电力电子控制系统为例,分析了具体的时钟同步算法中的全同步过程,以主站时钟为参考时钟,各个从站都和主站同步。

其中tX1和tX2表示站点X第一次和第二次打时间戳时记录的时刻,对于各个从站,tX1和tX2为时钟同步报文先后两次进入站点的时刻,对于主站,则表示报文两次从端口1(PORT1)端口接收到的时刻。tAB表示A站点首次打时间戳到B站点首次打时间戳之间经过的时间,tBA表示B站点第二次打时间戳到A站点第二次打时间戳之间经过的时间,其他同理。tEE表示E站点首次打时间戳到第二次打时间戳之间经过的时间。假设A站点首次打时间戳时各个站点X的时刻为tX0,则A站点与B站点间时钟的偏差即等于tA0与tB0的差值ΔtX。

在同步过程中,主站首先发送预同步指令,经各从站转发后经主站即站点A的端口2(PORT2),再经过各从站,回到主站,此时主站第一次打时间戳,记录时刻tA1。随后主站的同步报文向从站发送,第一次经过各个从站时,从站打时间戳,得到tB1、tC1等时刻,这个报文进入主站端口2重新经过各个从站时,从站第二次打时间戳,得到tB2、tC2等时刻,报文返回主站端口1时,主站第2次打时间戳,记录下时刻tA2。随后主站便下发含有主站时间戳信息的同步报文,各个从站根据主站与从站记录的时间戳信息,计算本地时钟与主站时钟的偏差,算法如下。

图4 时钟同步过程

因为tAB与tBA等都等于AB间线路传输时间与单次站点转发时间tin之和,AB间线路长度固定,tin也保持恒定,所以有:

tAB=tBA

(1)

同理有:

tBC=tCB

(2)

tCD=tDC

(3)

tDE=tED

(4)

由图中时间戳可得:

tE2-tE1=tEE

(5)

tD2-tD1=tEE+tDE+tED=2tDE+tEE

(6)

同理有:

tC2-tC1=2tDE+tCD+tEE

(7)

tB2-tB1=2tDE+tCD+tBC+tEE

(8)

tA2-tA1=2tDE+tCD+tBC+tAB+tEE

(9)

由上式可得各个从站与主站A间传输延时:

(10)

tAC=tAB+tBC

(11)

tAD=tAB+tBC+tCD

(12)

tAE=tAB+tBC+tCD+tDE

(13)

又由于:

tB0=tB1-tAB

(14)

代入上列各式可得站点B时钟与参考时钟间偏差:

ΔtB=tA0-tB0=tA1-tB1+tAB

(15)

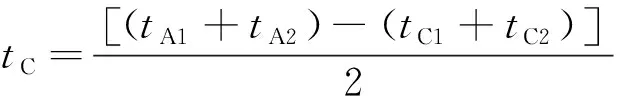

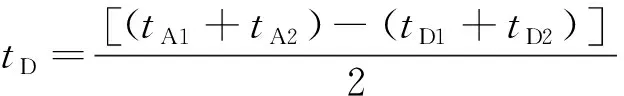

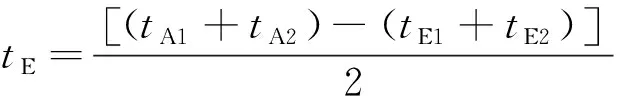

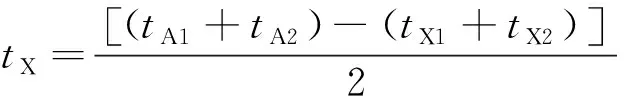

同理可得其他站点时钟与参考时钟间偏差:

(16)

(17)

(18)

因此可知任意站点X的时钟与主站参考时钟的偏差ΔtX可用主站及本站累计四次打时间戳所得时刻计算出:

(19)

2.2 自同步过程

晶振的频率与标称频率不可避免地存在误差,随着设备工作时间增加,多个晶振之间存在的静差不断改变,使前述全同步过程中的同步结果失效。自同步过程可以预先补偿各个站点晶振之间存在的漂移。

当系统的全同步过程完成后,每个站点计算得出本站时钟与主站参考时钟的偏差ΔtX,在不考虑晶振相对漂移的影响下,理论上ΔtX经过一次全同步补偿之后变为0,即一次全同步后所有时钟保持同步。而实际上各个站点的时钟间偏差不断拉大,单位时间t内增大的偏差值Δt0就为两个晶振漂移的相对值。在不考虑晶振频率随温度变化的情况下,晶振频率相对保持不变,因此两个晶振间频率漂移方向不变,可以使用上一同步周期测得的误差增长值预估下一周期晶振相对偏移量,即使用这一次全同步周期计算得到的Δt0来估算下单个周期的Δt0。

具体方法是:假设一次全同步周期为T,将上一周期的Δt0平均分为n等份,在全同步周期内分n次均匀地补偿到从站时钟上。

由于自同步过程预先考虑到本同步周期内晶振的漂移,因此在下一个周期的全同步过程中,所需补偿的偏差会大大减小,经过几次自同步过程后,全同步所计算出的本站时钟与主站参考时钟的偏差ΔtX趋向于零,达到类似锁相环的效果。而且自同步过程仅在本站运行,无需占用通讯资源,适当提高自同步的频率,即把Δt0分为更多等份,可以使自同步过程更加均匀,提高时钟同步精度。

3 实验结果与分析

为验证上述时钟同步算法,搭建了分布式电力电子通讯控制平台,采用了DSP芯片TMS-320F28335与FPGA芯片XC6SLX45作为控制器,以1台主站与4台从站的结构组成环网以自定协议通讯,测量了系统时钟同步的精度。

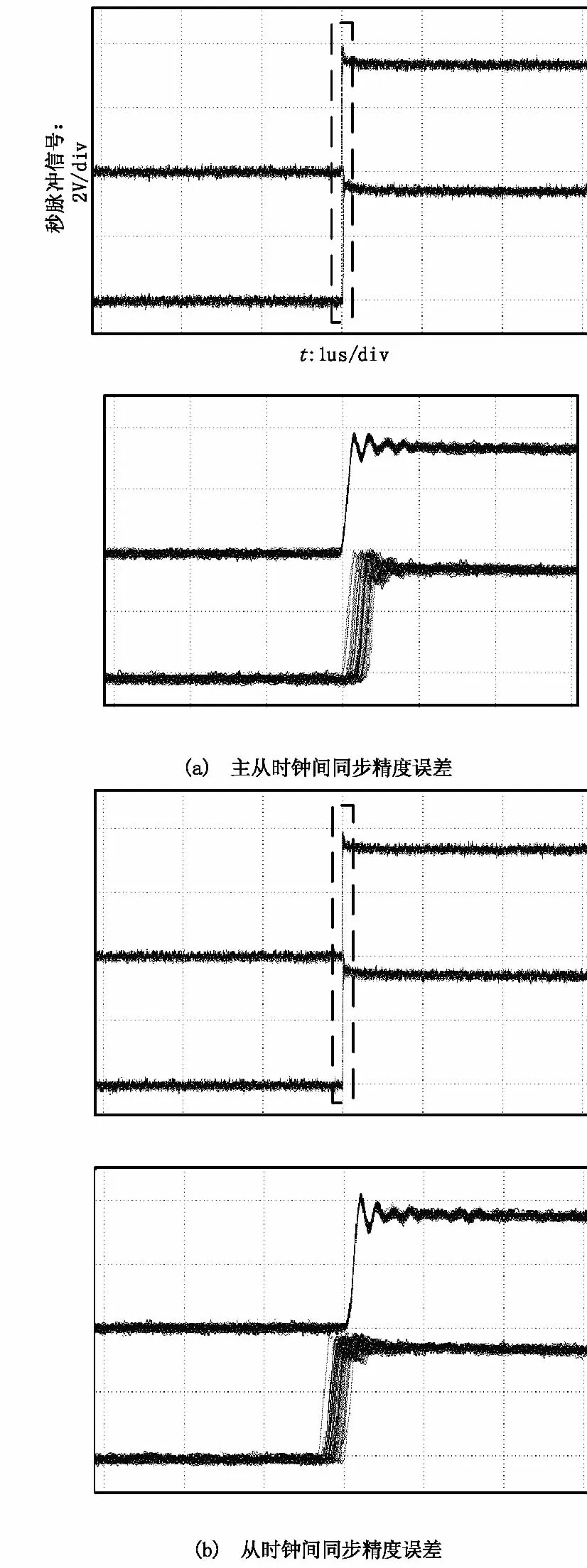

图5 实验结果

主站每隔0.01 s(可设置)开始一次全同步过程,待经过几次全同步过程后,加入自同步。主站与从站发送自身时钟的秒脉冲信号至示波器,通过比较各个脉冲信号上升沿的时间差,可以精确地测量出各个站点时钟间的误差。下面的波形分别为比较1 s之内主站与从站、从站与从站间时钟秒脉冲信号上升沿。实验结果如图4所示,在图5各子图中,下面的波形即是秒脉冲信号在虚线框内的局部放大图。可见主从站时钟间同步误差在1秒时间范围内最多约为15 ns,从站间同步误差在1秒时间范围内约为12 ns。

对比以上实验结果可以看出,经过时钟同步后,系统内的时钟同步精度达到15 ns以内,验证了所提出的时钟同步方案在实际应用中具备较高的时钟同步精度。

实验验证发现时钟同步的结果中,仍存在一定范围的偏差,而且存在抖动,经分析主要存在以下两方面原因:

(1) 自同步过程中中忽略了晶振温度漂移的影响,假设单个晶振频率不变,因此多个晶振间相对漂移速度基本不变。现实中即使环境温度基本恒定,网络芯片与处理芯片的工作状态改变也会引起晶振温度变化,从而改变晶振相对漂移速度,影响自同步的效果;

(2) 由于FPGA在实际工作中存在最小的时钟周期,对于相差一个时钟周期内的误差无法检测到,因此同步精度无法小于单位周期。

因此在实际工程中,对高精度晶振采取温度补偿措施,以及在可能的范围内,提高FPGA的时钟工作频率。采取以上的做法可以进一步改善时钟同步精度。

4 结束语

在大容量的复杂电力电子系统中,基于高速以太环网的分布式控制可以减少电气连接线、降低系统复杂度、增加可靠性。而各个站点间的时钟同步是实现分布式控制的前提。所提出的基于高速以太网络的环网拓扑,简便实用的时钟同步算法,与现有诸多方案相比,有如下优势和特点:头尾相连的环网拓扑,可以实现包括主站在内的所有站点的时钟同步;站点之间线路长度无需相等,可以灵活配置系统中站点位置;使用FPGA控制高速通讯,实时性强;各个站点硬件相同,主站从站仅软件程序不同,与EtherCAT等工业以太网应用相比,成本较低。

使用所提出的拓扑与算法搭建的通用控制平台,经实验验证具有较好的时钟同步精度,可以用于电力电子系统的分布式控制中,可以满足实际分布式控制工程应用中的时钟同步需求。