基于FPGA的NAND Flash ECC校验系统设计与实现

王 轩,常 亮,李 杰

(1.中国科学院上海微系统与信息技术研究所,上海200050;2.上海微小卫星工程中心上海201203;3.上海科技大学信息学院,上海201210;4.中国科学院大学北京100049)

随着嵌入式技术的发展,各类移动设备已广泛应用在各个领域。在人们对高速化,续航能力,高可靠性上取得进展的同时,也对其中的存储设备提出越来越高的要求[1]。NAND Flash设备具有的掉电非易失性,存取速度快,低功耗,抗震性等优点[2],已广泛取代传统磁介质存储设备,成为嵌入式设备中解决高密度存储的主流方案[3]。

由于NAND Flash工艺无法保证数据存储的可靠性,且考虑星载设备工作在空间环境的恶劣性,可能会导致单粒子事件造成其存储数据在某些位发生反转[4]。虽然出现这种情况的概率较低,通常只有一位或几位。不过对于重要的数据仍需采用必要的检错纠错机制来提高可靠性[5]。

基于汉明码的ECC(Error Correction Code)校验算法可纠正一位错误,检测两位错误,对多于两位的错误则无法保证纠错和检错[6]。由于其便于硬件实现,计算速度快,具有实时性等优点,非常适用于NAND Flash存储校验。文中将介绍ECC算法的设计及基于FPGA的硬件实现,具有1bit/4kbits的纠错能力,经Modelsim仿真及烧入Microsemi公司的Smartfusion2系列FPGA中调试验证算法在系统中可稳定运行,满足设计要求。

1 ECC校验算法原理

ECC校验由传统的奇偶校验发展而来,改进了传统奇偶校验仅能检错而无法纠错的局限性。并且传统的奇偶校验冗余数据随原始数据的增长而线性增长。而ECC校验算法将原始数据划分为矩阵的形式,通过对数据的组合行列校验产生,一般将512字节分为一组,每组(521 bytes=4096 bits=2n,n=12)的原始数据需产生24bits(2n,n=12)的ECC码,冗余编码数据为2logm2(其中m为原始数据的位数),随原始数据成对数形式增长。当然也可以根据需要,将较少的数据分为一组,增加组数和冗余码来来增强纠错能力。

1.1 ECC编码

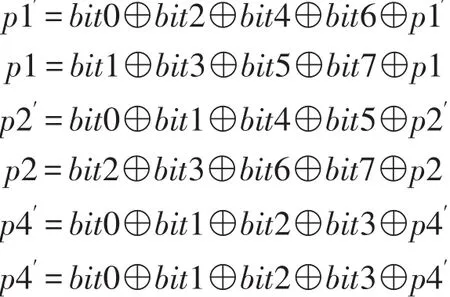

本设计中采用将512字节数据划分为一组进行ECC的编码。当然具体编码方式如图1所示[7]。

其中p1-p4为列校验码,由这512字节的所有对应位通过异或运算产生。用数学表达式表示为:

图1 ECC编码方式

p8-p2048为行校验码,由图1中对应字节的所有位通过异或产生。可用数学表达式表示为:

其中rownumber为行数的二进制表示形式。其第零位可区分出奇数与偶数行,第一位可将数据的行数分为每两行一组,对每两行的奇偶进行区分,类似的方式可对行数进行不同的分组,从而得到其他行校验码。

1.2 根据编码进行检错与纠错

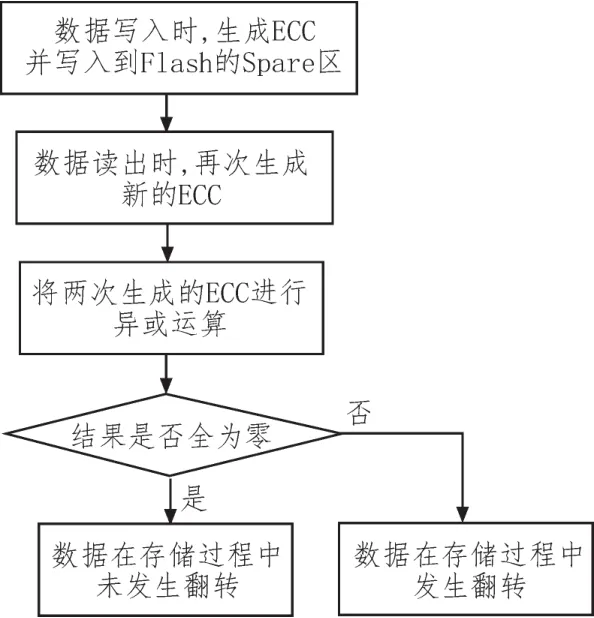

在写入操作时,生成的ECC将写入NAND Flash的Spare区,读出时,根据读出的数据再次生成的新ECC与从Spare区中读出的旧ECC通过对应位异或运算,结果可分为以下几种情况[8]:

1)若运算结果全为零,则两次ECC完全相同,说明写入的数据与读出时的数据是相同的,即NAND Flash在存储过程中数据未发生翻转;

2)若运算结果为在每个校验对(pn和′为一个校验对)中均存在一个‘1’,则说明该512字节的数据中仅有1位发生翻转,属于可纠错误。此时运算结果中p2048 p1024 p512...p8为该错误位所在字节的行偏移,p4 p2 p1为该字节内错误位的列偏移[];

3)若运算结果仅有一个‘1’,则说明存储的ECC中的一位出现了错误;

4)若运算结果非以上情况,则说明出现了一位以上的错误,报告出错但无法纠正。

如图1所示,在一组512字节的数据中,若第一个字节中的bit2在存储过程中发生了翻转,则读出时生成的 ECC 对应的p2048′p1024′...p16′p8p4′p2p1′处将会受到影响,即图中标深色的区域。使两组ECC按位异或这些位置处结果将为‘1’,即运算结果中各校验对中均存在一个‘1’,符合上述第二种情况。此时取运算结果中p2048 p1024 p512...p8对应的值即00...01即说明错误在第一个字节,p4 p2 p1对应的值为010即说明错误位在该字节中第二个位。即可定位错误位并予以翻转纠正。

2 硬件系统框架设计

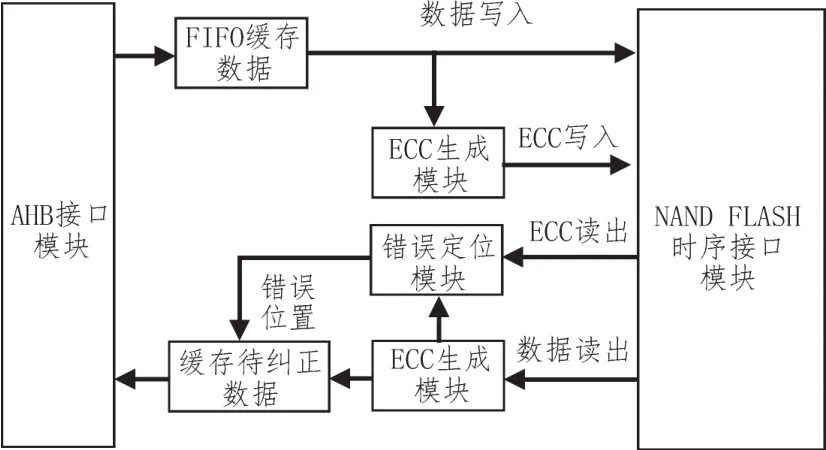

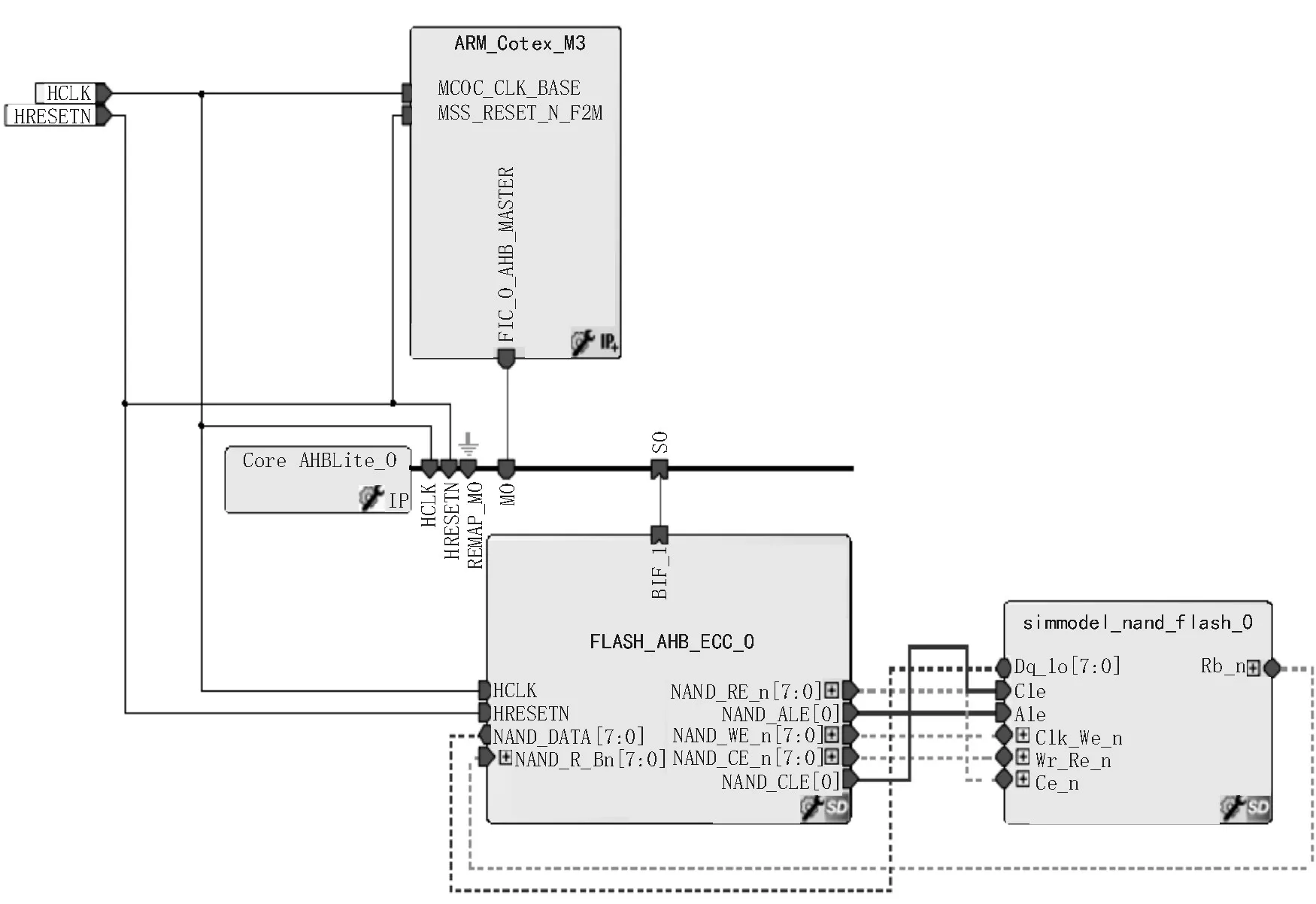

本设计基于Microsemi公司Smartfusion2系列SoC型高性能FPGA完成[10-11]。该FPGA内嵌有ARM Cortex-M3硬核。CPU通过AHB总线与FPGA层进行数据传输。这里CPU用于命令的发送与数据的接收,来进行软硬件协同验证设计的正确性[12]。NAND Flash采用三星K9F1G08UOA型号芯片[13]。该型号每页由2KB的数据区和64B的Spare区组成[14]。

本设计系统框架如图2所示。主要包括AHB接口模块,数据缓存模块,ECC校验模块及NAND Flash时序接口模块[15]。

图2 硬件系统框架图

AHB接口模块根据AMBA协议实现,将FPGA端作为slave挂接到AHB总线上与master CPU进行通信,而AHB总线可直接调用IP核通过配置使用。由于NAND Flash的读写均以页为单位[16],所以可通过配置整页大小的FIFO作为数据缓存。NAND Flash时序接口模块主要根据NAND Flash接口协议,将命令与数据通过解析来控制NAND Flash操作。ECC校验模块主要分为ECC的生成模块,错误检测与定位模块,和待纠错数据缓存模块。ECC校验流程图如图3所示。

图3 ECC校验流程图

当数据写入时,ECC生成模块根据原始数据生成ECC码,并随数据一起写入到NAND Flash中数据页所对应的Spare区。读出时将数据与存于Spare区中的ECC一并读出,所读数据将再次生成ECC,与读出的ECC一同进入错误检测与定位模块进行运算。根据运算结果将判断数据中是否存在错误及错误类型是否可纠。若错误可纠,则将错误地址输出到数据缓存模块中。由于需要对错误数据进行随机读写,所以此处采用基于SRAM的数据缓存方式。即图四中的SRAM_wrap模块。该模块底层例化SRAM IP核用于待纠正数据的存储,然后根据错误定位模块发来的地址,将发生翻转位所在字节读出,将错误位纠正,再将该字节写入底层SRAM中,最终通过AHB总线将所读数据发送给CPU来验证数据的正确性。

3 功能实现及仿真

文中基于Libero SoC 11.3开发环境中采用VHDL语言对NAND Flash ECC校验系统进行了设计与实现。该ECC校验系统顶层用于仿真的模块如图4所示。并在ModelSim SE-6410.4环境下进行仿真。采用NAND Flash model阵列模拟真实Flash芯片行为,编写bfm(bus function model)即总线功能模型脚本产生AHB Master端的激励,即可进行系统仿真。

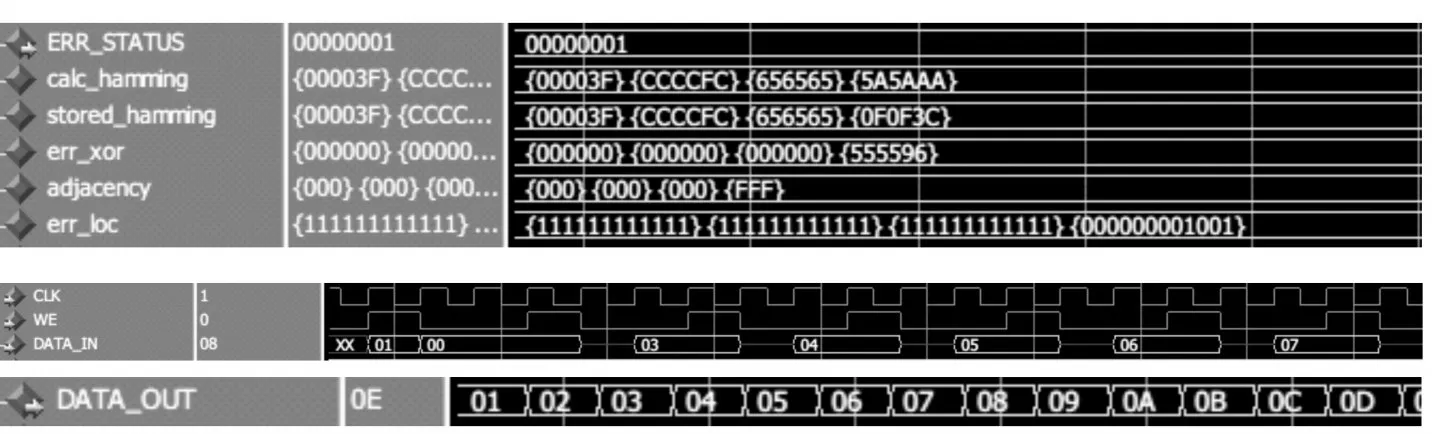

本设计采用的NAND Flash芯片每页为2 K字节,故将其分为4组512字节分别进行校验。为了测试该ECC校验系统具体检错与纠错功能,在NAND Flash接口模块中在读出时故意做了数据的改动。将第零组数据中的第一个字节写入‘x02’改为了‘x00’,即将数据二进制中的第一位翻转。仿真结果如图5所示。ERR_STATUS为对出错状态的报告,‘b00’为无错误,‘b01’为数据中发生一位错误,‘b10’为 ECC 中发生一位错误。‘b11’为发生一位以上的错误。图中显示出第零组数据中发生一位错误。并且由err_loc报告出错误所在位置。即为第一个字节中的第一位。DATA_IN与DATA_OUT为SRAM_wrap模块中 对错误数据的纠正,即将‘x00’改回为‘x02’。

图4 ECC校验系统顶层模块图

图5 ECC校验系统仿真时序图

4 结束语

由于NAND Flash存储设备具有掉电非易失性,存取速度快,低功耗,抗震性等优点,在嵌入式领域已经逐渐取代磁介质存储器,成为解决高密度存储的主流方案。针对其工艺结构局限而可能导致低概率的位翻转问题,本文给出了基于汉明码ECC校验系统完整的设计及实现方案。

基于汉明码的ECC校验算法具有便于硬件实现且占用资源较少运算速度快的特点,且可通过对冗余码的增加来实现对纠错能力的扩展。因此汉明码可以作为SLC类型NAND Flash应用中可以采用的性价比非常高的一种纠错方式。

基于FPGA的设计一方面可以节省由传统软件实现校验而带来CPU资源的占用与开销,另一方面由于硬件的并行性可满足高速存储设备对于实时性的要求。因此,本设计具有较高的工程应用价值。