VDMOS 横向变掺杂终端的优化与设计

(西南交通大学微电子研究所,四川成都 611756)

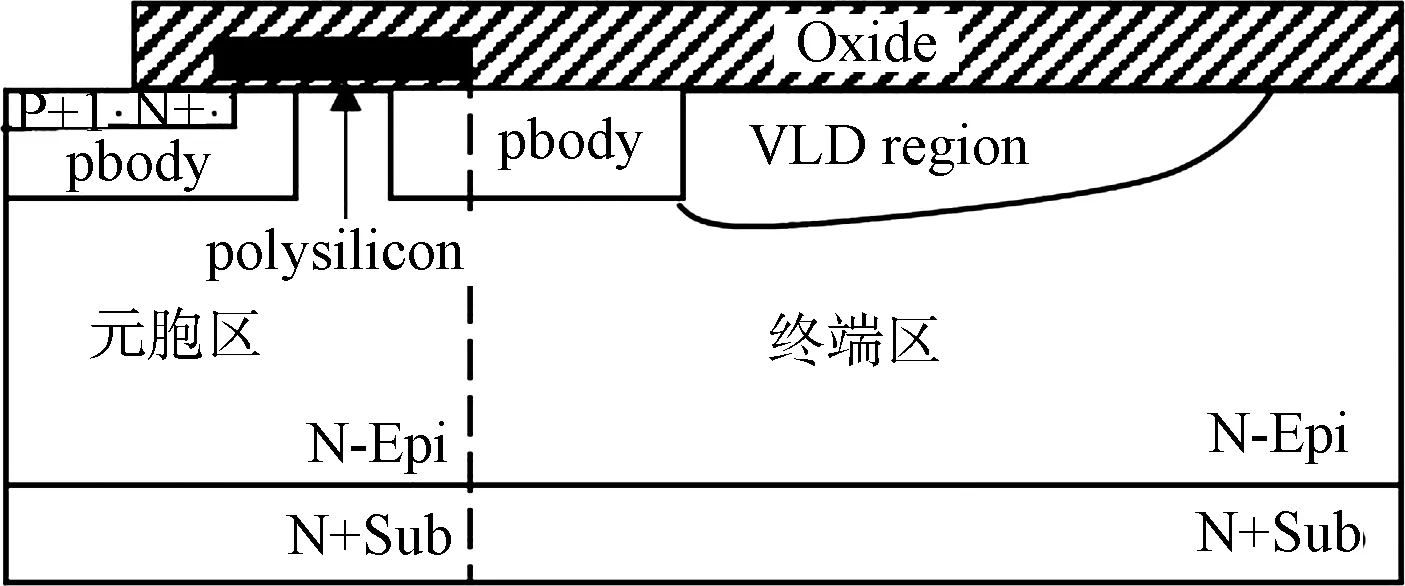

功率半导体器件中VDMOS(Vertical Double Diffusion Power Metal-Oxide-Semiconductor)是一种常见的器件,VDMOS器件的结构由元胞区和终端区两部分组成,VDMOS器件的主要参数是击穿电压、阈值电压、导通电阻;而元胞区决定器件的阈值电压和导通电阻,终端区决定了器件的反向击穿电压。

目前VDMOS在工业中经常使用的终端有以下几种:场板(Filed Plate,FR)、场限环(Filed Limiting Ring,FLR)、结终端扩展(Junction TerminationExtension,JTE)、横向变掺杂(Variation of Lateral Doping,VLD)[1]。

其中,横向变掺杂技术通过改变器件终端掺杂区的开窗实现降低表面电场的作用,在反向偏置下使整个VLD区完全耗尽,PN结耗尽层会向终端外侧扩展使耗尽区的边界曲率半径变大,从而有效地提高反向击穿电压。本文介绍了关于VLD注入开窗和掩膜间距调整的方法,借助Sentaurus TCAD仿真软件进行验证,在终端能够有效地形成VLD区,且提高了反向击穿电压。

1 结终端的简单理论

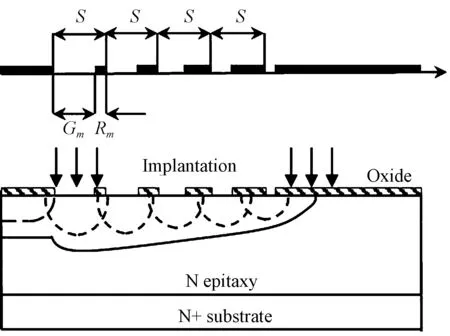

VDMOS器件的内部结构如图1所示,其中耐压能力是由终端结构决定,横向变掺杂结构对提高VDMOS的击穿电压是非常有效的,对于横向变掺杂结构严格来说只有一个PN结,就是对主结的一个延生来实现耐压。耗尽区不能有效地扩展,将会产生电力线的聚集和节电场的汇聚,使终端的耐压很低[2]。在以上理论条件下,直接把电荷引入来扩展耗尽区,将N区指向P区的电场抵消一部分,就会有效地缓解电场集中的现象,得到近似矩形的表面电场分布,从而提高终端的反向击穿电压。

图1 VDMOS器件结构图Fig.1 Schematic diagram of the VDMOS device structure

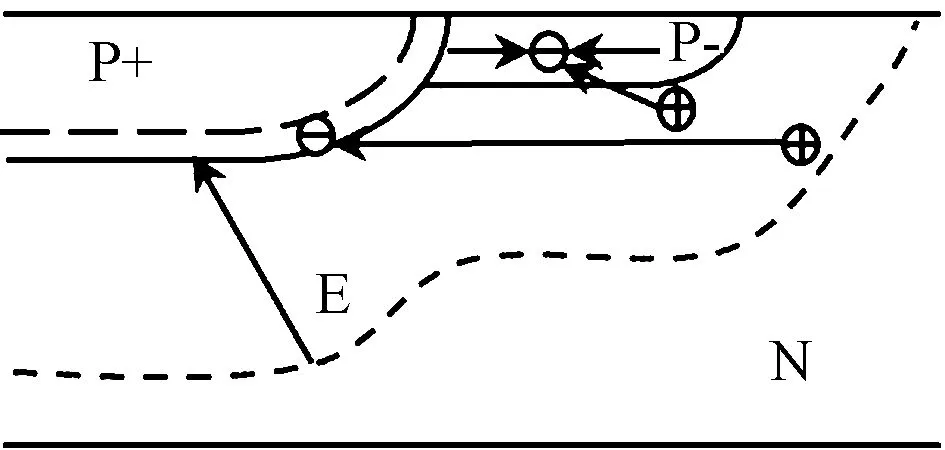

图2为引入电荷缓解电场集中的结构示意图,这种结构是在主结边缘处注入一个轻掺杂的P区。

图2 结终端延生结构Fig.2 Schematic diagram of the junction termination extension structure

当PN结工作在反向偏置时,掺杂浓度较低的P区将会全部耗尽并填满负电荷,负电荷产生的电场线会抵消部分N型耗尽区正电荷产生的电场线,使电场的分布更加均匀,击穿电压得到有效的提高[3-4]。

P型轻掺杂区的注入剂量非常重要,如果P型轻掺杂区的注入剂量太大,则PN结在反向偏压下,P型轻掺杂区就不能完全耗尽,导致电场线集中,提前在主结发生击穿。若P型轻掺杂区注入剂量过小,主结也不能得到有效的保护,同样会导致击穿电压偏低。只有适当地控制P型杂质剂量才能得到相对理想的击穿电压。

如图2所示的结构对于高电压大功率器件而言,受到一定的限制,于是提出了多演变结构。横向变掺杂结构是越靠近主结的地方注入剂量较大,而远离主结的地方注入量较小,通过杂质的横向扩散,使注入的杂质连在一起,形成一个有规则的图形[5]。如图3所示。

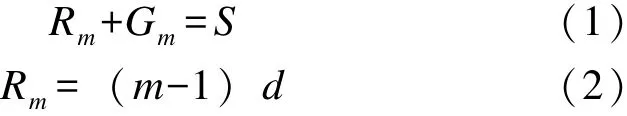

杂质的注入窗口和掩膜的阻挡窗口要求为:

式中:Rm为掩膜板阻挡窗口的宽度;Gm为注入窗口的宽度;S为掩膜板阻挡窗口和注入窗口总间距;d为注入窗口的序列号;m=1,2,3,…,n[6-8]。

图3 横向变掺杂结构Fig.3 Schematic diagram of the variable lateral doping structure

2 仿真结果分析

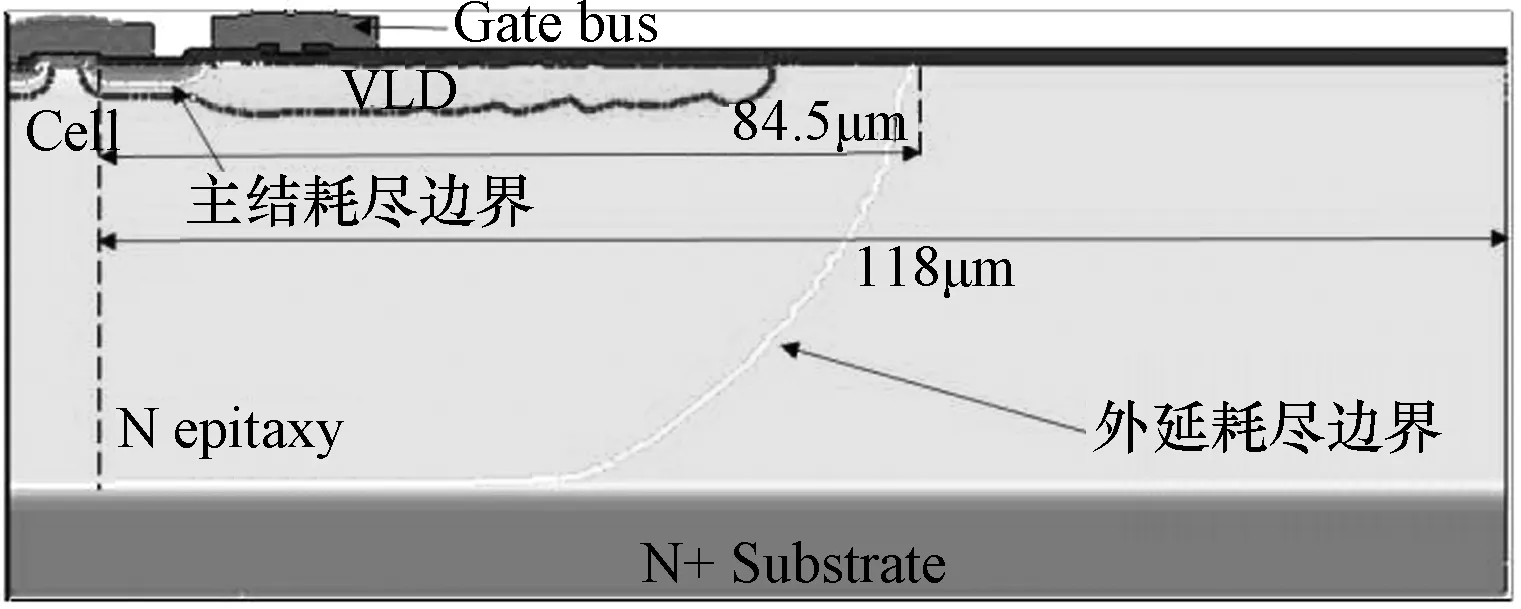

根据以上理论设计一种650 V的VDMOS终端结构,外延浓度为2.44×1014cm-3,外延厚度为56 μm,VLD 注入剂量为 2.0×1012cm-2、S=8 μm,VLD的最大结深为5.8 μm。利用Sentaurus TCAD仿真工具对横向变掺杂终端结构进行仿真,掺杂模型如图4所示。当工作在反向偏压时VLD区几乎完全耗尽,P型耗尽边界在主结处,主结耗尽边界到外延耗尽边界的最大横向距离为84.5 μm,终端区总宽度为118 μm。

图4 终端结构模型Fig.4 Model of the termination structure

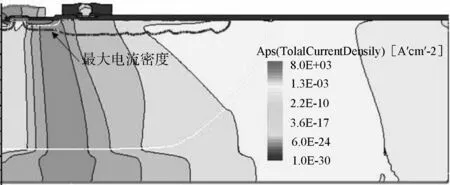

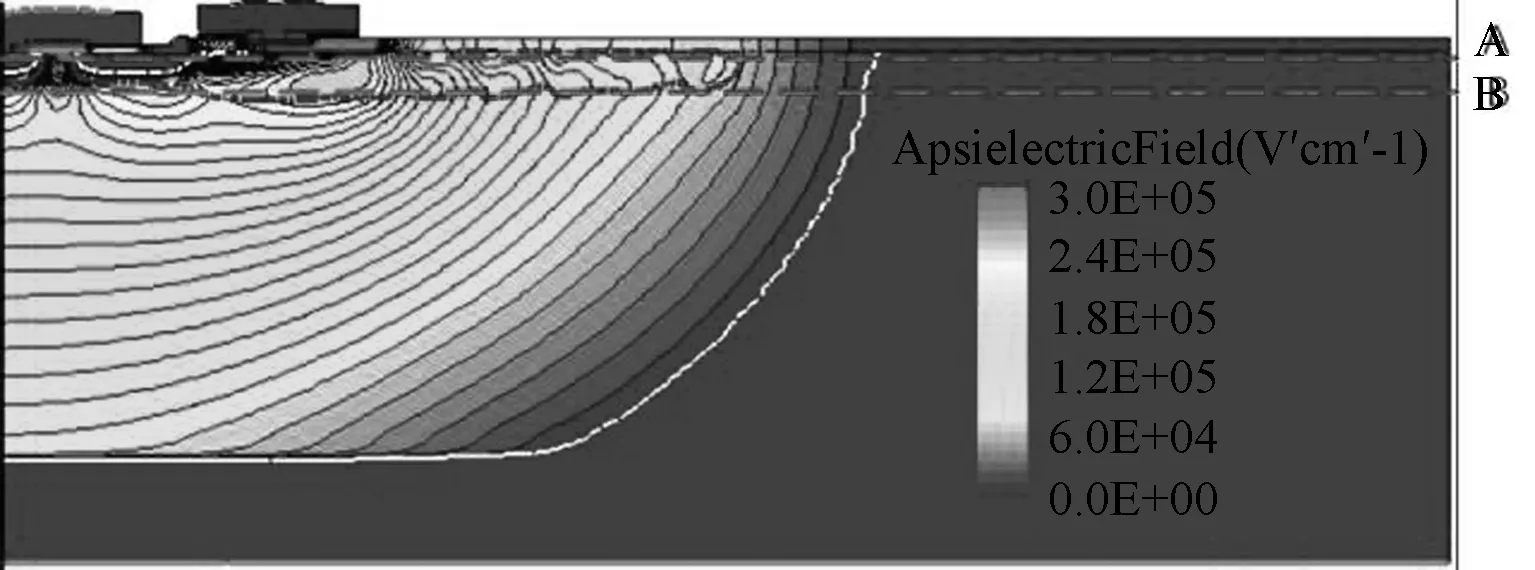

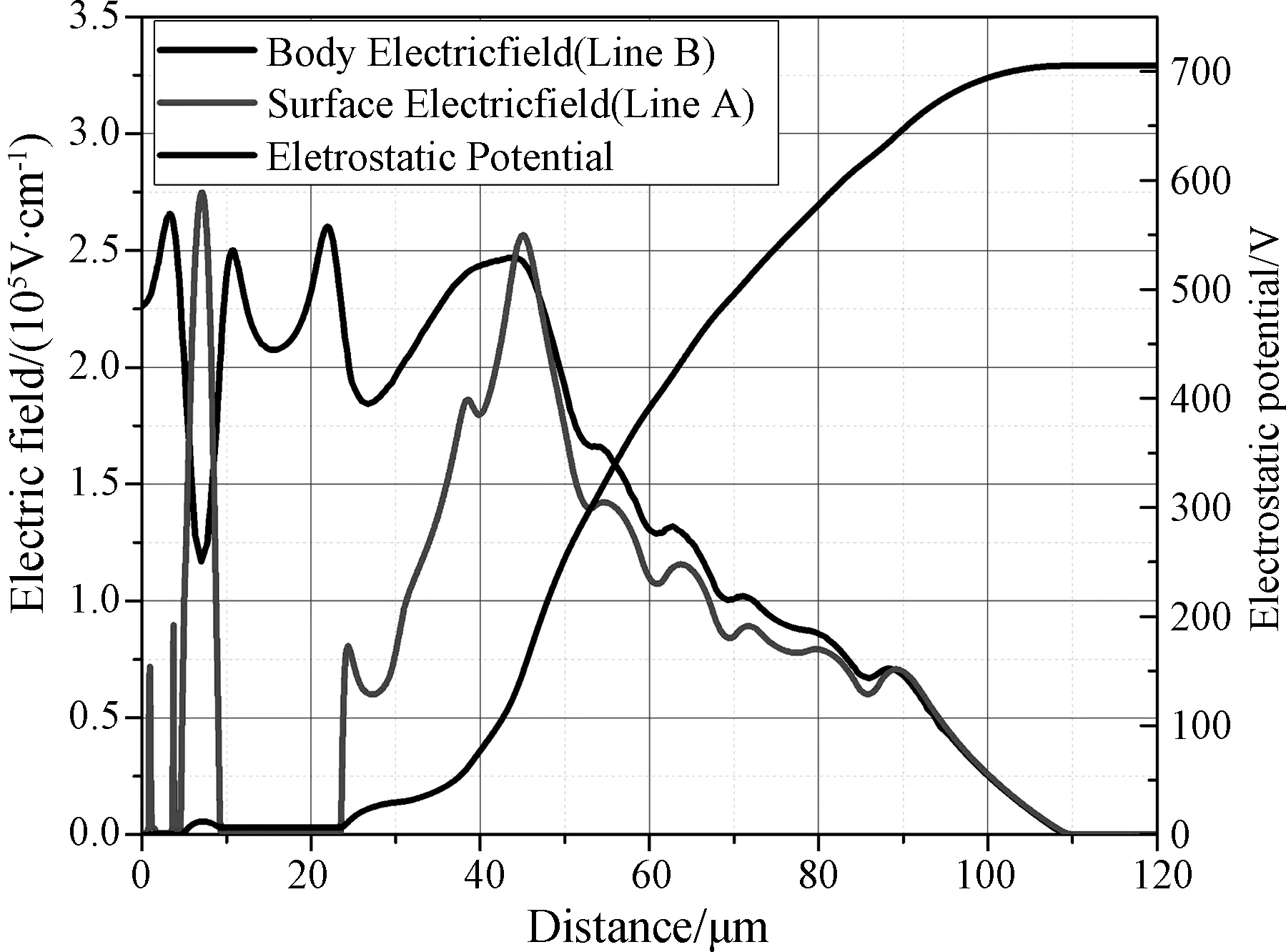

图5为击穿时的电流密度分布模型,从中可以看出最大电流密度在主结边缘处,使耐压达到最大,此处也是终端的击穿点。图6是电场分布模型,最大电场为3.0×105V·cm-1出现在氧化层中。在电场模型中分别截取了两条曲线,其中切线A为硅表面电场,切线B为体内电场。

图5 电流分布模型Fig.5 Model of the current distributions

图6 电场分布模型Fig.6 Model of the electric field distributions

图7是电场分布和表面电势曲线。从图7中可以看出主结处的最大电场为2.68×105V·cm-1,横向变掺杂区的最大电场为2.50×105V·cm-1,由于崩溃点发生在主结处,那么在这种掺杂下的崩溃电场也为2.68×105V·cm-1。横向变掺杂区的最大电场接近崩溃电场,说明该设计下横向变掺杂区发挥了最大限度,横向变掺杂区的横向耐压占整个终端耐压的99.01%。

图7 电场分布和表面电势曲线Fig.7 Electric field and potential near the device’s surface

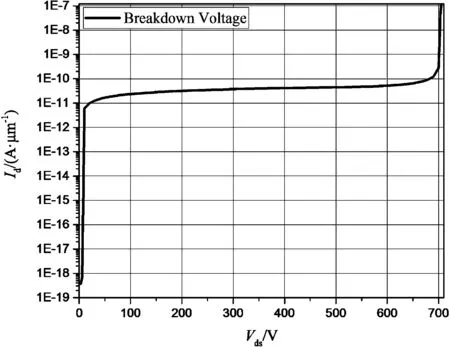

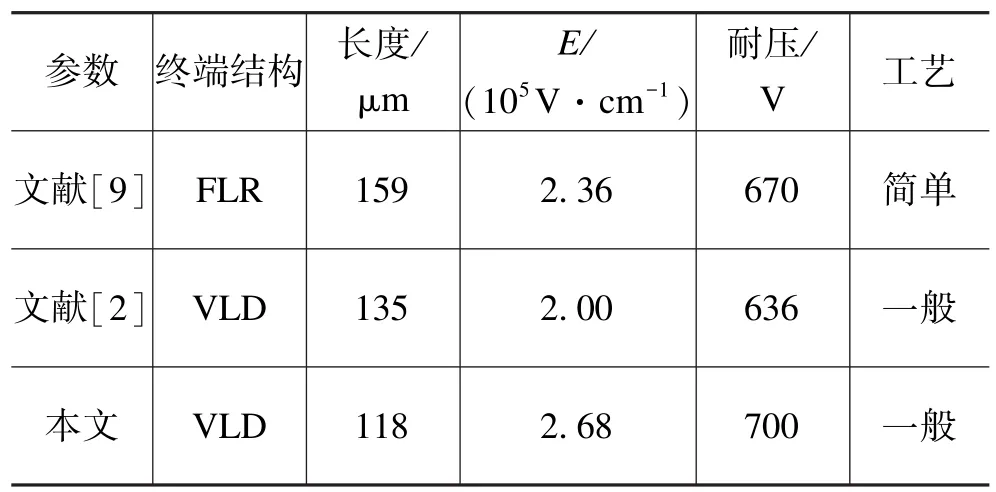

终端工作在反向偏置的击穿曲线如图8所示,击穿电压为700 V。根据设计的外延参数得到元胞区的仿真耐压为750 V,终端耐压的效率为93.33%,而传统的FLR终端结构效率只有80%[10]。与其他文献终端结构设计的比较,如表1所示。

图8 终端的击穿电压曲线Fig.8 Characteristic curve of breakdown voltage on termination

表1 不同终端结构的比较Tab.1 Compare to different termination structure

3 结论

通过横向变掺杂技术设计了一款650 V的终端结构,终端结构的长度为118 μm,仿真得出的击穿电压为700 V,最大电场为2.68×105V·cm-1。与文献[8]相比终端长度缩短了25.8%,有利于减少芯片成本提高晶圆利用率。但在工艺上相比FLR结构终端要复杂一些。