高压DDDMOS的设计及优化

(集美大学 信息工程学院,福建 厦门 361021)

近年来,随着平板显示器和便携式设备的日益普及,平板显示器驱动芯片和电源管理芯片的高压集成电路日益受到关注。由于高压双扩散漏端器件具有制作简单,容易与传统工艺兼容,成本较低等优点,因此常用来控制芯片中的高压信号。RESURF降低表面电场技术是设计横向功率器件的关键技术之一。本文在研究了各种最新应用于DDDMOS提高源漏击穿电压的结构参数和设计理论后,实现了在标准 P型衬底和漂移区长度为2 μm的情况下,在不改变器件的工艺兼容性如衬底浓度,源漏掺杂浓度和源漏扩散时间等情况下,实现栅极尺寸减小以缩小DDDMOS的器件面积,击穿电压增加,最终实现了DDDMOS的优化。

1 高压DDDMOS工作原理

本文中的高压MOSFET采用双扩散漏端结构(DDD),这种结构的最大特点就是在重掺杂的漏端外围包围着一层轻掺杂结构,即n-区,以此增加该MOS管的耐高压能力。这种与传统的MOS管明显存在差异的高压MOS管,先是经过第一次扩散形成n-区域,再进行第二次扩散,形成n+区域,这样形成的特殊轻掺杂结构,在原有传统的n+区域外,也就是高掺杂源漏区外,形成了一个深扩散结,这个深扩散结较之高掺杂源漏区,浓度较小,结深较深,结构示意图见图1。由于这个轻掺杂的关系,使得PN结的曲率半径变大,而曲率半径的变化也影响着击穿电压的变化,一般情况下,曲率半径越大,击穿电压也越大。同时,原本在源漏的近似突变结在高压情况下也变为了深扩散结,通过一个跨度,杂质浓度梯度变小,使得源漏区之间的电阻变大,使得MOS管的耐压能力进一步增强。

图1 DDDMOSFET结构示意图

2 DDDMOSFET的优化

2.1 DDDMOS在TCAD中的工艺仿真

在TCAD中,要对DDDMOS进行工艺仿真,以下几个步骤即DDDMOS的Athena工艺仿真流程。

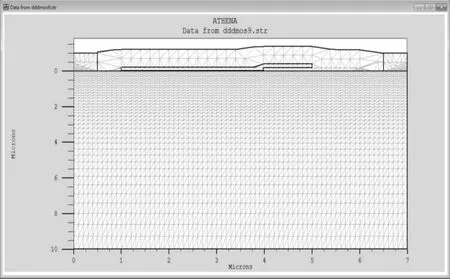

建立仿真网格,如下图2所示,将临近DDDMOS器件表面的网格设置得比较密集,而衬底下方的网格设置得比较疏松,这样对于表面一些物理量,可以抽取到更为准确的数据。网格设置的一般语法为:line x(或者y)loc=设定值 spac=设定值。

图2 DDDMOS网格设置示例图

仿真初始化,工艺仿真中的初始化可以定义衬底,也可以初始化仿真。

工艺步骤,本文比较常用的为Deposition,Diffusion,Etch,Implantation这几个工艺。

抽取特性,deckbuild有内建的抽取功能。

结构操作,主要用structure语句进行命令,可以保存和导入结构。

Tonyplot显示,tonyplot可视化工具用来显示当前的结构或是已经保存的结构文件的结构或掺杂等信息,如图3中就是本文工艺仿真得到的结构。

图3 DDDMOS工艺仿真结构图

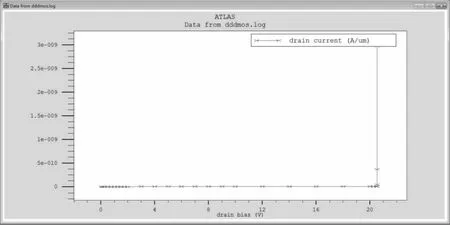

在本文中,当DDDMOS器件的gate尺寸为3 μm,P衬底电阻率为10,晶向为<100>,阈值电压调整离子浓度为2e12cm-3,注入剂量为60 keV,漂移区离子浓度为5e15cm-3,能量为80 keV,以温度为1100℃的条件推进60 min,n+离子浓度为8e15cm-3,能量为80 keV,以温度为1100℃的条件推进60分钟,从图4的结构图看以看出,此时的DDDMOS并没有场极板结构,通过TCAD软件测量出来DDDMOS此时的击穿电压为20.5 V,对于一个工作电压为20 V的高压DDDMOS,为保证器件工作的安全性和稳定,一般情况下击穿电压都需要有工作电压10%的电压余量,即击穿电压=(1+10%)工作电压,通过这个简单的式子可以得出此时的击穿电压至少为22 V才可避免该器件过早击穿,从图5中明显看出,当漏源极电压VDS超过20.5 V,漏源极电流ID将迅速上升,使ID迅速上升的漏源电压称为漏源击穿电压,此时器件的击穿电压为20.5 V,不能满足设计要求,需要对该器件进行适当的优化以提高其击穿电压。

图4 DDDMOS工艺仿真无场板结构图

图5 DDDMOS无场板击穿电压仿真图

为了降低该器件的表面电场,本文模拟出图3中所示的DDDMOS器件结构,与图4比较发现,此时的DDDMOS多出了场板结构,在器件其他条件都一样的情况下,再一次进行击穿电压的测量,虽然此时的击穿电压有提高,由原来的20.5 V提高到21.7 V,如图6所示,但是因为其他因素的影响导致pn结处的表面电场依然很高,场板结构在此时并没有使击穿电压大大提高,依然不满足本文的设计要求,因此需要对影响击穿电压的主要参数进行进一步的优化。

图6 DDDMOS有场板时击穿电压仿真图

2.2 各参数的仿真以及分析

2.2.1 gate尺寸的优化及仿真

若要保持DDDMOS的结构不变,而要减小整个DDDMOS器件的面积,可以通过减小gate尺寸或者是漂移区的长度来减小器件的整体面积[1],在本文中,主要研究的部分在n+范围以内,而漂移区的长度比较不好控制精确的量,因此通过减小gate的尺寸来减小器件的整体面积。

其中n-区域的注入条件P/5e15cm-3/80 kev,击穿电压随着gate尺寸变化的仿真结果如图7所示。从图中可以看出,在栅极尺寸为原始值3 μm时,DDDMOS的击穿电压为21.7 V,随着栅极尺寸在一定范围内的减小,击穿电压保持在一个不变的范围内,当栅极尺寸缩小到1.4 μm以下时,击穿电压开始缓慢的变小。当栅极尺寸小于1.4 μm时,击穿电压会不断地减小,当栅极尺寸超过1.4 μm时,虽然击穿电压并没有变大,但是DDDMOS器件的面积却变小了,因此可以考虑当栅极尺寸为1.4 μm时,器件的尺寸可达到最佳值。

图7 击穿电压与栅极尺寸关系图

20 V HV DDDMOS在应用中,其栅氧上的开启电压需要达到1.2 V左右,在图8中,开启电压达到了1.2 V,基本上达到了设计要求。

2.2.2 结深的优化及仿真

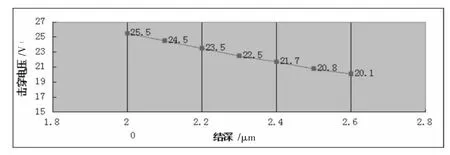

结深一般定义为从硅中表面到扩散层浓度等于衬底浓度处之间的距离,一般以微米为单位计量。在工艺仿真中,结深与离子注入剂量和能量,以及退火的温度和时间有关[2],本节通过调节退火的时间来控制结深,从而达到验证的目的。

通过软件仿真得到如图9的结果,可以看出,当漂移区的结深值越大时,击穿电压的值反而越小,当结深为2.6 μm时,击穿电压为20.1 V,不仅击穿电压比较低,同时通过仿真结果图10发现DDDMOS器件存在源漏穿通的现象,所谓的源漏穿通就是当VDS增加某一数值时,虽然漏区与衬底间尚未发生雪崩击穿,但漏PN结的耗尽区却已经扩展到与源区相连接了,发生漏源穿通后,如果VDS继续增加,源PN结上会出现正偏,使电子从源区注入沟道,这些电子将被耗尽层区内的强电场扫入漏区,从而产生较大的漏极电流;当结深值为2 μm时,仿真结果显示DDDMOS同样存在源漏穿通的现象,因此理论上,当结深为2.1 μm时,可达到最佳优化值。

图9 击穿电压与结深关系图

图10 高压DDDMOS源漏穿通仿真图

2.2.3 漂移区浓度的优化及仿真

根据 RESURF原理,器件的漂移区浓度必须满足一定的条件,当外加电压达到击穿电压时,漂移区全部耗尽,由整个漂移区承受外加电压,这样才能得到高的耐压。如果漂移区的浓度过低,当漏端电压增大时,漂移区过早耗尽,漏端的电力线集中,器件提早在漏端击穿。如果漂移区的浓度过高,其难以耗尽,电力线在 Psub/N-结处集中,器件也会过早击穿。当漂移区浓度达到优化值时,源端和漏端的电场分布较为均匀,器件的反向耐压达到最大[3-5]。

在图11中,当漂移区的浓度超出5e15cm-3的范围值时,DDDMOS器件由于漂移区浓度较高难以耗尽[6],导致其击穿电压也比较低,不满足设计要求,不作为优化的考虑范围。当漂移区的浓度为1e15cm-3时,仿真得到的击穿电压为33.4 V,完全满足了击穿电压至少为22 V时的设计要求,但是和图10仿真结果图一样,此时的源漏两端发生了穿通击穿,虽然击穿电压满足设计要求,依然不作为优化的考虑范围。

2.2.4 最终优化结果及分析

我们将对DDDMOS进行最终的优化,理论上采用每个小节的最佳理论值,这样的优化结果应当是最符合条件的,但是经过仿真发现,这种情况下的I/V曲线出现不正常的情况,而后这样的优化不仅不能得到理想中的结果,漏极电流仿真结果还出现了下图12中的异常现象。通过器件仿真发现,此时的结深边界在场氧区的中间位置,为保证阈值电压的准确性和实验的严谨性,一般将结深边界靠近在栅极处。

图11 击穿电压与漂移区浓度关系图

图12 漏极电流仿真结果图

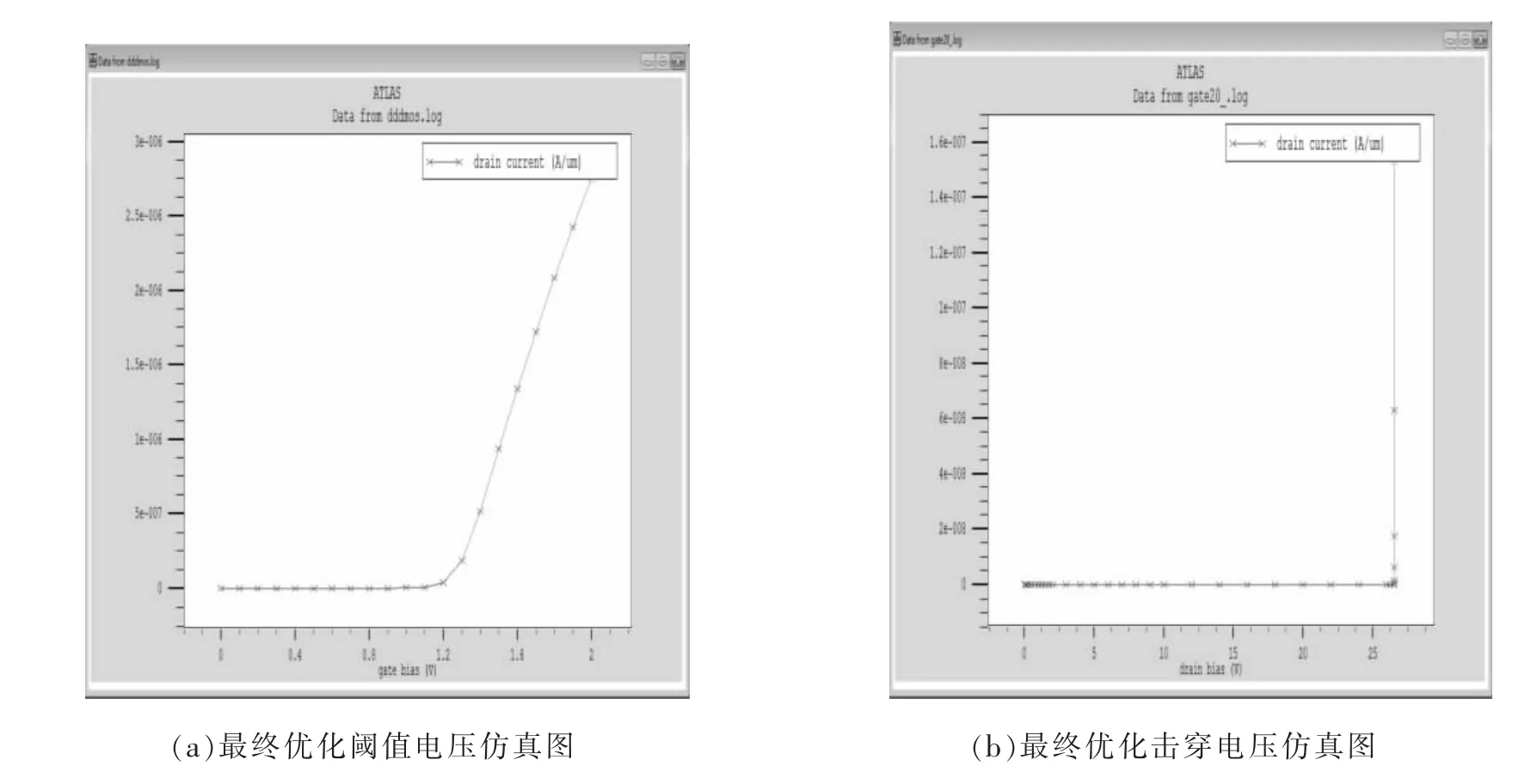

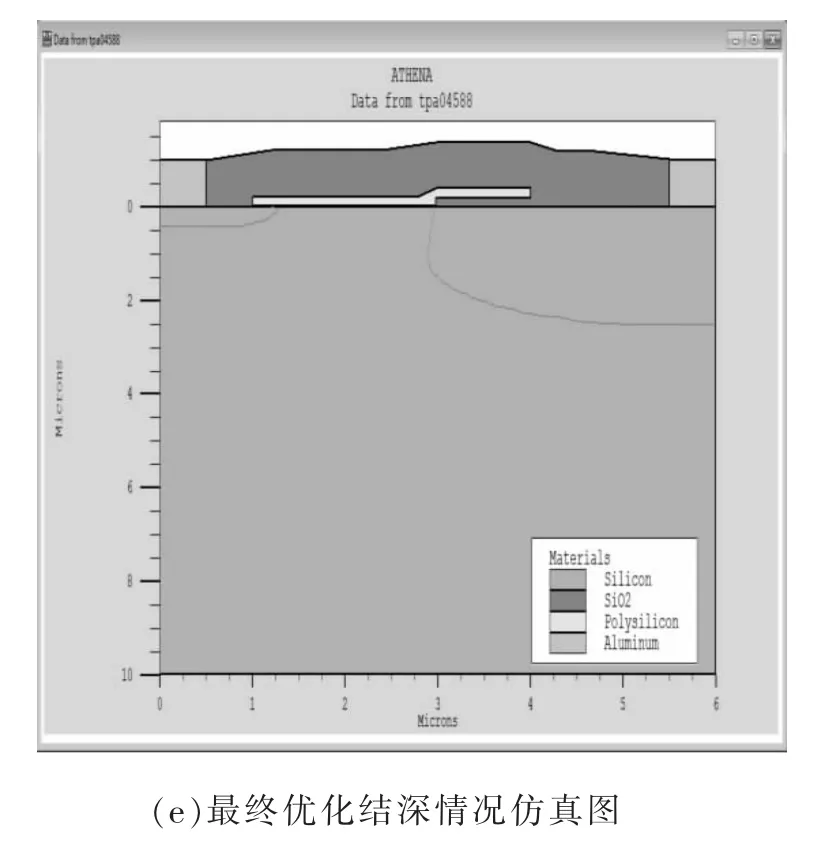

因此,再通过优化,得到了gate尺寸为2 μm,P衬底电阻率为10,晶向为<100>,阈值电压调整离子浓度为2e12cm-3,注入剂量为60 keV,漂移区离子浓度为3e15cm-3,能量为80 keV,以温度为1100℃的条件推进50 min,n+离子浓度为8e15cm-3,能量为80 keV,以温度为1100℃的条件推进60 min,通过仿真得到了最终优化值,此时的击穿电压为26.3 V,阈值电压和结构上也满足设计要求。其中,高压DDDMOS最终的优化及其各参数的仿真如图13中所示。

图13 最终优化参数图

4 结论

经过设计和分步的优化,栅极尺寸由原来的 3 μm 缩小到 2 μm,整整缩小了 1 μm 的长度,而通过增加场极板,更改结深和漂移区浓度这些操作,HV DDDMOS的击穿电压由最开始的20.5 V提高到了26.3 V,对于一个工作电压在20 V的高压MOS器件,本文的设计完全符合设计要求。同时,本文中所研究的参数具有对原有工艺的兼容性,并没有使用不兼容于现有半导体制造工艺的制造方法和材料,这样可以保证论文的理论分析可以对实际工作起到一定的参考作用,最终将通过软件仿真的结论性成果应用于实际工作中。