基于中规模集成电路实现任意进制定时器

陈圣涛

(铜陵职业技术学院 机电工程系,安徽 铜陵 244000)

定时器是数字系统中不可或缺的一部分,其不但可以用来计数、定时、分频,而且还常常被用作测量脉冲频率和各种脉冲的宽度,进而构成生活中各种各样的电路.定时器在一定的特定条件下的一些功能用途的实现有着极大的开发前景,这种集多功能于一体的特点,给人们带来了非常大的方便,满足科研工业上的需要.因此,任意进制的定时器的研究与开发拥有广阔的市场与科研价值[1].

1 中规模集成计数器构成任意进制计数器的原理

中规模集成计数器(MSI)中虽然有各种不同进制的模块,但是一个计数器的功能块的进制很少,而且需要复杂的过程才能进行进制,这样就严重影响性能.对此,利用中规模集成计数器进行适当的连接则可实现任意进制计数器[2],因此本文的研究具有重要意义.

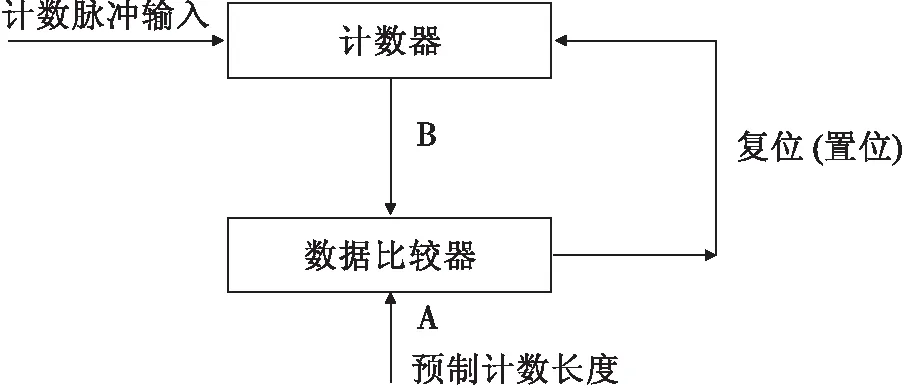

中规模集成计数器构成任意进制计数器的原理[3]如下:通过数据比较器进行预制计数长度A和计数器输出B的比较,然后通过数据比较器输出一个脉冲,此脉冲直接输送到计数器,可以实现计数器的清零和置位功能.由于A表示预制的计算长度,则通过改变其长度,可以实现任意进制计数器的改变,其基本原理[4]见图1.

2 单片构成N(N<10)进制计数器

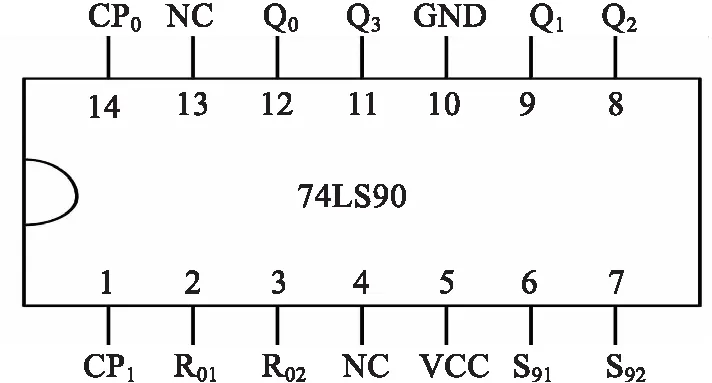

本文首先对74LS90的功能进行简要分析,其主要作为二进制计数器或者五进制计数器,在特殊情况下,可以转变为十进制计数器.该计数器具有普遍计数器均存在的功能清零和置位.图2中的R表示对计数器进行清零,而S表示对计数器进行置位功能,下面将分别对其功能进行介绍[5-6].

图1 计数器基本原理图

图2 74LS90引脚图示

2.1 复位法

当图2中的两个具有清零功能R都是高电平的时候,而且此时保证置位功能的两个S至少存在一个低电平时,此时对输入状态没有任何限制,这个时候的计数器的四个输出Q均为0,这种称为清零或者复位[7].

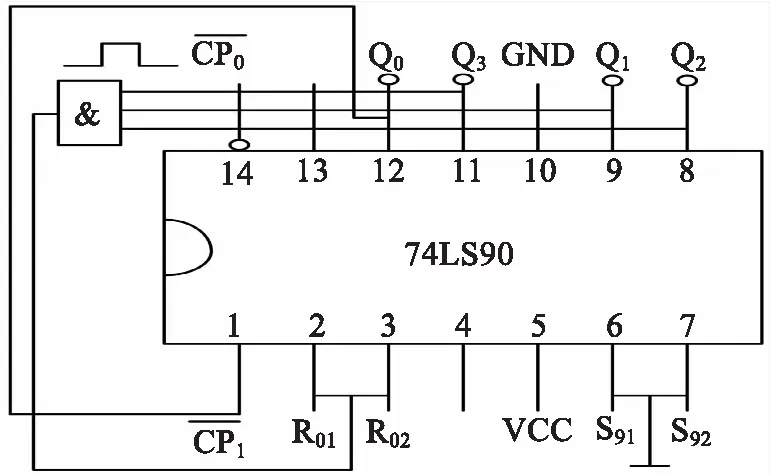

如图3所示,采用复位法可以实现七进制计数器.即当计数器计数到7的时候,计数器会自动清零,此时该计数器含有七个有效的独立运行的计数器状态,按照十进制计数器要求,应该含有十个有效的独立运行的计数器状态,而7进制则说明,必须有3个无效的运行状态,即(0111-1001),使其跳过该无效状态,当第7个脉冲过来时,要求此时计数器不是返回0111,而是直接达到复位状态.即到0000状态,但是一般此时不能满足这个状态,其计数器状态是从0110转到0111,而不能达到0000状态.此时采用置位方法,使其强迫的达到0000状态.当计数器达到0111的时候,通过逻辑与门,使其具有清零的功能,这个时候计数器能够迅速达到0000状态,而0111这种状态是一个非常非常短的一个过渡状态,只是稍微闪了一下,一般看不到,就自动清零了.因此,复位法的使用,使得计数器的实际状态变成0000-0110这7个实际的状态,即可达到七进制计数器的实现功能[8].

2.2 置位法

2.2.1 置入最大值法

当保证具有置位功能的两个S全部为高电平的时候,两个具有清零功能R至少有一个低电平时,此时对输入状态没有任何限制,这个时候的计数器的4个输出Q为1001,这种称为置入最大值法.

2.2.2 置入最小值法

当具有置位功能的两个S和具有清零功能R不全为高电位时候,当有计数脉冲输入时,此时开始计数,当计数器的4个输出Q为0001时,这种称为置入最小值法.其主要包括以下几种方式:

1)二进制计数器

如图4所示,把一个输入脉冲从计数器74LS90的CP0输入时候,在输出端只要一个Q0输出时,此时可以把计数器74LS90看做是二进制计数器.

图3 七进制计数器的实现

图4 二进制计数器的实现

2)五进制计数器

如图5所示,把一个输入脉冲从计数器74LS90的CP1输入时候,在输出端除了Q0没有输出外,其他3个具有输出时,此时可以把计数器74LS90看做是五进制计数器.

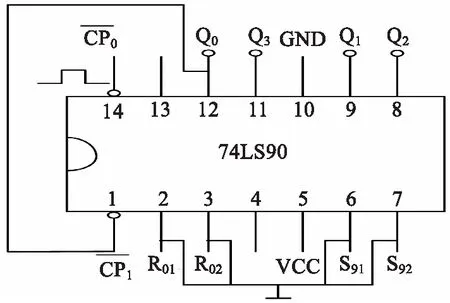

3)十进制计数器

如图6所示,把一个输入脉冲从计数器74LS90的CP0输入时候,且保证CP1和Q0直接相连接,在输出端具有4个输出时,此时可以把计数器74LS90看做是十进制计数器.

图5 五进制计数器的实现

图6 十进制计数器的实现

综上,单片74LS90可以构成N(N≤10)进制计数器,这个时候,只需要把属于BCD码中的高电平的输出端进行逻辑与运算,其结果放在计数器的R端,此时方可实现对N(N≤10)进制计数器的设计.

2.3 级联法

当N进制中的N取值较大的时候,此时N应大于10小于100,此时可以通过级联的方式进行N进制的设计.比如,可以用两个计数器74LS90就可以实现100进制的设计,此时两个计数器分别为个位和十位.

3 多片构成N(N>10)进制计数器

设计N>10的进制计数器是因为在日常生活中,往往不能仅仅靠十进制内的计数器完成任务,像生活中常见的钟表,常常需要的就是六十进制和二十四进制的计数器,类似的还有计件工厂对于产品数目的计算,一般以十二进制为主,轮数到十二个的时候增加一等.因此,在生产生活中任意进制的计数器的作用是非常大的.本文主要介绍生活中常用的二十四进制和六十进制的设计,由于已经超过了十进制,通过级联方法来增加整个设计的计数进制值,就需要多片芯片完成设计[9].

3.1 二十四进制设计

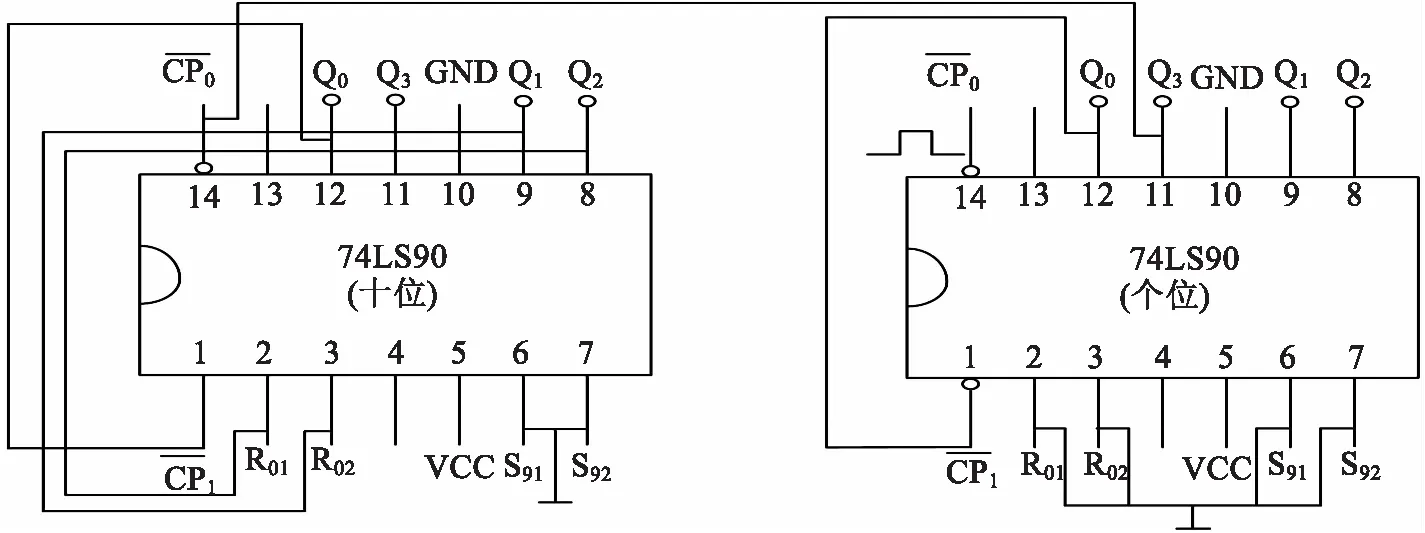

二十四将其分开来看主要由个位和十位组成,这样就需要两个芯片组成,通过片选信号进行个位十位的选择,由于采用标准的十进制进行设计就要满足“逢十进一”的规则.由于74LS90芯片的逻辑功能,将选择连接成十进制形式.整个设计过程则为:个位上的数因为脉冲数的不断输入进行计数,直至计算到十,则个位最高位的则向十位的脉冲输入端发一个脉冲信号,此时十位进行数字加一,连接如图7所示.

如图7所示,芯片分为个位和十位分开计数,当个位的CP0得到脉冲信号后,个位开始计数,当计数值达到10后,Q3输出信号给十位,十位进值为1,当Q3第二次输出信号时,十位得到信号计数值变成2,由于是二十四进制,即拆分成2进制数则用BCD码表示为“00100100”也就是当个位的Q2与十位的Q1同时为1时,达到二十四,通过“与”门,将两个信号相应输出到十位的R01和R02中,完成一整个进制的循环,即对信号进行重新计数输出,完成整个二十四进制的设计.

图7 二十四进制计数器的实现

3.2 六十进制的设计

六十进制的设计与二十四进制设计类似,也是将六十分为两个部分,即个位和十位,同样的也是通过两个芯片组合完成,再通过片选信号去选择计数值的个位和十位,仍旧采用标准的十进制进行六十进制的设计.由于74LS90芯片的逻辑功能,根据前面的介绍,将选择连接成十进制形式,整个设计过程则为:个位上的数因为脉冲数的不断输入进行计数,直至计算到十,则个位最高位的则向十位的脉冲输入端发一个脉冲信号,此时十位进行数字加一,也满足“逢十进一”的规则.连接如图8所示.

图8 六十进制计数器的实现

如图8所示,两个芯片仍然分为个位和十位分开计数,由于个位仍按照十进制进行设计,个位的CP0得到脉冲信号后,个位开始累计计数,计数值达到10后,此时Q3位为高电平,直接将高电平信号输出发送到十位芯片上,十位计数值则变成1,如此循环,当Q3第六次输出信号时,十位得到信号计数值变成6.根据六十进制的设置,拆分成二进制数则用BCD码表示为“01100000”,即个位的Q3和Q2同时为1时,达到六十进制的最大值,将两个信号直接输出到清零位的R10和R20上,数据清零后完成六十进制的一次循环,下次得到外部脉冲再对信号开始重新计数输出,完成六十进制的设计.

3.3 几种方法的优缺点

通过上面的介绍分析,可以总结反馈清零法、反馈置数法和级联法这3种算法的优缺点.

反馈清零法通过七进制的分析可知,因为在清零信号的负脉冲有可能会随着计数器的清零而发生消失的情况.在这种情况下,会出现负脉冲的时间仅仅具有很短的保存.但是当清零的时候,如果触发器不是同步进行,那么所需要的时间就会产生差异,进而会导致由于时间的延时触发器没有真正的进入清空状态,这个时候信号已经没有了,最终导致结果的不成功产生出错.所以反馈清零法虽然实现简单,但是可靠性比较差.

反馈置数法在负脉冲的处理上,给予一个带有宽度的信号,进而会使得计数器的可靠性比反馈清零法高.

级联法主要是先级联去扩大进而根据清零和置位用来获得任意进制,虽然其应用比较广泛,但可靠性不如反馈置数法.

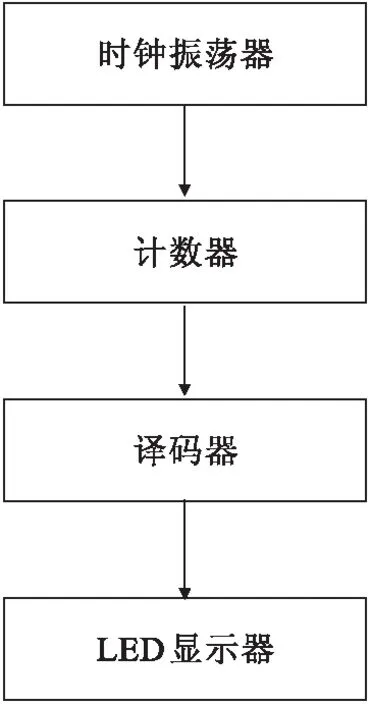

3.4 60 s减法定时器的设计

图9为60 s减法定时器的设计原理图.其设计原理为:时钟振荡器采用555多普振荡器或门电路构成的多谱振荡器实现,其主要用来产生时间的标准信号,其精确程度取决于时间的标准信号的频率和稳定性,用555定时器实现“秒”信号的产生器;计数器由74LS90采用“清零”方法组成六十进制的“秒”计数器,且用BCD码表示;清零方法主要是适用于有异步置零输入端的集成计数器.其基本原理是不管它的输出是一个什么状态,只要在输入的端口加入一个有效的电平电压,那么输出就会立刻从之前的状态回到“0000”状态;译码驱动电路将计数器输出的8421BCD码转换为数码管需要的逻辑状态,而且为七段数码管的正常稳定提供正常的工作电压和电流,译码器采用74LS48为驱动芯片,共阴极七段数码管作为文中的显示器.

图10为60 s倒计时定时器的程序流程图.流程图主要包括开始、显示60 s电路、中断50 s溢出电路、跳转到loop1,倒计时开始和结束.其中,中断50 s溢出电路中,当符合条件的时候进行循环执行20次,当倒计时到0之后则返回主程序,进而进行余下的程序到最终结束.

图9 60 s减法定时器设计原理图

图10 60 s倒计时定时器的程序流程图

4 结语

本文介绍了利用数字中规模集成电路的控制端功能实现任意进制计数器的方法.首先,针对中规模集成电路的原理进行分析总结;进而,引入本文的重点——芯片的选择,即计数器74LS90,通过研究其引脚的功能,来实现反馈清零法、反馈置数法和级联法,并在其中应用各种实例进行验证分析;最终,对反馈清零法、反馈置数法和级联法的优缺点进行描述,得出反馈置数法的可靠性能比较良好.本文得到一个利用集成计数器的清零端和置位端实现归零,从而构成按自然态序进行计数的N进制计数器的方法.