基于容忍单粒子效应的集成电路加固方法研究

徐亚伟

(1.安徽工程大学电气工程学院, 安徽芜湖241002;2.安徽机电职业技术学院, 安徽芜湖241000)

引言

宇宙高能粒子引发的单粒子翻转(Single Event Upset,SEU)是造成存储元件产生软错误的主要因素。集成电路技术的飞速发展使得晶体管尺寸更加小巧、工作电压愈加低,导致每个节点上存储的电荷更少,而电路的工作频率却不断增加。晶体管本身结构上的这些变化因素加剧了软错误,并成为影响电路可靠性的主要因素。粒子入射轨迹上的电子-空穴对就会被电极收集,从而形成瞬时电流,如图1所示。当不存在电场时,电离的电子-空穴对不会对电路的正常工作产生影响。如果发生在存储元件中,晶体管漏极与衬底之间的电荷漂移将导致存储元件的正常逻辑状态发生改变,从而发生单粒子翻转[1],主要表现为某一个节点的数据位发生翻转,而在较坏的情况下可能会导致某两个节点的数据位发生翻转(Double Node Upset,DNU)。另一方面,上述情形如果发生在组合电路块中,较大的瞬时电流可能会使逻辑门的输出电压发生瞬态的变化,从而发生单粒子瞬态(Single Event Transient,SET),在逻辑门的输出端表现为瞬时的SET脉冲,而在较坏的情况下可能会在多个逻辑门的输出端产生瞬时的脉冲(Single Event Multiple Transient,SEMT)。

关于容忍单粒子效应的集成电路抗辐射加固技术,国内外已经提出了很多方案。但许多设计仍然会因为受到高能量粒子轰击而引发软错误,不适用于高可靠系统。针对现有容忍单粒子效应的锁存器结构无法同时容忍SEU、SET,以及未考虑电荷共享导致的DNU问题,提出了本文方案,即一种高可靠性的同时容忍SEU、SET和DNU的锁存器加固结构SRDT-SET。基于空间和时间冗余原理,该锁存器结构采用了多个输入分离的施密特触发器来构建高可靠性数据存储反馈环,达到有效容忍SEU和DNU的目的,同时通过内嵌的多个施密特触发器,有效增强了SET脉冲的过滤能力。

图1软错误模型

1单粒子效应的建模方法

1.1器件级模型

器件级模型通过器件模拟来体现。器件模拟是在特定边界条件下对半导体物理基本方程进行求解,从而得到器件内部物理量重分布的过程。早在1984年,IBM学者就通过器件模拟的方法发现了粒子入射的漏斗效应[2]。目前,一种广为采用的研究单粒子效应电荷收集的方法就是器件模拟。

通过器件模拟,诸如器件的各端电压和电流在粒子入射后的变化情况是可以计算得到的。器件模拟时会根据半导体器件特征尺寸的不同而取不同的物理模型,目前广为采用的是漂移-扩散模型。此外,如果加入特定的描述方程,还能够对碰撞电离、粒子散射等微观效应进行模拟。

1.2电路级模型

在电路级的单粒子效应建模中,IBM公司的Freeman提出了单指数电流源模型[3]。

(1)

式中:Q为入射粒子沉积电荷量,τ为脉冲波形时间常数,其取值和电路工艺尺寸息息相关。

另一方面,Messenger提出了双指数电流源模型[4],并且被广泛应用[3,5-7]。该模型通过将一个双指数电流注入到电路的某个节点,实现对单粒子效应的模拟。双指数电流源模型为:

Iinj(t)=I0(e-t/τ1-e-t/τ2)

(2)

其中:I0为入射粒子产生的最大电流,它的取值为Q/(τ1-τ2);Q为收集的沉积电荷总量;τ1与τ2分别为电荷收集时间常数与电荷通道建立时间常数,是工艺相关的常数因子。

2相关加固锁存器结构

2.1标准静态锁存器

标准静态锁存器主要由两个传输门TG1、TG2,以及三个反相器inv1、inv2、inv3组成[8],如图2所示。D为输入端、Q为输出端,CLK为时钟信号,CLKB为时钟信号的反信号,n1和n2为两个内部节点。标准静态锁存器存在的问题就是不能容忍单粒子效应。

图2标准静态锁存器

2.2空间冗余技术

空间冗余基本思想是增加冗余的硬件,使锁存器结构具有更多的冗余节点或冗余子模块进行单粒子效应的容忍[9]。TMR锁存器主要由三个标准静态锁存器和一个表决器组成[10],如图3所示。通常三个标准静态锁存器都输出或保存一致的逻辑值,经过表决器后仍是正确的逻辑值。在出现错误的情况下,有一个标准静态锁存器出现错误,但表决后仍然可得到正确的逻辑值。

图3TMR锁存器

2.3施密特触发器

施密特触发器具有过滤SET脉冲的作用并能够将正常的输入信号进行反相输出[11],如图4所示。当D端有低电平数据,M6打开。如果D端到来一个0-1-0型SET脉冲,即SET正脉冲,当短暂的高电平到达D端后,M3和M4会被短暂打开,因为N2点被预先充电为高电平,所以需要部分时间下拉为低电平。在N2被下拉为低电平期间,SET正脉冲的短暂高电平可能已经传输完毕,所以Q端还没有来得及下拉为低电平,即Q端一直为高电平。由此可见,D端点到达的正常低电平数据中即使附带了SET正脉冲干扰信号,输出端一直为高电平,即SET脉冲被过滤掉,并且输入信号被反转,此即为施密特触发器的特有功能。

图4施密特触发器

2.4时间冗余技术

施密特触发器使用了时间冗余技术,也就是通过增加延迟进行SET脉冲的容忍[12]。但是施密特触发器增加的延迟有限,所以只能过滤比较窄的SET脉冲。

由图5可知,该锁存器只是将图2中标准静态锁存器的inv1替换为施密特触发器。因为施密特触发器具有SET脉冲过滤功能,并且它处于透明模式下的数据通路上,所以该锁存器在透明模式下能够过滤SET脉冲。因为施密特触发器的各个节点临界电荷比较大,比普通的反相器更具备一定的抗SEU能力,所以该锁存器在锁存模式下具备一定的SEU容忍能力[13]。

图5ST锁存器

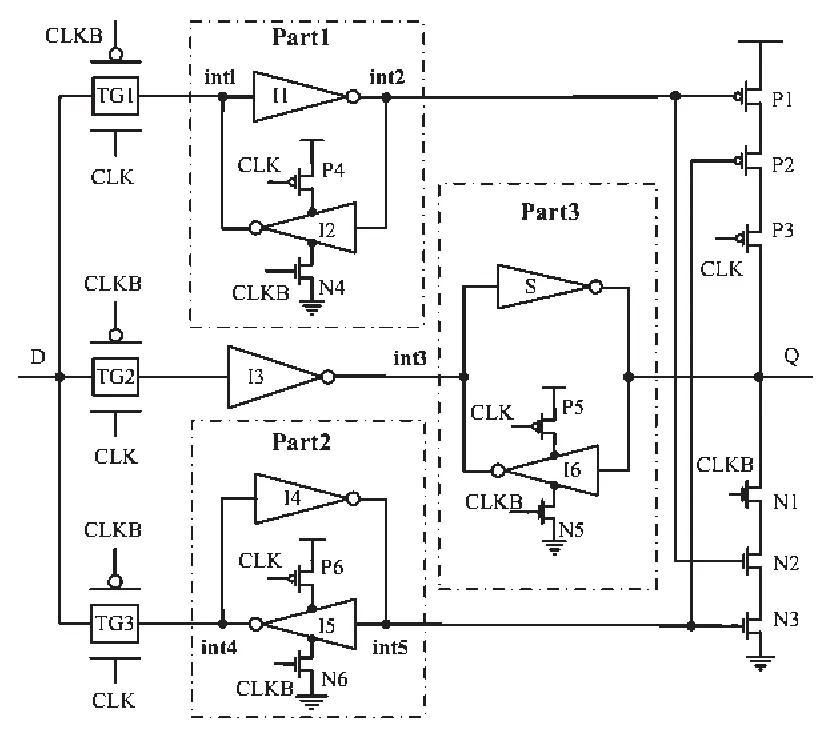

2.5LCHR锁存器

LCHR锁存器主要由三个锁存模块Part1、Part2和Part3,以及一个钟控的C单元构成,如图6所示[14]。其中,器件S为能够过滤SET脉冲的施密特触发器。在透明模式下,数据路径D-TG2-I3-S-Q被开启,并且Part1和Part2以及C单元被充电,但因为C单元的钟控作用,输出端Q的数据并不会由C单元的输入来决定;因为Part1、Part2和Part3中的钟控作用,它们的反馈环还没有建立。因为S能够过滤SET脉冲,所以该锁存器过滤SET脉冲。在锁存模式下,Part1、Part2和Part3的反馈环被建立起来,并且输出端Q由C单元的两组输入决定,输出端Q还由Part3决定。

图6LCHR锁存器

3容忍单粒子效应的锁存器结构设计

3.1输入分离的施密特触发器

输入分离的施密特触发器是将原有施密特触发器的单个输入拆分为两组输入,每一组输入都是分别连接到一个PMOS晶体管以及一个NMOS晶体管的栅极[15-17],如图7所示。从另外一个角度来看,输入分离的施密特触发器是将原有C单元的内部节点分别插入一个PMOS晶体管和一个NMOS晶体管,并且PMOS晶体管和NMOS晶体管的源极分别接入GND和VDD,然后将插入的两个晶体管的栅级同时与输出端进行互相连接,由此构成输入分离的施密特触发器。

图7输入分离的施密特触发器

3.2SRDT-SET的电路结构

本文所提出的电路结构该结构主要由三个传输门TG1、TG2、TG3、虚线框部分所示的三个输入分离的施密特触发器CST1、CST2、CST3,以及两个反相器inv1和inv2构成,如图8所示。右上角的反相器inv1为钟控反相器。CLK和CLKB分别是时钟信号和时钟信号的反信号,D和Q分别是输入端和输出端,N1到N5为五个内部节点。

图8提出的SRDT-SET锁存器

3.3SRDT-SET的容错原理

在透明模式下,三组输入分离的施密特触发器CST1、CST2和CST3都能够过滤SET脉冲。假定输入端D的正常信号为低电平,N1、N2均为低电平,即CST1的两组输入均为低电平,所以CST1中的两个PMOS晶体管都被打开,CST1的输出N4就被上拉为高电平。因为N4为高电平,即inv2的输入为高电平,所以inv2中的NMOS晶体管被打开,inv2的输出N3就被下拉为低电平。因为N2、N3均为低电平,即CST2的两组输入均为低电平,所以CST2中的两个PMOS晶体管都被打开,CST2的输出N5就被上拉为高电平。因为N4、N5为高电平,即CST3的两组输入均为高电平,所以CST3中的两个NMOS晶体管都被打开,CST3的输出Q就被下拉为低电平。到达D的低电平信号就被顺利地传输到输出端Q,并且SRDT-SET锁存器中所有节点的状态都被确定下来。

在锁存模式下,N2和Q节点完全等效。从图7可知,共有N1、N3、N4、N5、Q五个SEU敏感节点。在考虑DNU的情况下,共有10个DNU敏感节点对。在考虑SEU的情况下,当N1发生SEU,因为CST1中C单元的作用,错误不会输出到N4,并且因为inv1的输入N5没有发生错误,所以N1能够通过inv1进行恢复。同理,当N3也能恢复。当N4节点发生SEU,因为CST3中C单元的作用,错误不会输出到Q;错误虽然会通过inv2输出到N3,但是因为CST2中C单元的作用,错误不会输出到N5,因为CST2的另一组输入Q没有发生错误;N5没有发生错误,那么inv1的输出N1也没有发生错误,即CST1的两组输入都没有发生错误,所以N4能够通过CST1的输入进行恢复。同理,N5或者Q节点也能恢复。可见,五个SEU节点中每一个发生SEU都能进行恢复。

4仿真实验与结果分析

4.1SRDT-SET的仿真实验设计

分别在CLK为高电平的1 ns~2 ns、3 ns~4 ns、5 ns~6 ns期间,向输入端D分别注入了SET正脉冲、负脉冲,如图9所示;负脉冲、正脉冲,如图10所示;正脉冲、负脉冲,如图11所示。由于1 ns~2 ns期间注入的SET脉冲宽度比较小,没有被传输到CST1的输出N4和CST2的输出N5,所以也不会被传输到CST3的输出Q。在3 ns~4 ns期间注入的SET脉冲宽度增大,所以正负脉冲都被传输到N4,有部分原始的D端正脉冲被传输到N5,CST3将这个部分脉冲过滤掉,所以也不会被传输到Q。在3 ns~4 ns期间注入的SET脉冲宽度更大,所以正负脉冲都被传输到N4,也被传输到了N5。由于CST3对脉冲的过滤能力是有限的,所以原始的D端正脉冲被传输到了Q,而负脉冲被过滤掉了。

图9注入SET的SRDT-SET锁存器工作波形

4.2鲁棒性与开销对比

本文结构与其他锁存器结构的仿真对比结果见表1。由表1可知,只有本文提出的锁存器能够自恢复,能够部分容忍DNU。在15个DNU敏感节点对中,LCHR锁存器只能容忍7对,容忍能力达到7/15=46.7%;而本文提出的结构在10个DNU敏感节点对中,同样能容忍7对(自恢复),容忍能力达到7/10=70%,并且3个DNU敏感节点对在输入分离触发器的作用下,具有比较大的临界电荷,因此与LCHR锁存器相比,本文的结构DNU过滤能力更好。在容忍SET方面,本文的结构中包含多个输入分离的施密特触发器,最大可过滤的SET宽度达到84.6 ps,并且SET过滤能力达到87.3%。在面积、功耗和延迟开销方面,使用了30个晶体管,比LCHR结构少了6个,并且本文结构的功耗和延迟也都比LCHR结构小,但是本文的结构却能够在发生SEU后自恢复、DNU容忍能力更好,SET过滤能力更强。总之,综合来看,与其他几款锁存器结构相比,本文的结构具有一定的优越性。

图10注入SEU的SRDT-SET锁存器工作波形

图11注入DNU的SRDT-SET锁存器工作波形

表1与其他锁存器结构的对比结果

5结束语

本文主要针对SEU、SET,以及电荷共享导致的DNU几种单粒子效应,提出了一种高可靠性的同时容忍SEU、SET和DNU的锁存器加固结构SRDT-SET。该锁存器结构同时采用空间冗余和时间冗余技术,使用了多个输入分离的施密特触发器来构建高可靠性数据存储反馈环,达到有效容忍SEU和DNU的目的,同时通过内嵌的多个施密特触发器,有效增强了SET脉冲的过滤能力。使用HSPICE仿真实验结果表明,与相关文献提出的结构相比,本文提出的锁存器结构不但能够对SEU自恢复、容忍的SET脉冲宽度更宽,并且能够有效容忍DNU,而与同时容忍SEU、SET和DNU的LCHR锁存器结构相比,其面积、功耗和延迟综合开销不大。