一种片式T/R组件的热电协同设计方法研究

,,

(中国电子科技集团公司第三十八研究所国家级工业设计中心,安徽 合肥 230088)

0 引言

新型有源相控阵雷达系统对组件提出高密度集成设计要求[1- 3],在有限的空间内往往集成有数千至上万个片式T/R组件,使得组件工作时的热控问题愈发突出[4- 5],主要表现为:单个T/R组件内多个收发通道上的多个芯片会产生密集的热量;较小的空间内高密度集成了多个T/R组件,热流密度大。因此,对于高频段高集成的片式T/R组件,温度场的变化将对其电讯性能产生不可忽视的影响,包括芯片S参数、收发通道驻波与增益乃至整个天线系统的电讯指标,而变化的电磁特性又将重新影响T/R组件的热耗分布。

目前,T/R组件的设计模式是以电讯专业牵头、结构和热控专业配合的串联设计[6],各专业使用的模型以及仿真数据难以匹配传递,难以进行热- 电磁场的协同仿真设计,无法满足高集成片式T/R组件的设计需求。

文献[7]研究了一种小型Ku波段瓦片式T/R组件设计,采用组件紧贴冷板、内部有源芯片紧贴组件壳体的方式解决片式T/R组件的散热问题,该方法属于对已定电讯方案的被动设计,并未从总体设计方面对电讯和结构进行协同设计,而且在很小的空间内,冷板的散热效果有限,难以满足高集成T/R组件的热控要求。西安电子科技大学等针对雷达天线阵面开展了机电耦合机理以及多学科优化分析研究[8- 10]。而针对高密度集成片式T/R组件,文献中尚未见到明确的多学科协同设计方法。

本文提出一种片式T/R组件的热- 电磁协同仿真设计方法,首先,通过提取T/R组件的结构和电磁单学科模型特征进行混合建模获得T/R组件热- 电磁协同分析模型,在此基础上对多学科数模进行电磁和热性能耦合仿真,获得真实电磁场的组件温度分布并评估真实温度下的电讯指标变化,通过快速修改模型并迭代分析直至T/R组件的热、电磁性能全部满足设计要求。

1 T/R组件多学科建模

片式T/R组件一般设计多个收发通道,结构专业负责壳体、盖板、通道隔筋等设计,建模采用Pro/E等结构三维数模软件;电讯专业提供电路板、收发和控制网络、芯片、垂直互联连接器等设计,建模采用Protel等电子行业二维设计软件。不同的专业、建模工具和模型维度均阻碍了T/R组件多学科建模及协同设计。

本文对T/R组件的结构和电讯特征进行提取和简化,简化方法如下:

a. 保留热耗较大的射频网络,忽略热耗较小的低频控制网络。

b. 将射频网络中的EDA元素(带状线、焊盘、金丝等)组合成可参数化建模的形状特征(如网络端点、网络合成节点)。

c. 简化电路板中隔离孔(隔离电磁波)的数量,忽略间距小于0.1倍介质中波长的隔离孔。

d. 将各类过孔(隔离孔、导电孔、散热孔)的分布简化为圆环阵列、矩形阵列及组合阵列,可以参数化建模。

采用ANSYS SCDM软件对提取的模型特征进行混合建模,该软件可以进行几何参数快速定义、并将模型数据实时传递给热和电磁仿真软件。通过热、电磁特征混合建模方法,获得多通道片式T/R组件多学科数模,如图1所示。

图1 某片式T/R组件多学科数模

与热相关的模型特征包括壳体、盖板、电路板、芯片及其下方焊层;与电磁相关的模型特征包含电路板、射频网络、连接器、隔筋。在后文的热- 电磁协同设计中将根据分析需求,对部分模型特征进行抑制。

2 T/R组件多学科设计方法

2.1 设计分析流程

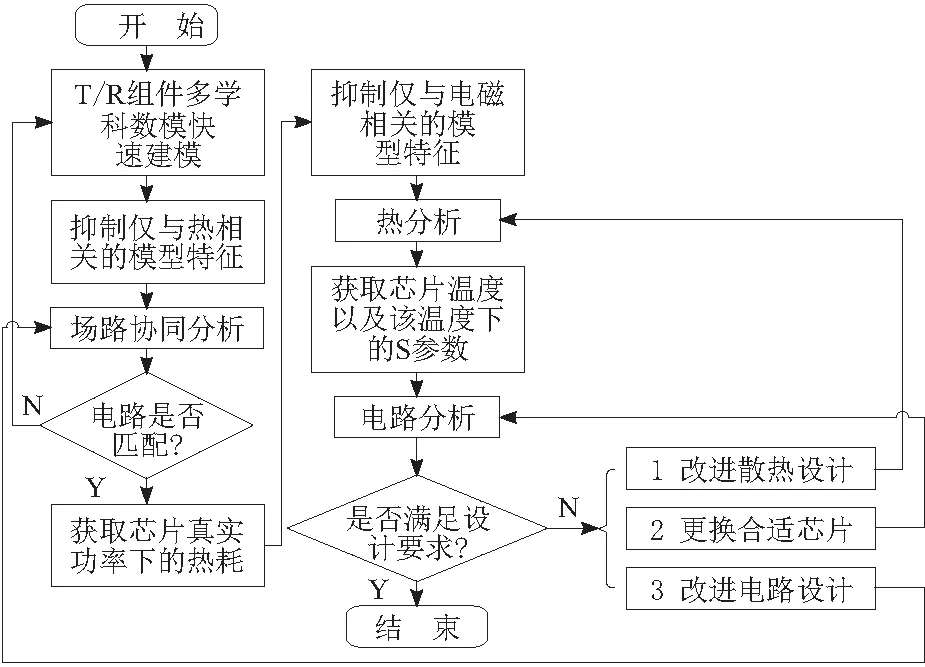

片式T/R组件的热- 电磁协同设计分析以多学科数模为基础,展开电磁和热的交互迭代分析,不同物理场的仿真结果数据进行匹配传递,具体方法流程如图2所示。

图2 T/R组件热- 电磁协同设计方法

2.2 初始有源电路匹配设计

在分析流程中,首先对T/R组件在某个设计温度下的初始有源电路进行匹配设计,包含对无源电磁场和有源电路的传输特性等参数进行分析,技术指标包括端口驻波比(VSWR)、插损(S21)等。

在SCDM软件中将T/R组件多学科数模中仅与热相关的模型特征(如壳体、芯片实体)进行抑制,导入电磁分析软件HFSS和电路软件Circuit中,进行电磁场和电路的协同设计,获得匹配后电路在真实发射和接收激励下芯片和传输线的功率。

2.3 热- 电磁协同仿真

在SCDM软件中将T/R组件多学科数模中仅与电磁相关的模型特征(如连接器、射频网络)进行抑制,导入热分析软件中,并将有源电路中芯片和传输线的功率转化为热耗,作为T/R组件热仿真的输入,获得组件壳体、电路板、芯片(尤其是有源芯片)在真实电磁波激励下的温度分布。

本文基于功率谱反演方法得到各向异性大气湍流相位屏,模拟了贝塞尔高斯涡旋光束在其中的光强分布、光强闪烁和光束抖动的影响,并与已有在轴闪烁的理论值进行比较.研究了不同参数下强度分布、闪烁效应和抖动效应的变化规律.

更新组件电路中有源芯片在真实温度下的S参数,进行电路重分析,获得更新后各收/发通道的VSWR和S21等指标。如果指标满足电讯设计要求,则完成T/R组件的多学科设计,否则,按照如下优先级方法进行结构或电讯特征的改进设计:

a. 改进壳体结构散热设计,重新生成数模并迭代热- 电磁协同分析,使得T/R组件在真实温度下满足电指标要求。

b. 在改进散热设计效果有限且芯片有备选的情况下,可以更换工作温度范围更宽的有源芯片,迭代电路分析。

c. 最恶劣情况下,需要改进初始电路设计,优化元器件的功率分布同时调整散热路径,进行整个设计流程的迭代。

3 仿真案例

3.1 数模及参数

对某宽频带4通道片式T/R组件进行热- 电磁协同设计,多学科数模如图1所示。

模型的几何初始参数如壳体尺寸、电路板厚度、带状线宽度、芯片焊层厚度等采用参数化建模,更改这些参数可实现模型快速重构。

根据2.1节中的设计分析流程,在ANSYS workbench(WB)软件平台中建立该T/R组件的热- 电磁协同仿真流程,如图3所示。部分数据之间的传递在软件中尚不支持,通过编写脚本完成。

图3 WB中实现T/R组件热- 电磁协同仿真

3.2 场路建模及分析

图4 HFSS中T/R组件电磁分析模型

模型网格划分在导体传输路径上进行加密,考虑壳体内部真实的腔体效应,将多层电路板包围在与壳体内腔等同体积的空气盒子内,激励端口包括连接器表面的波端口和电路内部的集总端口。

将电磁分析结果与常温下的芯片S参数模型在电路软件Circuit中集联,形成T/R组件有源电路。接收和发送通道在模型中用开关切换。本案例中模拟了单个通道的收发电路,其他通道的芯片端口用匹配负载连接。

通过线性频率分析,给出完整电路的散射系数,如图5和图6所示,总端口的VSWR和S21均满足指标要求。

通过谐波平衡分析获得各个波端口的实际激励,再推送给T/R组件电磁模型,得到实际激励下电路内部各芯片上的功率。在本案例中,功率较大的芯片包括功放芯片、多功能芯片以及低噪放芯片。

图5 T/R组件有源电路的插损

图6 T/R组件总端口的驻波比

3.3 热- 电磁分析结果

将数模中仅与电磁分析相关的模型特征,包括连接器、射频网络等进行抑制,导入Static- State Thermal模块中建立T/R组件的热分析有限元模型,如图7所示。

图7 T/R组件热分析结构模型

查阅芯片效率,将3.2节中获得有源芯片功率转化为热耗并自动导入到芯片实体结构中作为T/R组件热分析的载荷输入。

根据实际散热方式施加边界条件,本案例中用温度边界模拟冷板散热,获得T/R组件在真实激励下的内部结构的温度分布,如图8所示。芯片在真实激励下的最高温度达到106 ℃。

图8 T/R组件内部结构温度分布

3.4 温度对电指标的影响及改进

查阅芯片知识库,提取各个有源芯片在实际温度下的S参数,并在电路模型中进行自动更新,迭代电路分析获得更新后的电指标参数,如图9所示的总端口的驻波比。

图9 温度变化对T/R组件端口VSWR的影响

本案例的T/R组件的单通道功率和热流密度有限,因此,虽然有源芯片的S参数从常温到实际温度下发生变化,使得T/R组件的端口驻波在部分频率点接近设计上限,但并未超过设计阈值(VSWR<1.5)。从保守设计考虑,可以改进功放芯片下方的导热柱设计。

4 结束语

提出了一种片式T/R组件的多学科建模方法并基于该模型实现组件的热- 电磁协同设计,该方法具备可根据参数快速重构组件电磁和结构特征、多物理场仿真数据匹配传递等优点,可以实现T/R组件的快速、全性能优化设计。

以ANSYS Workbench软件为平台,将T/R组件的热- 电磁协同设计方法流程化,通过各个软件模块的交互分析完成了某片式T/R组件的多学科设计,验证了本文方法的可行性和有效性。