一种宽带接收机射频前端芯片设计

竺 磊,吴俊杰,万川川,张 浩

(南京电子技术研究所,南京210039)

1 引言

雷达被称为战争中的千里眼,是电子战和信息战的核心装备。雷达系统未来的发展方向和趋势是多功能化、小型化和智能化,相应的对芯片的设计也提出了更高的要求,要求芯片覆盖更广的工作频率范围,具有更高的集成度,更大的动态范围。

对电路性能和工作频段要求较高的射频集成电路一般采用GaAs工艺,因为该工艺能够提供较大的电流驱动能力、较低的插入损耗和更好的噪声系数,但是GaAs工艺成本较高,并且无法提供大规模的数字电路设计,限制了芯片的集成度。CMOS工艺具有低廉的成本,可实现数字模拟电路的大规模集成,但是射频频段较差的性能使得该工艺难以成为射频集成电路的合适选择。近些年发展和普及的SiGe BiCMOS工艺,由于良好的性能与集成度以及相对适中的价格已逐渐成为射频集成电路设计的合理选择。

无线接收机的射频前端必须完成两个主要操作:对天线接收到的信号进行放大;将放大后的信号下变频到较低频率。由于射频前端对整个接收机的影响最大,对其性能要求也最高[1]。

2 接收机结构

传统无线接收机射频前端的电路架构主要包括超外差、零中频[2-3]和低中频结构[4]。另外还有其他几种接收机结构在实际应用中也经常遇到,如超再生式接收机[5]、宽带中频接收机[6]、镜像抑制接收机[7]和亚采样接收机[8]等。由于超外差接收机可以提供优良的性能,目前依然是应用最广泛的一种接收机结构;在对接收机性能要求很高的应用中,超外差结构几乎是唯一的选择。但是超外差式接收机的主要缺点是依赖多个外接滤波器。

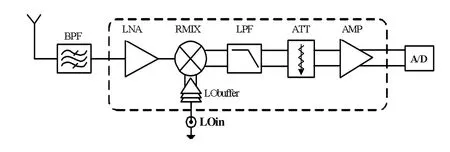

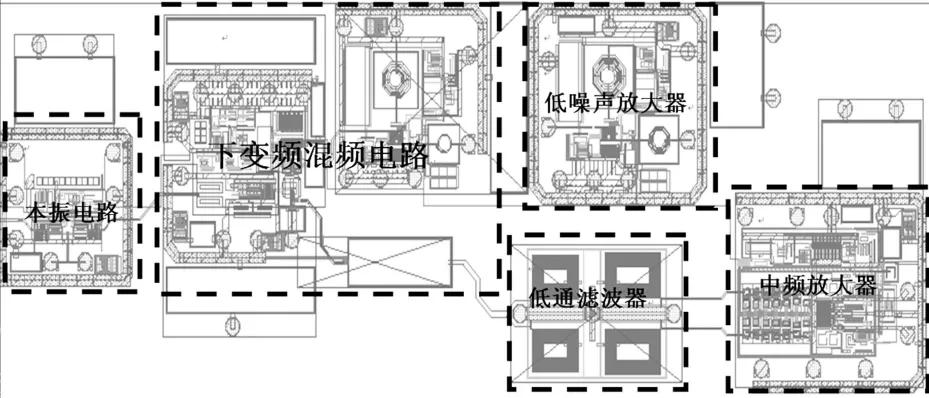

结合雷达系统的应用要求,在超外差式接收机结构的基础上,将中频低通滤波器集成在片内,可提高集成度,降低产品成本,提高系统的稳定性。所设计的射频前端芯片具体结构如图1所示。虚线框内为芯片内电路,LNA前级通过外接的射频带通滤波器连接到天线。如果对噪声有更高的要求,片外还可以级联一个砷化镓的低噪声放大器。本振信号由片外提供,中频放大器的输出给模数转换器采样。

图1 射频前端芯片整体结构框图

如图1所示,射频前端芯片集成了低噪声放大器(LNA)、下变频混频器(RMIX)、本振缓冲电路(LObuffer)、低通滤波器(LPF)、中频衰减器(ATT)和中频放大器(AMP)。LNA的后级直接片内级联RMIX,片外本振信号通过LObuffer电路后驱动混频器的开关对管,LObuffer电路的主要作用是将本振信号放大整形为方波,以此来优化混频器的线性度和噪声性能。混频器输出与中频衰减器相连要经过低通滤波器,采用五阶的巴特沃兹LC滤波器结构,其中电感为自行建模设计,实现了片内集成,提高了集成度,降低了应用成本。中频放大器电路采用了三阶项抵消技术,实现了较高的线性度。

所设计的接收机射频前端芯片覆盖0.2~4GHz的频率范围,采用台积电(TSMC)的0.18-μm SiGe BiCMOS工艺制造,流片后测试的结果和仿真基本一致。实测结果显示,低噪声放大器的噪声系数3dB、功率增益15dB,下变频混频器的单边带噪声系数12dB、电压转换增益6dB、输出1dB压缩点8dBm,低通滤波器的带内插损1dB、3dB带宽是550MHz,中频放大器采用了三阶项抵消技术,提高了电路的线性度,实现了功率增益20dB、输出三阶交调点高达40dBm、输出1dB压缩点20dBm。芯片在5V电压下工作,静态工作电流220mA。

3 电路设计与实现

3.1 低噪声放大器

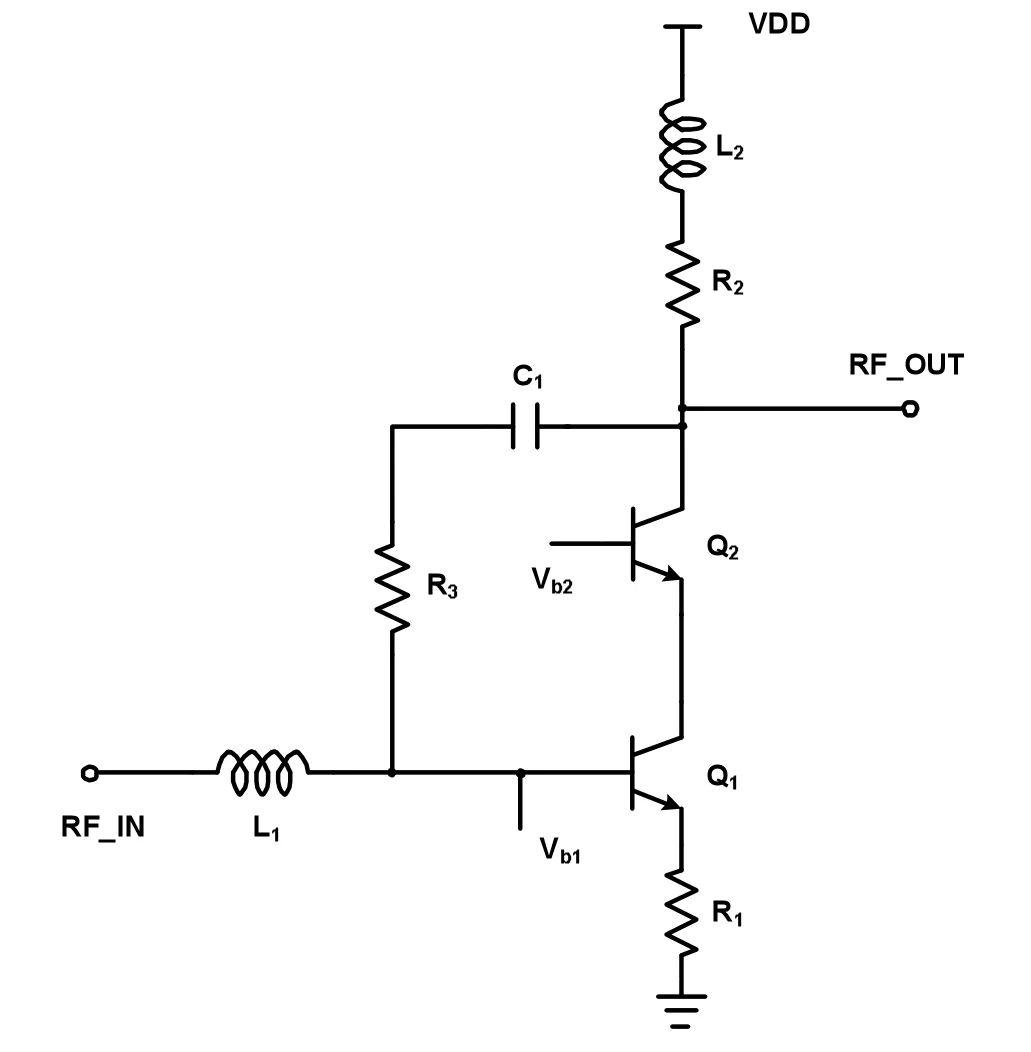

低噪声放大器的电路是共发射极的单端cascode放大器,采用适合宽频带的反馈结构,如图2所示。图中Vb1和Vb2分别为三极管Q1和Q2的偏置电压,片内的基极电感L1用于抵消各种寄生电容的影响,实现50Ω阻抗匹配。电容C1和电阻R3通过反馈实现宽频带范围内的输入阻抗和输出阻抗匹配。电阻R1降低了器件参数变化对放大器性能的影响,并提高放大器的线性度。大尺寸的三极管Q1偏置在30mA电流,适当牺牲了功耗来满足噪声和增益的性能。Cascode三极管Q2改善放大器的反向隔离度,能减小混频器到低噪放输入的本振泄露。片内电感L2和电阻R2串联作为负载,保证了频带内的增益平坦度。

图2 低噪声放大器电路示意图

3.2 接收混频器

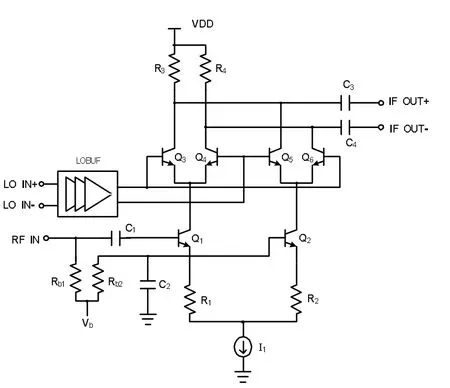

接收混频器的电路是采用双平衡吉尔伯特结构的有源混频器[9-10],如图3所示。采用双平衡结构能够对本振泄露起到很好的抑制作用,但前一级的低噪声放大器的输出是单端形式,因此将双平衡混频器的一个输入端通过电容C2接地,另一端通过电容C1与低噪声放大器输出相连接,实现了单端到差分的转换。片外的差分本振信号经过本振缓冲电路整形为方波,并以300mV的电压幅度驱动混频器的开关对管,同时本振缓冲电路给混频器提供直流偏置。

图3 接收混频器电路示意图

3.3 低通滤波器

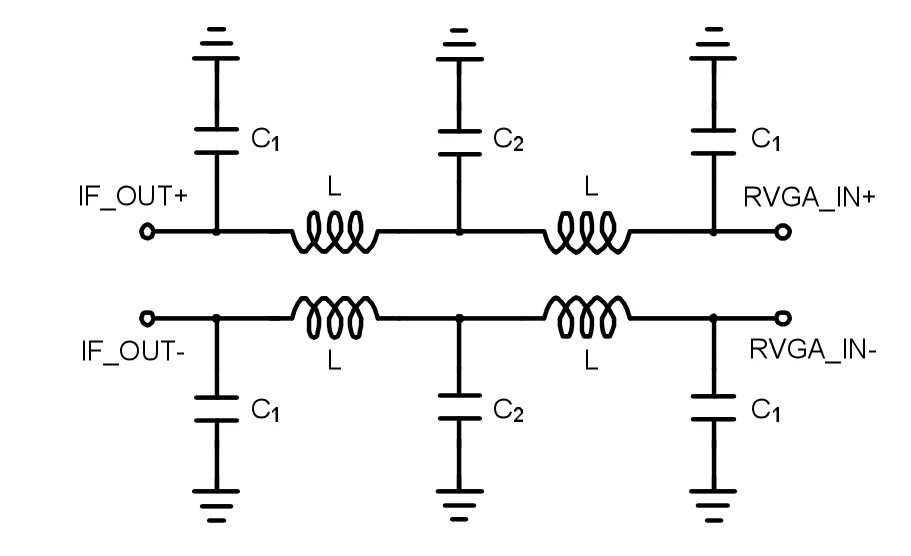

低通滤波器选用的是一个五阶最大幅度平坦型的巴特沃兹(Butterworth)低通滤波器[11],如图4所示。选用参数为:电感L=35nH,电容C1=2pF,电容C2=6.2pF,-3dB带宽550MHz,带内插损≤1.5dB,50~400MHz带内增益起伏≤1.5dB。

图4 五阶LC低通滤波器电路示意图

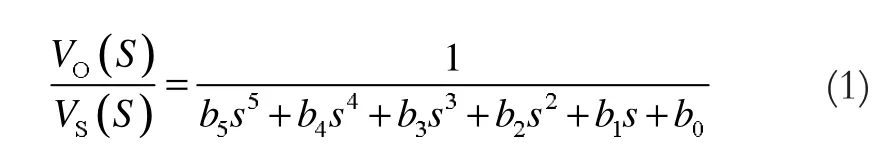

根据五阶LC低通滤波器的简化电路图,可以推导出传递函数:

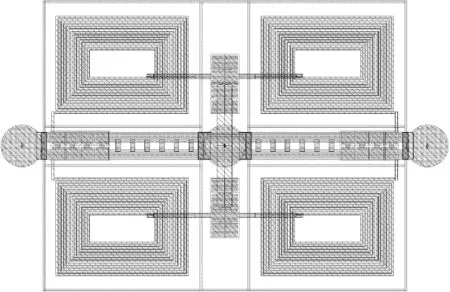

滤波器电路中的长方形片上螺旋电感为自行建模设计,版图照片如图5所示。电感线圈采用顶层金属绕制,金属线宽度为3.6μm,线间距为1.9μm,方块电阻为8.6mΩ/sq,衬底为200μm厚的P型硅,电感线圈圈数是13,最外层线圈大小为270μm×230μm。

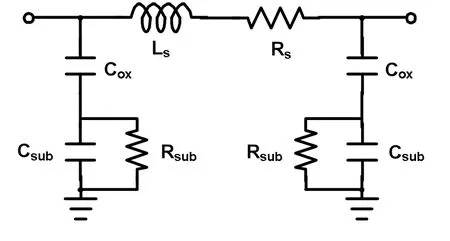

片上螺旋电感的等效电路[12]如图6所示。LS代表电感的电感量,RS代表金属线电阻损耗,Cox代表金属线与衬底之间的氧化层电容,Csub代表金属线与衬底之间的耦合电容,Rsub代表由金属线与衬底之间的电场耦合所引入的损耗。利用等效电路在ADS中拟合得出 LS、RS、Cox、Csub和 Rsub的值分别为34.8nH、20Ω、114fF、52fF 和 176Ω。

图5 低通滤波器版图照片

图6 电感等效电路模型

3.4 三阶项抵消中频放大器

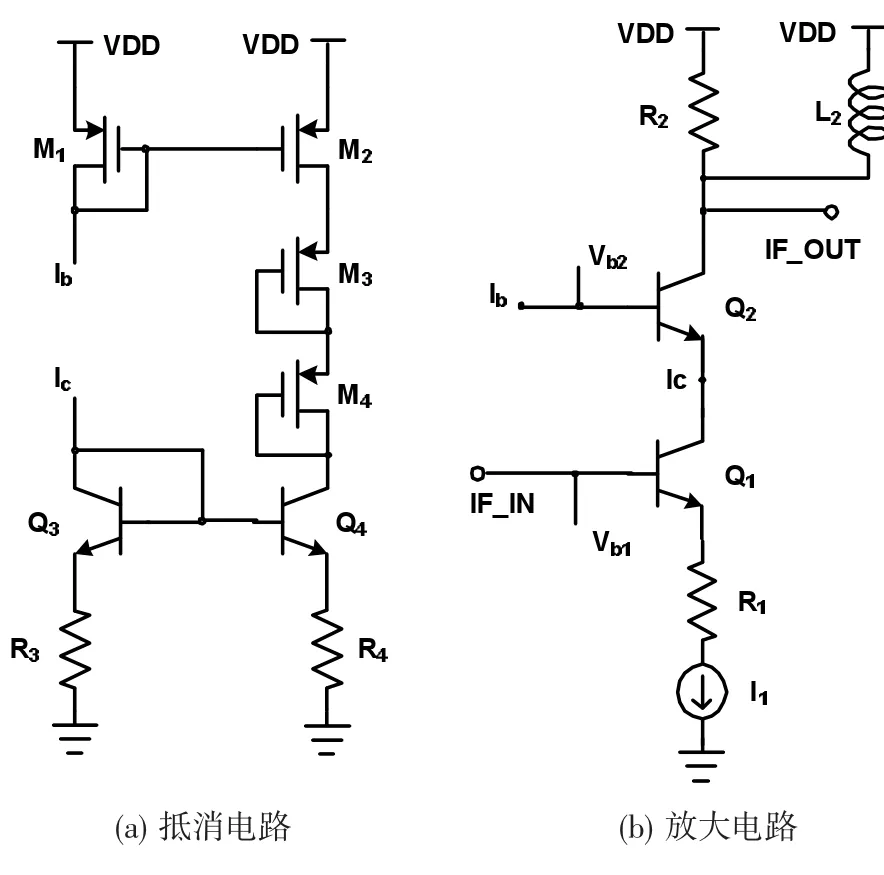

如图7所示,中频放大器采用了共发射极的差分cascode电路结构。Cascode三极管采用了三阶项抵消技术,提高了电路的线性度。

图7 中频放大器三阶项抵消电路示意图

图7(a)是抵消电路,图7(b)是差分放大电路的单端示意图。图7(b)中的Q2作为cascode三极管,集电极就是放大器电路的输出,输出信号的电压峰峰值能达到2V,由此可见cascode三极管本身的线性度严重制约了整体放大器电路的线性度。在本项研究提出的三阶项抵消电路结构中,三极管Q2的集电极相对基极和衬底各自形成一个PN结,而抵消电路的核心思想就是利用这两个PN结产生的非线性相互抵消,从而提高线性度。具体抵消电路如图7(a)所示,Q2管的集电极-基极PN结产生的三阶项交调电流iIM3,从基极Ib处抽取到抵消电路中,抵消电路改变iIM3的极性,并通过适当比例在Ic处反馈回放大电路中,从而抵消集电极-衬底PN结产生的三阶项。

4 版图设计和实测结果

射频前端芯片基于TSMC的0.18-μm 1P6M(一层多晶硅6层金属)BiCMOS工艺设计流片,整体版图如图 8所示,面积约为 1500μm×4500μm,各电路模块均已标注在图中。

图8 接收机芯片版图布局

芯片封装形式采用球栅阵列倒装芯片(简称BGA Flip Chip)。芯片封装好后,焊接在测试板上测试电路性能。版图中低噪声放大器、混频器和中频放大器都放置了可以单独测试的电路模块,并且分别单独测试,测试中需要外接巴伦,用于产生差分输入信号并将差分输出转换为单端信号。测试结果显示,低噪声放大器实现了噪声系数3dB、功率增益15dB;下变频混频器实现了单边带噪声系数12dB、电压转换增益6dB、输出1dB压缩点8dBm;低通滤波器实现了带内插损1dB、3dB带宽550MHz;中频放大器实现了功率增益20dB、输出三阶交调点40dBm、输出1dB压缩点20dBm。

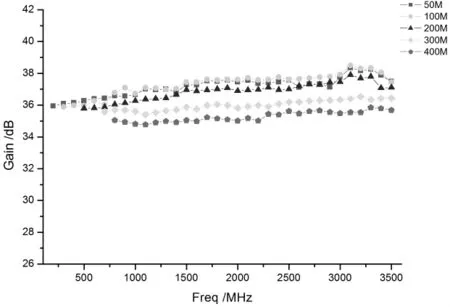

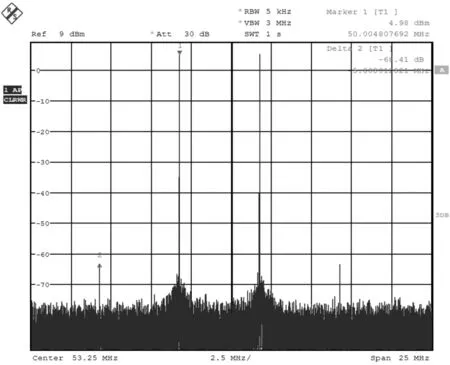

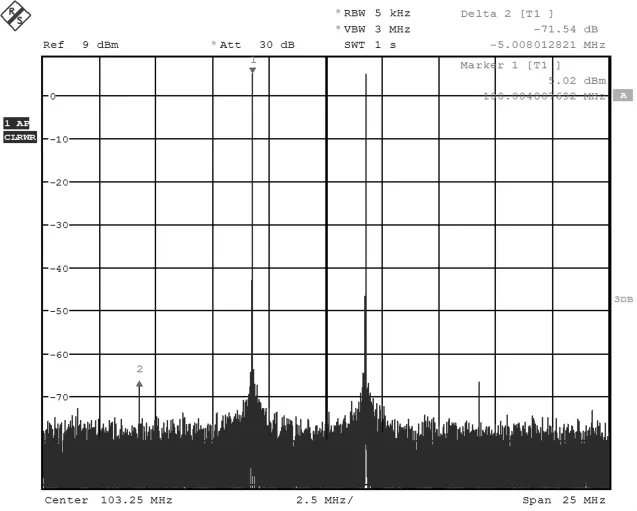

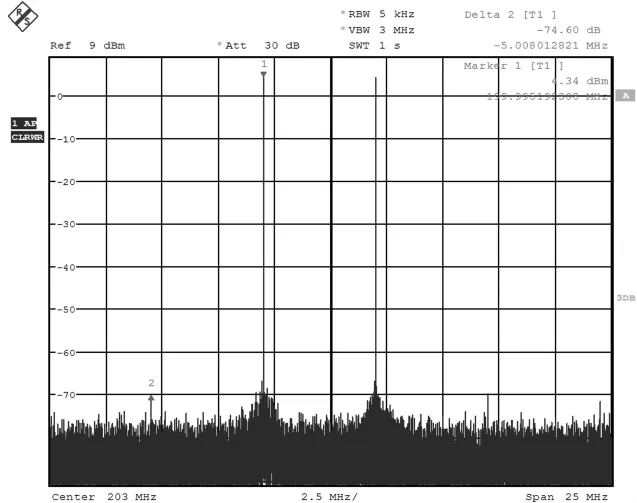

图9所示为接收通道整体的功率增益随射频频率变化的曲线,其中中频频率分别为50MHz、100MHz、200MHz、300MHz和 400MHz,整个频带内功率增益均≥35 dBm。图10、图11和图12所示为不同中频频率的双音测试输出频谱,双音的频率间隔是5MHz,输出一阶项的功率保持在5dBm左右,三阶交调项的功率低于一阶项70dB,输出三阶交调点≥40dBm。

图9 功率增益随频率变化图

图10 50MHz中频的双音测试输出频谱图

图11 100MHz中频的双音测试输出频谱图

图12 200MHz中频的双音测试输出频谱图

5 结束语

对接收机射频前端芯片采用TSMC 0.18-μm BiCMOS工艺流片,令整个接收电路实现了3dB的单边带 (SSB)噪声系数、35dB的转换功率增益、40dBm的输出三阶交调点、20dBm的输出1dB压缩点,芯片的工作电压5V,正常工作电流220mA。芯片射频频率覆盖200MHz~4GHz,中频频率范围50~400MHz。低通滤波器实现了片内集成,提高了集成度。中频放大器电路采用了高线性度的三阶项抵消结构,整个接收链路的OIP3达到40dBm以上。射频前端电路已通过流片测试验证,芯片具备宽频带、高集成度、高线性度等优异性能,适应现代雷达智能化、小型化、大动态的要求,可应用到雷达系统的射频T/R组件之中。

[1]RAZAVI B.RF Microelectronics[M].2nd ed.Upper Saddle River,NJ:Pearson Prentice Hall,2012.

[2]RAZAVI B.A 2.4-GHz CMOS receiver for IEEE 802.11 wireless LANs[J].IEEE Journal of Solid-State Circuits,2002,34(10):1382-1385.

[3]ZHANG P,NGUYEN T,LAM C,et al.A direct conversion CMOS transceiver for IEEE 802.11a WLANs[C]//2003 IEEE International Solid-State Circuits Conference.Digest of Technical Papers.San Francisco:ISSCC,2003(1):354-498.

[4]CROLS J,STEYAERT M S J.Low-IF topologies for highperformance analog front ends of fully integrated receivers[J].IEEE Transactions on Circuits and Systems,1998,45(3):269-282.

[5]FAVRE P,JOEHL N,VOUILLOZ A,et al.A 2-V 600-μA 1-GHz BiCMOS super-regenerative receiver for ISM applications[J].IEEE Journal of Solid-State Circuits,1998,33(12):2186-2196.

[6]RUDELL J C,OU J J,CHO T B,et al.A 1.9-GHz wideband IF double conversion CMOS receiver for cordless telephone applications[J].Computer Standards and Interfaces,1997,21(12):2071-2088.

[7]Long J R.A Low-Voltage 5.1-5.8GHz image-reject downconverter RF IC[J].IEEE Journal of Solid-State Circuits,2000,35(9):1320-1328.

[8]SHEN D H,HWANG C M,LUSIGNAN B,et al.A 900MHz integrated discrete-time filtering RF front-end[C]//1996 IEEE International Solid-State Circuits Conference.Digest of Technical Papers.San Francisco:ISSCC,1996:54-55.

[9]MEYER R G.Intermodulation in high-frequency bipolar transistor integrated-circuit mixers[J].IEEE Journal of Solid-State Circuits,2003,21(4):534-537.

[10]FONG K L,MEYER R G.Monolithic RF active mixer design[J].IEEE Transactions on Circuits&Systems,1999,46(3):231-239.

[11]Nguyen N M,Meyer R G.Si IC-compatible inductors and LC passive filters[J].IEEE Journal of Solid-State Circuits,2002,25(4):1028-1031.

[12]Cao Y,Groves R A,Huang X J,et al.Frequency-independent equivalent-circuit model for on-chip spiral inductors[J].IEEE Journal of Solid-State Circuits,2003,38(3):419-426.