一种具有对称结构的低损耗低纹波电荷泵

万 悦 ,吕 坚 ,周 云 ,阙隆成 ,田 雷

(1.电子科技大学光电科学与工程学院,成都610054;2.中国电子科技集团公司第四十九研究所,哈尔滨150009)

1 引言

随着人们对便携式电子设备的消费需求越来越高,电子产品的高性能、低功耗、轻型化等需要迫使着电源管理技术朝高效率、低功耗、高稳定性和高集成度等方向发展,对电荷泵的功耗和纹波要求也随之越来越高。

对现有的电荷泵而言,传统Diskson电荷泵[1-2]在高压工作条件下应用广泛,但随着工艺进入深亚微米,阈值电压有所减损,同时受衬底偏置效应影响,在低压工作条件下电流驱动能力不足的问题日趋明显。为解决电流驱动和转换效率等问题,对新型电路结构提出了要求。先从系统的角度设计了一种四相非交叠时钟信号控制的对称结构低损耗低纹波电荷泵,再依次详细分析了该结构电荷泵电路的原理和时钟控制逻辑,最后基于0.35μm BCD工艺完成了该新型对称结构低损耗低纹波电荷泵电路的设计,并在Spectre仿真平台下进行了仿真验证。

2 电荷泵系统设计

新型电路结构的设计有两种方案,第一种为动态电荷传输开关电荷泵结构,降低了开关的等效电阻,提高了转换效率,同时又增强了电流的驱动能力,但该结构并没有完全消除阈值电压损失和体效应的影响,也无法避免NMOS开关器件发生电荷逆流现象;第二种为四相时钟电荷泵结构,通过在MOS开关栅极上添加辅助升压电路来使MOS开关完全导通,降低其等效电阻,其中两路异相时钟与Dickson电荷泵中的时钟一样用来引导电荷的流向,另外两路时钟用来控制MOS开关的栅极,有效地解决了电荷逆流现象,在Dickson电荷泵基础上降低了损耗。

对于单分支电荷泵,虽结构相对简单,但负载能力弱,输出电压纹波也比较大,于是提出由两路分支组成的交叉耦合电荷泵,在一个周期内两路分支轮流给负载电容供电,使输出纹波较小[3-4]。

参考四相时钟电荷泵和交叉耦合电荷泵的优势,结合四相时钟电荷泵的低损耗和交叉耦合电荷泵的低纹波特点,最终设计方案被确定为一种对称结构的低损耗低纹波电荷泵。

本文所设计的电荷泵系统大致如下所述:振荡电路(OSC)产生幅值为VDD的时钟信号clk,再由非交叠时钟产生电路(Nonoverlap_clk)产生4组时钟控制信号,其中两路异相时钟Nonoverlap clkA/D用来引导电荷的流向,另外两路时钟Nonoverlap clkB/C用来控制MOS开关的栅极,协同合作控制泵电容的充放电,从而实现电压的抬升。抬升的泵电压OUT交替输出得到稳定的输出电压Vout。

3 电荷泵电路设计

3.1 对称结构电荷泵电路设计

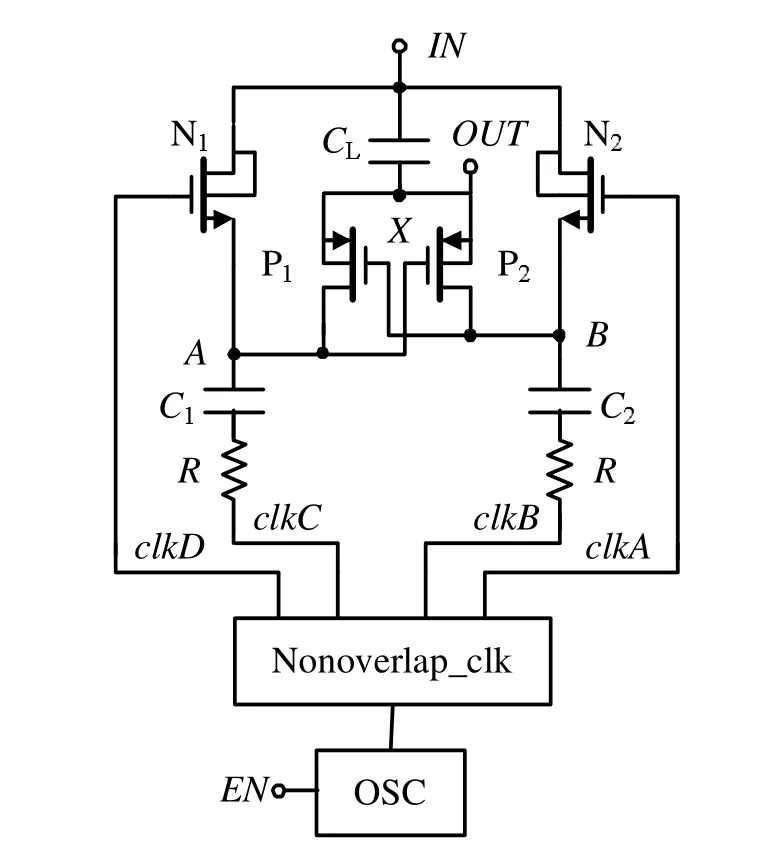

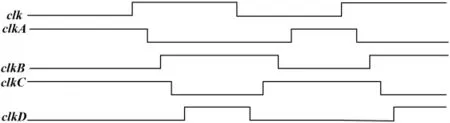

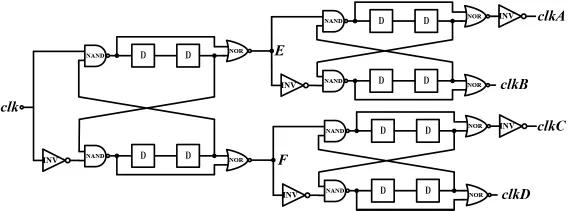

所设计的对称结构的电荷泵电路如图1所示。其中,clkA、clkB、clkC、clkD是一组四相非交叠时钟控制信号。时钟信号clk与clkA、clkB、clkC、clkD的时序关系如图2所示。采用非交叠时钟信号来控制电路是为了防止短路和电容漏电,提高电荷泵电路的性能[5]。电荷泵电路是利用电容两端电压不能突变的原理来实现电压的抬升[6]。当使能信号EN无效时,振荡电路OSC的输出clk恒定为低电平,clkA为高电平,输入Vin对电容C2充电,稳定时B点电位等于Vin。但此时电路维持静态,没有对电容进行周期性地充放电,故不能得到升压输出。

图1 对称结构的电荷泵电路

图2 非交叠时钟信号波形

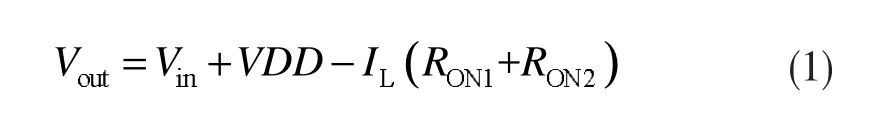

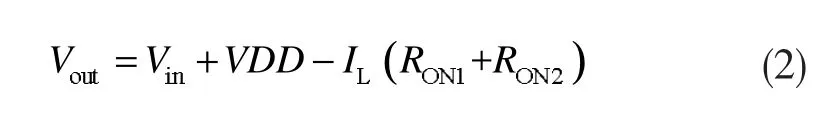

当使能信号EN有效时,振荡电路OSC开始输出周期性的时钟信号clk。clkA由高电平变为低电平,N2管关断,紧接着clkB由低电平变为高电平,电容C2的下极板电位等于VDD,由于电容电压不能突变的特性,B点电位等于VDD+Vin,P1管关断。而此时clkC为高电平、clkD为低电平,A点电位也等于VDD+Vin,P2管关断,B点电位得以维持。当clkC由高电平变为低电平后,A点电位降为Vin,P2管导通,电荷泵输出B点电位,得:

其中 RON1为 NMOS管的导通电阻,RON2为PMOS管的导通电阻,IL为是负载电流。

之后,clkC为低电平,clkD由低电平变为高电平,N1管导通,A点电位等于Vin。维持一段时间之后,clkD先变为低电平,使N1管关断,然后clkC信号再变为高电平,将A点电位抬升至Vin+VDD。同理,当clkB变为低电平且clkA变为高电平之后,B点电位为Vin,P1管导通,电荷泵输出A点电位,得:

受到非交叠时钟控制,X点交替通过P1管或P2管连接到A点或B点,高频率的时钟变化保证了电荷泵的输出电容能够快速得到补充,从而降低输出纹波。由电荷守恒定律知半周期内电容提供的电荷等于负载得到的电荷,即

其中ΔV是输出电压的变化值,I是负载电流,T是时钟周期,并且假设C1=C2=C。

由(3)式可得输出电压纹波ΔV为:

根据以上分析,电荷泵的效率会受到传导损耗的影响,此损耗主要是MOS管的导通阻抗导致的。

当电路工作稳定时,MOS管工作在线性区,MOS管导通电阻为:

其中,μ为沟道载流子迁移率,Cox是单位面积的栅氧化层电容,Vo是过驱动电压。减小电荷泵的输出电阻即可获得较强的电流驱动能力,因此需减小导通电阻RON,即增大过驱动电压Vo。

NMOS和PMOS管的过驱动电压分别表示为:

结合(1)~(7)式,可求得传导损耗为:

根据公式(8)可以看出,传导损耗正比于MOS管的栅长L和负载电流IL2,反比于栅宽W。

3.2 非交叠时钟信号产生电路设计

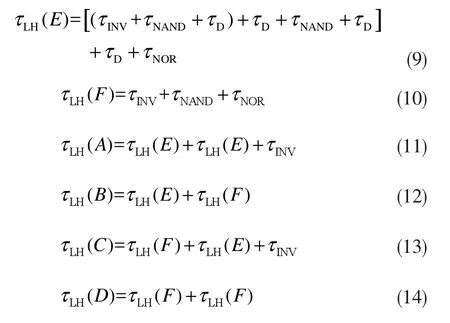

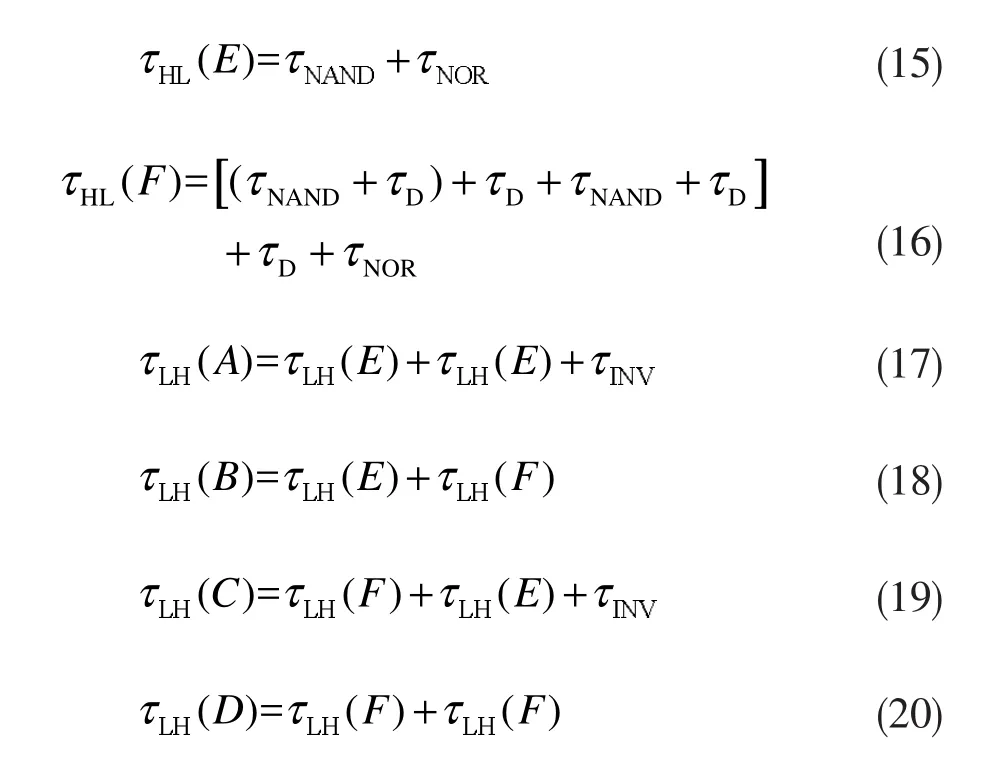

非交叠时钟信号产生电路如图3所示。D是延时电路,由电容和偶数个反相器组成。时钟信号clk经过四个不同的逻辑运算通路而得到不同时延,从而产生四个非交叠的时钟信号,设他们的峰值电压为Vclk。在时钟信号的上升沿和下降沿,非交叠时钟信号的触发时序是不同的[7]。

图3 非交叠时钟电路

在时钟信号clk的上升沿,clk到节点A、B、C、D、E和F的延时依次为:

其中τD为单个延时电路D的延时,τNAND是单个与非门的延时,τNOR是单个或非门的延时,τINV是单个反相器的延时。

在时钟信号clk的下降沿,clk到节点A、B、C、D、E和F的延时依次为:

将相应信号的延时做差就可得到对应的非交叠时间,这里不再详述。时钟的延迟避免了P1和P2管的同时导通,有效的解决了电荷逆流现象。若P1、P2管同时导通,会导致Vout与Vin之间形成通路,增加损耗,也会增大电路纹波[8]。

4 仿真结果

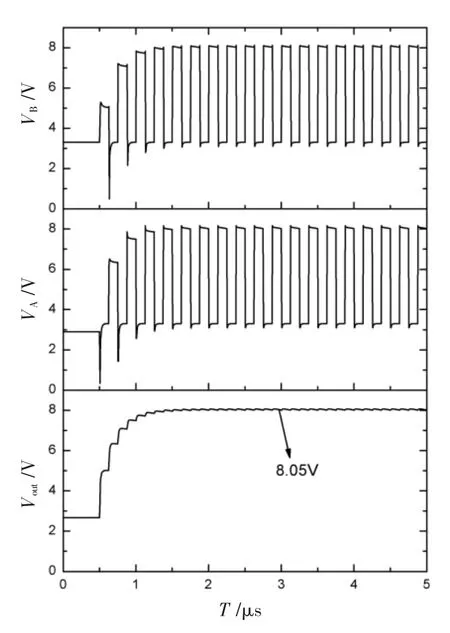

设计的电荷泵电路基于0.35μm的BCD工艺。电荷泵电路的工作频率为4MHz,输入电压Vin为3.3V,芯片内部工作电压VDD为5V,在负载电流等于10μA的条件下对电路进行Spectre仿真,0.2μs时振荡电路开始工作。

图4所示的是非交叠时钟控制信号在时钟上升沿和下降沿的仿真波形。从仿真波形图可以看出,振荡电路OSC的输出clk为4MHz信号。当时钟信号clk由低电平变为高电平时,clkA、clkB、clkC、clkD依次跳变;当时钟信号clk由高电平变为低电平时,clkD、clkC、clkB、clkA 依次跳变。在时钟信号clk 的上升沿,具体有 τLH(A,B)=1.00ns,τLH(B,C)=0.67ns,τLH(C,D)=0.95ns;在 clk 的下降沿,有 τHL(A,B)=-1.56ns,τHL(B,C)=-1.30ns,τHL(C,D)=-1.55ns。

图5是A、B两点电位和电荷泵输出Vout的仿真波形,其负载电流为10μA。结果表明输出级OUT能够很好地输出A、B两点中电位较高的点的电位,大幅度减小了输出纹波。在4MHz的工作频率下,当输入电压为3.3V、负载电流为10μA时,电荷泵输出电压Vout为8.19V,其电压纹波仅有9mV。

图4 非交叠时钟信号的仿真波形

图5 A、B点电位和输出电压仿真波形

5 结束语

就现有的电荷泵而言,为解决传统Diskson电荷泵关于电流驱动和转换效率的问题提出的几种新的额电路结构也是各有优势各有不足,单分支电荷泵随结构简单,但输出电压纹波比较大,由此提出了交叉耦合电荷泵,在一个周期内两路分支轮流供电,以减小输出纹波。动态电荷传输开关电荷泵结构虽提高了其转换效率和电流驱动能力,但无法避免开关器件的电荷逆流现象,由此提出四相时钟电荷泵结构有效避免了电荷逆流,并在传统电荷泵的基础上降低了损耗。

传统的开关电源通常使用一个电感实现DCDC变换,但是电感体积庞大、容易饱和、会产生EMI,而且电感价格昂贵。为解决此类问题,现代电源通常采用电荷泵电路。电荷泵采用电容储存能量,外接组件少,非常适合用于便携式设备中,并且随着其电路结构的不断改进,也可应用在需要较大电流的应用电路中。具有优异性能的电荷泵结构可广泛应用在电子设备电源电路中。结合四相时钟电荷泵结构低损耗和交叉耦合电荷泵结构低纹波的特点,设计出的一种新的电荷泵结构,达到了同时具备低损耗和低纹波优势的效果,面对面积日趋减小,对功耗要求也越来越小的便携式电子设备行业,希望该电荷泵结构可以在未来电子设备的电源电路应用中可发挥更好的作用。

[1]UMEZAWA A,ATSUMI S,KURIYAMA M,et al.A 5-V-only operation 0.6-μm flash EEPROM with row decoder scheme in triple-well structure[J].IEEE Journal of Solid-State Circuits,1992,27(11):1540-1546.

[2]DADHICH H,MAURYA V,VERMA K,et al.Design and analysis of different type of charge pump using CMOS technology[C]//International Conference on Advances in Computing,Communications and Informatics.IEEE,2016:294-298.

[3]徐彦峰,钱栋良,李环,等.一种高增益低纹波的电荷泵电路[J].电子与封装,2017,17(7):21-24.XU Yanfeng,QIAN Dongliang,LI Huan,et al.A charge pump circuit with high gain and low ripple[J].Electronics&Packaging,2017,17(7):21-24.

[4]魏哨静,梅年松,张钊锋,等.一种低压高效的电荷泵设计[J].微电子学与计算机,2017,34(10):72-75.WEI Shaojing,Mei Niansong,ZHANG Zhaofeng,et al.Design of a low voltage and high efficiency charge pump[J].Microelectronics&Computer,2017,34(10):72-75.

[5]吴浩,李富华,郑坚斌.一种提高效率和减小电压纹波的电荷泵[J].中国集成电路,2006,15(12):22-24.WU Hao,LI Fuhua,ZHENG Jianbin.A charge pump that improves efficiency and reduces voltage ripple[J].China Integrated Circuit,2006,15(12):22-24.

[6]TANZAWA T,ATSUMI S.Optimization of word-line booster circuits for low-voltage flash memories[J].IEEE Journal of Solid-State Circuits,2002,34(8):1091-1098.

[7]YAMAZOE T,ISHIDA H,NIHONGI Y.A charge pump that generates positive and negative high voltages with low powersupply voltage and low power consumption for non-volatile memories[C]//IEEE International Symposium on Circuits and Systems.IEEE,2009:988-991.

[8]MIN K S,KIM Y H,KIM D,et al.A large-current-output boosted voltage generator with non-overlapping clockcontrol or sub-1-V memory applications[C]//Asia and South Pacific Design Automation Conference.IEEE Press,2004:288-291.