多通道超声波数据采集传输实现方法*

丁孝超,杨 媛,陈 福

(西安理工大学 自动化与信息工程学院,陕西 西安 710048)

0 引言

现今高铁迅速发展,高铁无缝长轨负荷量不断增加,在役钢轨在承受负荷时受到交变弯曲应力和横向应力而产生磨损、塑性变形及疲劳损伤,钢轨性能逐渐劣化,导致钢轨断裂失效和断轨事故时有发生,因此对轨道进行损伤监测成为保障列车行车安全的重要手段[1]。随着超声无损检测技术的发展,为全面完整地评估钢轨的健康状况,需以不同的入射角发射超声波,来增大对待检测缺陷的覆盖范围,这就使得多通道损伤检测系统越来越多地应用到在役钢轨的损伤检测研究中[2]。传统的超声波数据采集完成后是通过串行总线将数据传输到处理单元,但是针对多路超声波信号仍采用该方式,将会使数据传输成为检测系统实现实时性的瓶颈,导致超声波换能器的重复频率降低,检测速度变慢[3-4]。

本文在考虑可实现性和高效率数据传输的前提下,采用ARM+FPGA的架构完成对2通道超声波信号的采集,为以后更多通道的数据采集提供解决方案,同时采用FPGA对数据进行FIR滤波,最后通过FSMC接口将处理后的数据传输到ARM完成算法处理。

1 系统结构

本文以2通道超声波为例进行数据采集系统设计,该框架可以支持更多通道的数据采集,系统框架设计如图1所示。由ARM控制FPGA进行数据采集和数据传输,FPGA在接收到ARM的控制信号后,通过判断交替产生激励脉冲激励探头1和探头2,然后将接收到的回波数据经过限幅、带通滤波、增益放大和偏置后送到高速AD处,由FPGA产生控制信号使能高速AD完成数据采集并将数据缓存到FPGA内部FIFO中。为保证数据的正确性,本文通过FIR滤波器对数据进行预处理,并将处理后的数据缓存到RAM中,最后在ARM的控制下通过灵活的静态存储器控制器[5-6](Flexible Static Memory Controller,FSMC)接口将滤波后的数据发送给ARM进行算法运算。

图1 系统框图

1.1 硬件设计

本文所涉及的硬件电路主要包括激励电路、信号调理电路、数据采集等,此处只给出其中一路的硬件电路设计,其他通路结构相同。由于本文采用的是收发一体的超声波换能器,其接收到的回波信号受到激励的影响具有较大的振幅,因此调理电路使用一对高频二极管对回波信号进行限幅处理。限幅后的信号经过信号放大后,进行带通滤波,本文采用的超声波换能器中心频率是2.5 MHz。为取得较好的滤波效果,本文设计了一个中心频率为2.5 MHz、上下限截止频率分别是2.7 MHz和2.3 MHz、通带增益为1的二阶滤波器。AD采集采用高速ADC芯片AD9226,它采用单端输入和输出误差校正逻辑的多级差分流水线架构,在65 MS/s数据速率下具有12位精度。

1.2 FIR滤波器设计

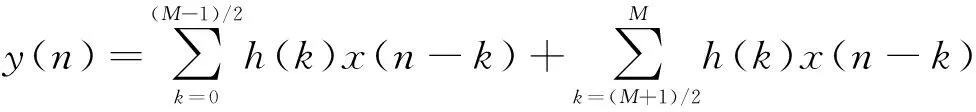

数字滤波器是通过数字运算器件对输入的数字信号进行处理,改变信号频谱,以得到期望的响应特性的离散时间系统。根据数字滤波器的功能特征,可以将其分为低通、高通、带通、带阻以及全通类型,根据冲击响应特性的不同,又可以分为IIR和FIR数字滤波器,其中FIR滤波器有其自身的优点,成为信号处理中滤波器的一种常用电路[7-8]。本文采用具有线性相位的FIR滤波器,以M为奇数、单位取样响应为偶对称的FIR滤波器为例,其传递函数如下:

(1)

(2)

(3)

(4)

式(4)即为FIR的传递函数,实现该传递函数的方式有串行结构、并行结构、分布式结构以及IP核,本文通过调用IP核的方式实现FIR滤波器。根据前面所述,本文涉及的超声波信号中心频率是2.5 MHz,为了更好地得到该处信号,设计数字带通滤波器。系统的采样率Fs为25 MHz,截止频率为2.3 MHz和2.7 MHz,阻带衰减为-40 dB,通带不衰减,通过MATLAB的FDAtool工具得到滤波器系数,并将该系数进行12 bit的位宽量化,作为最终的FIR滤波器的系数。

1.3 FPGA与ARM通信设计

目前FPGA与ARM的通信方式很多,按数据传输方式分为两类:一类是串行传输,此类方式接口简单,传输速率较低,不利于高速数据采集,常见的如UART、USART、I2C、SPI等[9-10];另一类是并行传输,顾名思义可以一次传输多位宽信号,配合相应的时序控制即可。本文为满足高速数据采集及传输,采用FSMC总线实现并行传输。

FSMC是STM32采用的一种新型存储器控制技术,支持多种类型的外部存储器,其主要包含四个模块:AHB接口、NOR闪存和PSRAM 控制器、NAND闪存和PC卡控制器、外部设备接口。所有的外部存储器共享地址、数据和控制信号,但有各自的片选信号,FSMC 一次只能访问一个外部器件。FSMC提供了4个Bank用于连接不同的外部存储器,其中Bank1又被划分为4个NOR /PSRAM区域,FSMC为每个存储区域输出唯一的片选信号NE[4: 1]。FPGA连接在Bank1的第三区域,FSMC_NOE和FSMC_NWE分别是接口读写信号,根据应用需求,设计接口数据宽度为16 bit,地址线为1 bit,将数据线FSMC_D[15: 0]和地址线FSMC_A[15: 0]连接到FPGA的I/O端口,寻址空间为64 KB。因此FPGA就作为STM32的外设被连接到系统中,通过存储器读写指令就可以访问FPGA,其实质就是将FPGA通过FSMC总线映射为STM32的一个SRAM。FPGA与STM32的接口电路连接如图2所示。

图2 FPGA与STM32接口电路

在STM32内部,FSMC的一端通过内部高速总线(Advanced High performance Bus,AHB)连接到Cortex-M4内核上,另一端则是面向扩展存储器的外部总线。内部AHB总线的地址HADDR与FSMC总线地址存在一定的映射关系,具体如下。HADDR总共有28根地址线(HADDR[27:0]),其中HADDR[27:26]用于对Bank1的4个区域进行寻址,当FPGA使用第三区时,对应的HADDR[27:26]为10。

Bank1在外接16 bit存储器时,FSMC将在内部使用HADDR[25:1]产生外部存储器的地址FSMC_ADDR[24:0],即在进行地址读写操作时,HADDR[0]并未使用,实际上对应关系HADDR[25:1]变为FSMC_ADDR[24:0]。知道该对应关系后,接口地址FSMC_ADDR[15:0]对应的HADDR的地址为0x68000000~0x6801FFFE,具体如表1所示。

表1 STM32中FSMC有关的地址映射

2 软件实现

本文软件实现主要包括两部分内容:FPGA软件实现和STM32软件实现。主要目的是:(1)通过设置FPGA内部的各个状态寄存器的读写,完成对高速AD的控制和采集通道的选择以及各时延要求;(2)将接收到的数据完成FIR滤波并缓存;(3)通过FSMC接口完成对数据的传输。

2.1 FPGA软件实现

FPGA主要是接收来自STM32的指令,然后控制高速AD完成数据采集,并将采集到的数据经过FIR滤波(可选)后,通过FSMC接口将数据传输到STM32中进行后级处理,程序流程图如图3所示。

图3 FPGA程序流程图

系统上电后,FPGA通过PS(被动模式)方式完成配置,然后侦测STM32发送的信号STM32_en1和STM32_en2是否存在指定宽度的脉冲,若存在,则记录该脉冲来源并产生与其对应的指定宽度的脉冲,该脉冲宽度由激励电路中电容充放电的时间常数τ决定,本文根据电路参数,计算得到该脉冲宽度为200 ns。产生完激励信号后,将进行高速AD采集,在此之前需要延时以等到超声回波信号。打开AD使能,并以AD采集时钟作为异步FIFO的写时钟,将采集到的数据写入到FIFO中。根据实际需要,决定是否打开FIR滤波器,然后将滤波器输出的数据通过FSMC发送给STM32,具体过程是利用异步FIFO的“空”标志,向STM32产生FSMC通信请求,STM32通过拉低片选信号(片选信号低有效)来响应本次数据传输请求,并通过控制FSMC读使能信号完成FSMC的数据传输,当STM32接收到既定数据量时,将拉高片选信号结束本次数据传输。由于FPGA的内部各模块是并行执行,因此上述程序流程只是描述了一次数据采集及传输流程,FPGA随时都在侦测STM32的使能信号,以进行下次数据采集,提高整个系统的效率。

2.2 STM32软件实现

STM32在本文中的主要功能是控制FPGA并完成数据的接收,为后期算法处理提供可靠的数据,其程序流程图如4所示。

图4 STM32程序流程图

首先配置STM32需要用到的端口及FSMC接口寄存器,然后产生STM32_en1使能信号并判断是否有FSMC通信请求信号,若接收到请求信号,则拉低片选信号和使能FSMC读信号,接收完既定数据后,使能STM32_en2,激励另一个超声波换能器,并开始执行其他操作,等到FSMC通信请求信号到来时,开始响应FSMC通信,重复上述操作,即可完成两路数据交替采集和数据传输,并且可以十分方便地扩展成多路数据采集及传输。程序流程图中的其他操作主要是用于数据处理。

3 实验结果

本文采用自制的硬件平台进行超声波激励和数据采集及传输,其中控制器采用STM32F407ZGT6,该芯片是基于Cortex-M4内核,具有极其丰富的外设资源,其主频是168 MHz,内存是1 MB,Flash是1 MB,支持FSMC接口;本文采用的FPGA是Altera的EP4CE6E22C8N,其时钟频率最大可达200 MHz,具有6272LUT,270 Kbit的EBR等丰富资源。本文将对前面所述的超声波激励、FIR滤波设计以及FSMC通信进行验证。

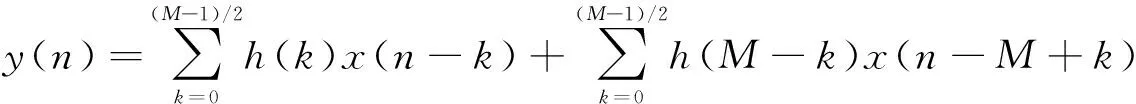

3.1 硬件电路测试结果

在本文的硬件平台上,给激励电路施加400 V直流电源,测得激励电路产生的尖负脉冲激励信号如图5所示,负脉冲峰值绝对值为396 V,脉冲宽度为160 ns,脉冲下降时间为35.6 ns。利用该激励信号激励超声波换能器并将接收到的回波信号经过放大和带通滤波得到的信号如图6所示。

图5 激励信号

图6 超声波回波信号

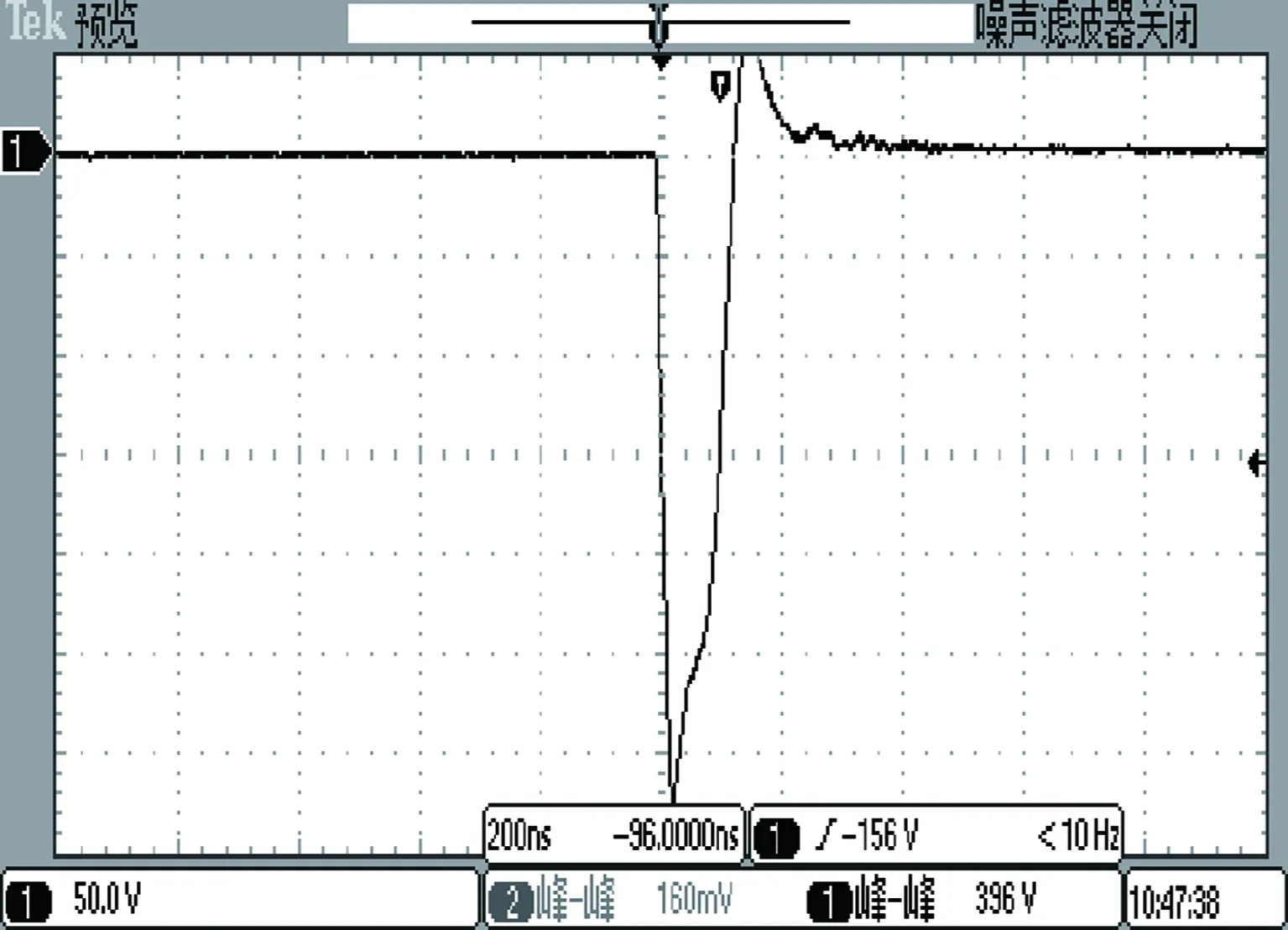

3.2 FIR滤波器测试结果

本文通过调用IP核来实现FIR滤波器的设计,将采集到的超声波信号经过FIR滤波器后,通过MATLAB将处理后的数据进行频谱分析,如图7所示。

图7 FIR滤波前后波形及频谱

从图7可以看到FIR滤波前信号主要集中在2.5 MHz附近,但是仍存在较多其他频率分量;滤波后使得信号在2.5 MHz处更加集中,对带外信号进行抑制。从图中可以看出FIR滤波具有明显的效果。

3.3 FPGA与ARM通信测试结果

本文通过在FPGA内部实现计数器,然后通过FSMC将计数器值发送到STM32,然后通过串口将数据打印出来以判断传输是否正确。图8是通过示波器抓取波形,其中①是FSMC的读信号,②是数据的最低位信号线,从图中可以看到当FSMC的读信号拉低时,数据的最低位信号由低变到高,通过配置FSMC的控制寄存器,可以设置地址和数据的建立和保持时间(都是以STM32的AHB时钟HCLK为参考),保证在FSMC读信号有效期间数据能够被正确传输。

图8 FSMC读使能与数据信号图

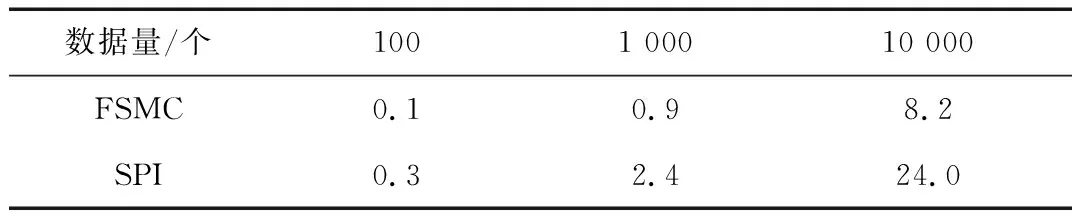

为验证采用FSMC通信方式相较于SPI通信方式在传输效率上的变化,本文通过将STM32作为主机,FPGA作为从机进行SPI通信测试,实验中SPI的时钟最大能达到APB时钟的8分频即10.5MHz。数据位宽16bit,分别对同样数据量下不同通信方式耗时量进行比较,结果如表2所示。

表2 FSMC与SPI对比 (ms)

通过表2可以看到随着数据量的增加,FSMC通信方式优势更加明显,并且对于实时大量数据处理的系统,采用FSMC通信将大量缩短数据传输的时间,给数据处理部分留出更多的时间。

4 结论

本文设计的多通道超声波数据采集与传输方案采用ARM与FPGA相结合的硬件架构,分别利用了ARM运算控制能力强和FPGA速度快的优势,设计了超声波激励与调理电路,通过绘制PCB板完成了数据的采集与传输。在FPGA内部增加可选的FIR滤波器,对高速AD采集到的数据进行预处理,最后通过在自制的硬件平台上完成验证。与SPI通信方式进行了对比,结果表明FSMC通信方式在大量数据传输中优势明显,为后期实施大量数据处理节约了更多时间。本文方案适合常见的多通道数据采集与传输系统,具有很好的扩展与移植特性。

[1] 赵扬, 陈建伟, 孙继华,等. 在役钢轨无损检测技术与系统的应用与发展[J]. 无损检测, 2014, 36(3):58-64.

[2] LAD P, PAWAR M. Evolution of railway track crack detection system[C]// IEEE International Symposium on Robotics and Manufacturing Automation. IEEE, 2017:1-6.

[3] CHEN Z, JIA Y, JIANG G, et al. A multi-channel ultrasonic non-destructive testing system-based on ethernet[C]// IEEE International Conference on Control and Automation. IEEE, 2007:385-388.

[4] 辛光, 伍川辉. 基于STM32的列车噪声数据采集系统[J].兵器装备工程学报, 2012, 33(1):90-92.

[5] 宋雅琪, 韩晓军, 荣锋,等. 基于ARM和FPGA的多通道振动信号采集仪的设计[J]. 仪表技术与传感器, 2016(5):25-28.

[6] 王晨, 乔旭兴, 闫文奇, 等. Graphic display terminal for FSMC (flexible static memory controller) bus architecture:中国, 204009859 U[P]. 2014-07-22.

[7] Liu Hao, Miao Changyun, Feng Yongmao, et al. Design and realization of integrated ultrasound transmitting circuit[J]. Instrumentation Measurement Circuits & Systems, 2012, 127:137-144.

[8] SINGH G, PRAKASH N R. FPGA implementation of higher order FIR filter[J]. International Journal of Electrical & Computer Engineering, 2017, 7(4):1874.

[9] 朱望纯, 张硕, 蒋汉林. 基于ARM与FPGA高速数据通信接口设计[J]. 桂林电子科技大学学报, 2017(4):293-297.

[10] 赵星. STM32基于FSMC的SRAM扩展技术[J]. 工业控制计算机, 2015, 28(6):102-103.