K波段pHEMT下变频混频器的设计与研究*

李 罡,余 凯,李思臻,章国豪,周正轩,刘祖华

(1.广东工业大学 信息工程学院,广东 广州 510006;2.广州穗源微电子科技有限公司,广东 广州 510006)

0 引言

随着无线通信技术的不断进步与发展、应用背景的多样化和性能的高端化,应用领域也随之逐渐不断扩大,无线通信系统的设计指标也日趋严格。下混频器作为射频前端接收端的一个重要模块,其功能是将接收到的射频信号下变频到中频信号。因为下变频混频器的性能会对整个射频接收机系统产生较为显著的影响,所以对下混频器的线性度、转换增益、隔离度、功耗都有着较为严苛的要求。在第五代移动通信中,K波段(18.0~26.5 GHz)作为卫星通信频段(19.2~20.2 GHz,21.4~22 GHz)和潜在的频段被美国和欧洲的频谱规划所提及,具有重要的研究意义。

可以用来实现K波段通信电路的工艺有硅CMOS工艺、砷化镓GaAs工艺、氮化镓GaN工艺等。CMOS成本低廉,易于实现,在低频电路中被广泛使用。但是它的硅基衬底损耗是个严重的问题[1],在实现片上无源器件(如电感、变压器、巴伦)时的品质因数Q也很小。由于GaAs电子迁移率比硅高6倍,电流密度较高,适合用于超高速、超高频器件的设计。作为衬底材料,GaAs的电阻率低,具有较高的击穿电压阈值,寄生电容更小,噪声更低,这些特性导致GaAs材料具有更好的高频特性。且较GaN产品而言,GaAs产品更为成熟,成本相较GaN更低,可靠性更好。

本文提出了一种下变频混频器,主要应用于K波段无线收发机的接收端。本方案的创新点在于:集成了两个片上巴伦,能够实现差分-单端的转换。在混频器的开关级应用了电流注入的技术,且在输出端采用了源跟随器,有效地改善了电路的增益,提高了线性度。与其他文献相比,此设计具有更好的电路性能。

1 系统设计

1.1 混频器结构

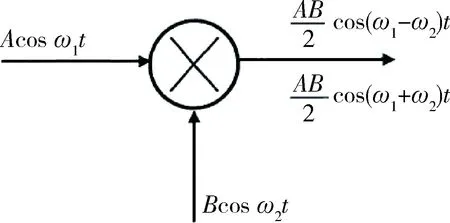

如图1所示,混频器是一种三端口器件,包括中频信号IF输入端口、本振信号LO输入端口、射频信号RF输出端口,主要完成中频信号到射频信号转换的功能。

图1 混频器原理图

在时域上,中频信号通过混频器模块与本振信号相乘,从而在频域上表现出中频信号频率与本振信号频率相加减。假设输入的中频信号和本振信号均为正弦型信号,则通过这两个信号的混频,可以得到一个差频成分(频率为ω1-ω2)和一个和频成分(频率为ω1+ω2),理想情况下,差频成分与和频成分的幅度与输入信号的幅度成正比,可表示为式(1):

cos(ω1+ω2)t]

(1)

在下混频器中,需要的信号为差频信号,所以需要信号在输出端通过一个滤波器滤除差频信号以外的其他干扰信号成分,从而取出所需要的差频信号。在工程应用中,为了滤除不需要的信号,一般会采用高Q值的片外滤波器来实现。

混频器通常根据其是否提供正的转换增益值,分为有源混频器和无源混频器两大类。相较于无源混频器,有源混频器能提供更高的增益。因为传统单端结构混频器不能完全消除和抑制非线性,且对电源的抑制较差,在无线通信的应用中,射频前端系统一般会使用平衡式电路来提高其性能,因此差分输入输出为射频前端重要的输入输出形式。混频器一般采用差分结构实现输入信号相乘来消除高次谐波部分以及共模成分。

有源混频器中有一类很重要的混频器称为平衡型混频器,若输入信号和本振信号均采用差分形式输入,则称之为双平衡混频器。事实上,差分结构能够很好地抑制共模噪声,因此减少了基带信号输出的直流失调。除此之外,双平衡混频器与单平衡混频器相比,能够很好地消除本振馈通,也能够很好地消除叠加在混频器输入本振信号上的干扰和噪声[2]。

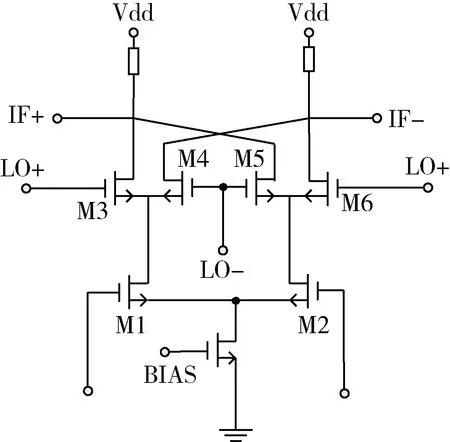

双平衡混频器也称之为Gilbert单元,基本结构如图2所示,双平衡混频器由跨导级、开关级、输出级三部分组成。跨导级由晶体管差分对M1、M2组成。将输入的电压信号转换为电流信号,送入开关对的共源节点。晶体管M3、M4、M5、M6四管差分对构成本振驱动级,当本振信号幅值偏大时,差分对MOS管M3、M4、M5、M6构成混频器的开关级。当本振信号足够强时,在本振信号LO的控制作用下将跨导级输入进来的电流周期性地开启关断,工作在开关状态。在M3与M6导通时,M4与M5关断,当M4与M5导通时,M3与M6关断,从而将跨导级的电流周期性地从一边转换到另一边,实现混频功能。在M3~M6处于理想开关的状态时,电路的电压转换增益如式(2)所示:

(2)

其中gm3为M3的跨导,RL为中频输出负载。

图2 Gilbert混频器结构

1.2 巴伦设计

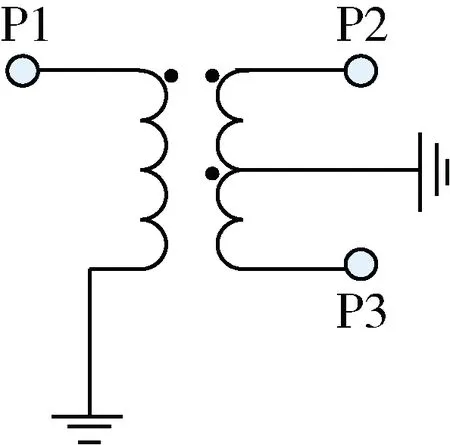

双平衡混频器的一个重要部分就是巴伦平衡-不平衡(Balun,Balance-unbalance)转换器。巴伦是一种将单端信号转为差分信号的模块,可用于PA、LNA、混频器等模块[3]。在理想情况下,单端信号通过巴伦模块能够输出两个幅度相等、相位相反的信号。巴伦器分有源巴伦和无源巴伦两种。常用的无源巴伦结构有平行线巴伦、变压器巴伦、Marchand巴伦。除了变压器巴伦以外,其他的两种结构都会用到90°波长线,而90°波长线在频率较低的场合使用会显著增加微带线的长度,从而增大芯片的面积[4]。有源巴伦结构主要是利用晶体管的各种工作特性来实现相应的功能,如共源极电路能输入输出相位相反的信号,共栅极电路能够输入输出相位相同的信号,但是实现起来较为复杂,且占用芯片面积较大。故在本设计中,射频端和本振端均采用变压器巴伦结构进行设计。

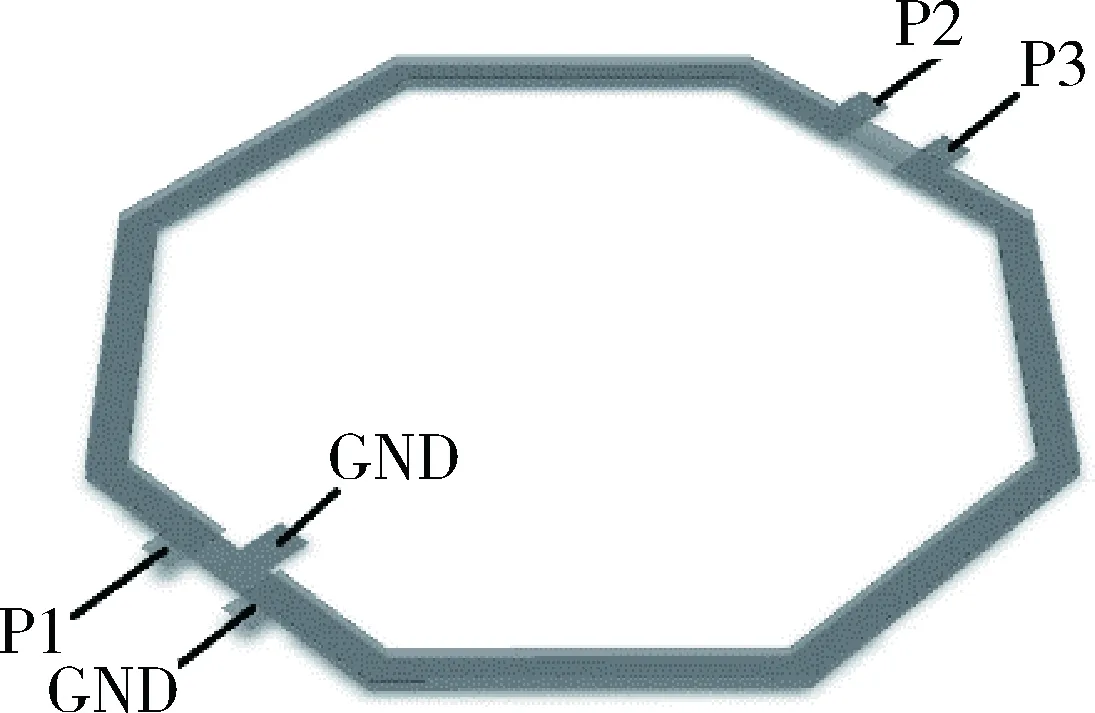

理想的变压器巴伦结构如图3所示。P1端为单端信号输入,P2与P3端输出为等幅、相差为180°的差分信号。

图3 理想巴伦

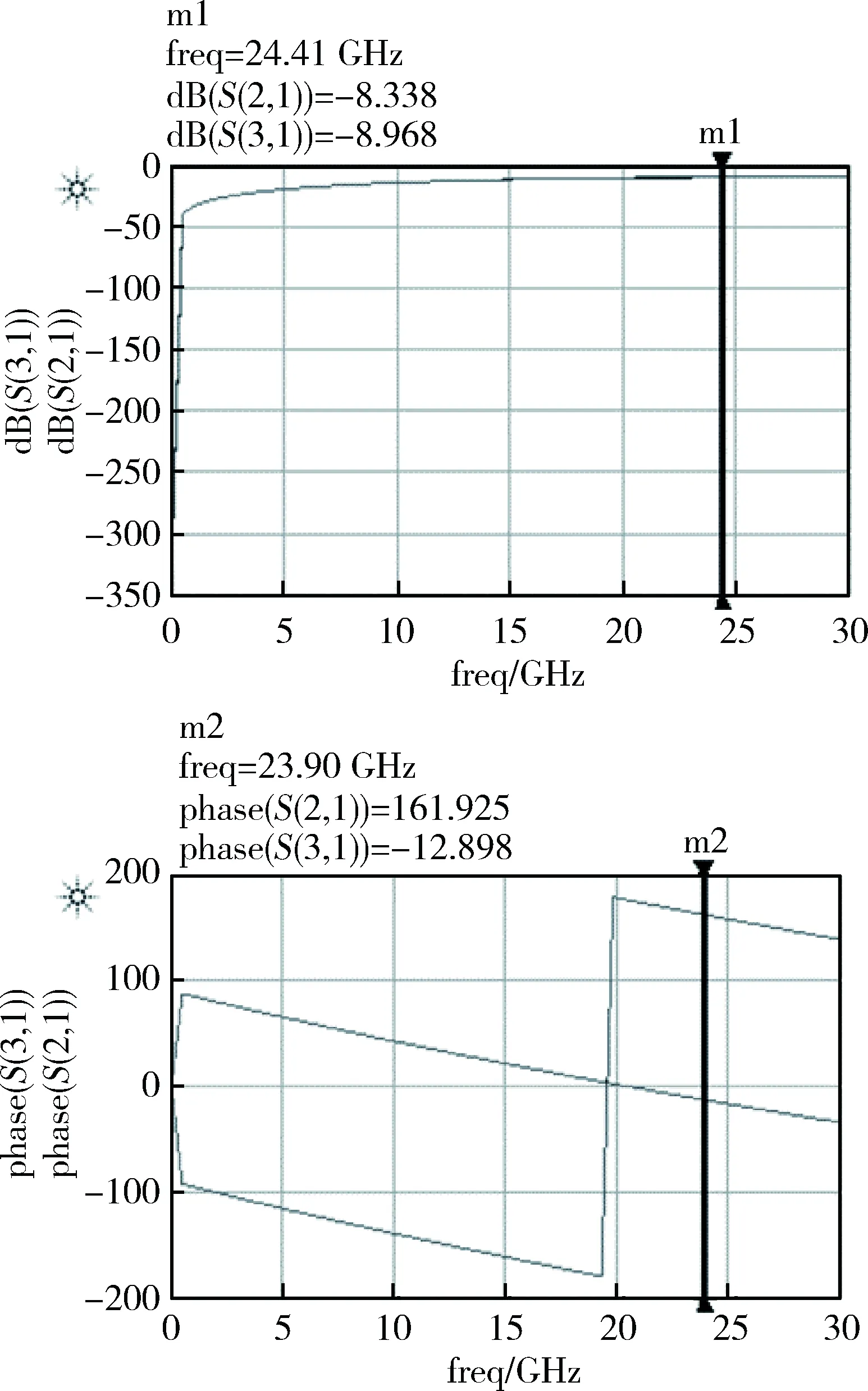

本文采用了一种上下叠层结构巴伦[5],结构示意如图4所示。该巴伦由上下两层金属耦合构成,与P1端连接的耦合线在金属2层,P2与P3端在金属1层,金属1层与金属2层的几何结构为正八边形,利用HFSS软件仿真,最终设计线宽为6 μm,内半径为70 μm。图5给出图2的S参数、幅度差、相位和相差的仿真结果。在中心频率约为24 GHz时P1到P2、P3端口的S参数S(2,1)=-8.338 dB,S(3,1)=-8.968 dB;幅度值不平衡差为0.63 dB;相位差为174.823°。由幅度差曲线与相位差曲线数据可以得出,正八边形巴伦可以适用于较宽的工作频带。

图4 上下叠层巴伦模型

图5 巴伦幅度差和相位差曲线

2 电路设计

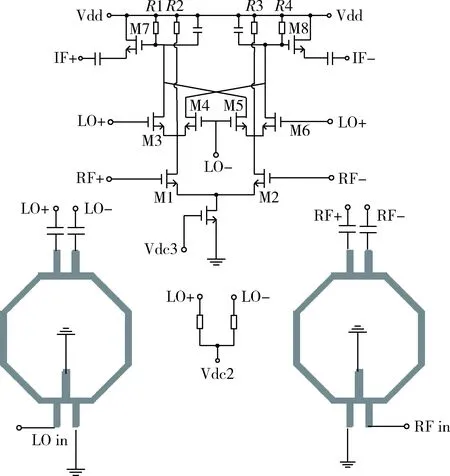

本文电路原理图如图6所示。射频输入端和本振输入端都采用了本文所述的上下叠层巴伦,M1~M6构成吉尔伯特单元。M1和M2为A类偏置,射频信号经过巴伦转换为差分信号,施加到M1和M2的栅极,产生了相对恒定的增益,抵消了偶次谐波,另外射频跨导级M1、M2也采用了电流注入技术[6-7],降低了功耗。本振信号经过巴伦转换成差分信号分别作用在M3~M6的栅极,M3~M6的漏极信号输入到M7和M8的栅极,M7与M8构成源极跟随器,以使得中频输出IF+/IF-相匹配。

图6 电路原理图

M1和M2为信号放大级,M3~M6在LO信号的调控下工作在开关状态,在M3和M6为开启状态时,M4和M5为关闭状态,反之,在M4和M5为开启状态时,M3和M6为关闭状态。M1漏端小信号电流在LO信号一个周期中,半周期中由M3源端流入,另半周期由M4源端流入。同理M2漏端工作状态与M1相同。LO信号为正弦波大信号,LO的差分信号分别加载在M3、M6的栅极与M4、M5的栅极。M3、M6在LO的正半周期饱和导通,M4、M5栅源电压必定小于开启电压,处于关断状态,反之亦然。

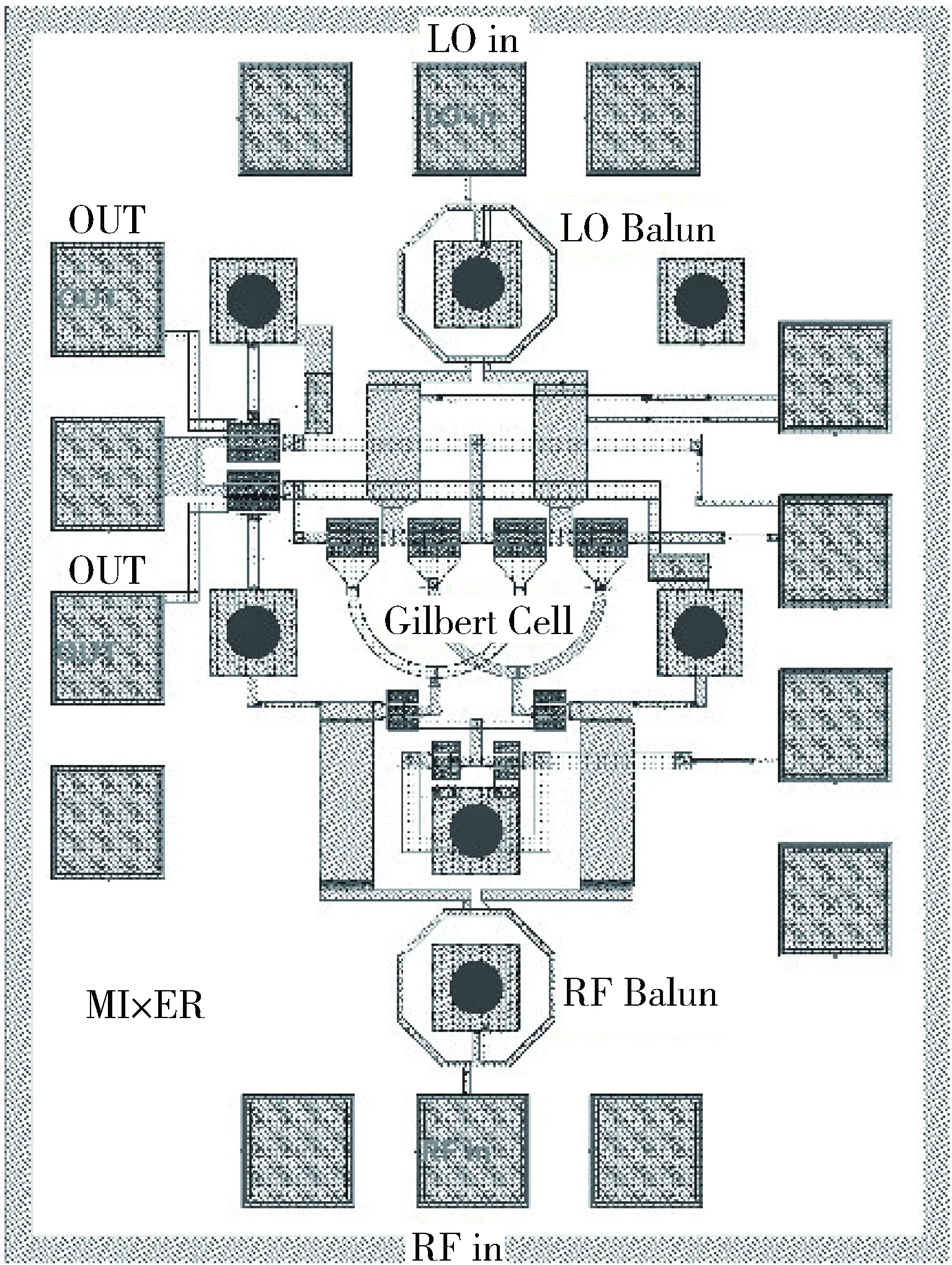

3 版图设计

芯片版图如图7所示,其中布线最困难的为高频段的差分布线,差分信号布线的对称性要求极高。在差分布线中要尽可能避免输入输出差分线有上下叠层覆盖,如果有覆盖,很容易产生耦合,会干扰输出信号的质量。振荡信号会使M3~M6开关管的栅极信号出现比较大的幅度不平衡,间接导致输出端对本振信号的隔离度。本文布版避开了振荡信号与中频输出信号的交叠。LO振荡信号从图7上端LO in焊盘输入,信号通过巴伦差分输送到M3~M6的栅极调控晶体管的开与关。RF信号由图7下方RF in焊盘输入,中频信号由图7左端OUT焊盘差分输出。

图7 芯片版图

4 仿真结果分析

本文混频器电路是基于厦门三安集成电路有限公司的P25ED 0.25 μm GaAs PHEMT工艺设计,最终的版图电磁仿真(EM)基于Keysight ADS2016平台的Momentum仿真工具实现,本文所述数据均为经电磁仿真后的数据。转换增益与射频功率曲线如图8所示。

图8 转换增益与射频功率曲线图

下变频混频器的转换增益为中频输出端功率与射频输入功率之差。图8是在振荡信号输入功率为0 dBm时的仿真结果。由图8可以看出在射频输入功率小于-5 dBm时,混频器的转换增益约为7.2 dBm。在射频输入功率大于-5 dBm时,混频器的转换增益开始衰减,当射频输入功率小于0 dBm时,按线性衰减,在射频输入功率约为7.5 dBm时,转换增益为0。

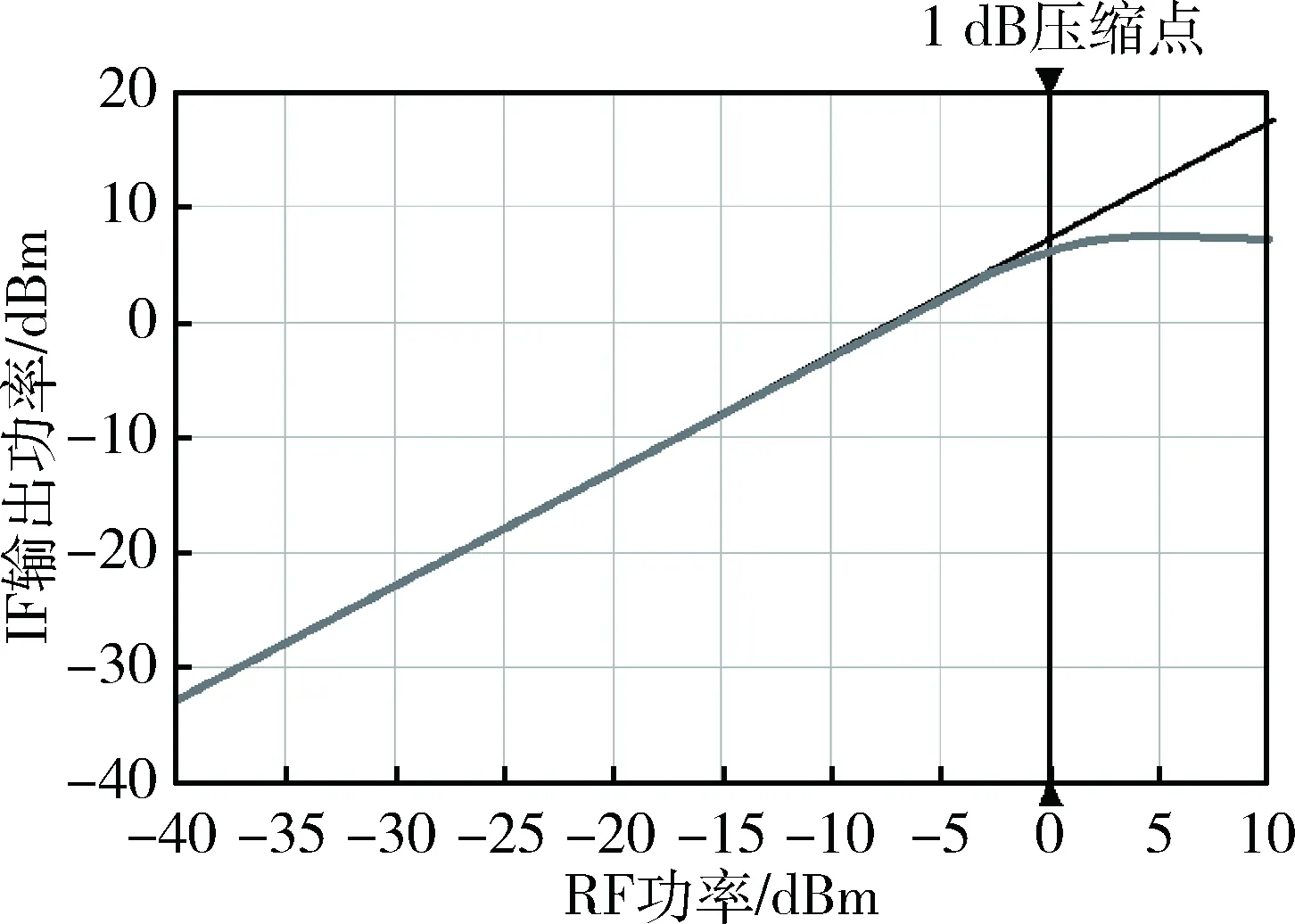

图9是1 dB压缩点的确定,该点定义为当输出信号的功率比基波的线性外推理论值降低1 dB处的功率输入值。随着射频频输入功率的变大,输出功率也在增大,在射频输入功率为0 dBm时,增益压缩1 dB,此点的输出大约功率为6 dBm,最大输出功率约为8 dBm。

图9 1 dB压缩点

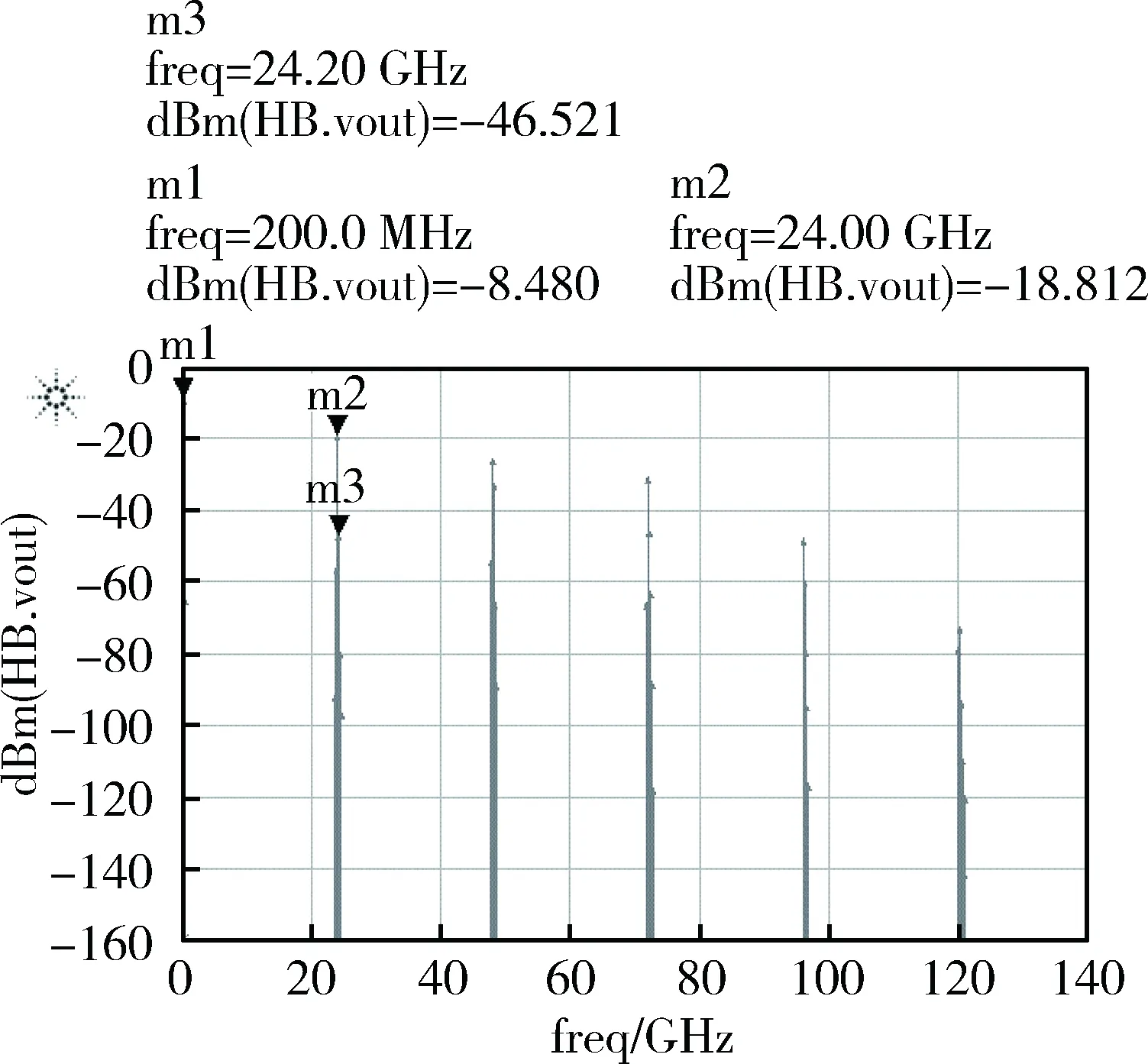

图10为混频器输出信号频谱图,其中m1为输出中频信号功率,m2为射频信号泄漏功率,m3为本振信号泄漏功率。为获得所需中频信号,只需在片外接低通滤波器即可滤除。

图10 输出信号频谱图

本文所设计的K波段pHEMT下变频混频器工作在中心频率为24 GHz,提供电源电压为5 V,本振信号输入功率为0 dbm时的性能参数如表1所示,与国内外其他文献相比,本文的设计具有合适的转换增益及良好的线性度,但相对来说面积稍大,且功耗稍高。

5 结论

本文应用PHEMT工艺设计实现了一款K波段的下变频混频器,由版图仿真结果看出,在LO功率为0 dBm时最大转换增益为7.2 dB,输入P1dB为6 dBm。与参考文献其他混频器相比,本文的设计部分性能较为良好,可为国产商用K波段混频器的设计提供一定参考。

表1 本文与部分文献的参数对比表

注:CG(Conversion Gain):转换增益;PLO:本振功率;P1dB:1 dB压缩点。

[1] ALVARADO U. 基于标准CMOS工艺的低功耗射频电路设计[M]. 黄水龙,王小松,刘欣,等,译.北京:国防工业出版社, 2013.

[2] LEE T H. CMOS射频集成电路设计[M].余志平,周润德,译.北京:电子工业出版社, 2006.

[3] 陈晓飞, 李小晶, 邹雪城,等. 带有源巴伦的CMOS宽带低噪声放大器设计[J]. 华中科技大学学报(自然科学版), 2013, 41(5):45-47.

[4] 李潇然, 仲顺安. K波段低噪声集成片上CMOS接收前端设计[J]. 北京理工大学学报, 2017, 37(3):287-291.

[5] SHI J, LI L, CUI T J. A 60 GHz broadband Gilbert-cell down conversion mixer in a 65-nm CMOS[C]// Electron Devices and Solid-State Circuits. IEEE, 2013:1-2.

[6] KRAIMIA H, TARIS T, BEGUERET J B, et al. A 2.4GHz ultra-low power current-reuse bleeding mixer with resistive feedback[C]// IEEE International Conference on Electronics, Circuits and Systems. IEEE, 2012:488-491.

[7] 谷江, 毛陆虹, 门春雷. 一种电流注入式零中频正交混频器[J]. 固体电子学研究与进展, 2012, 32(3):281-285.

[8] LI C H, KO C L, KUO M C, et al. A 7.1-mW K/Ka-band mixer with configurable bondwire resonators in 65-nm CMOS[J]. IEEE Transactions on Very Large Scale Integration Systems, 2017(99):1-14.

[9] CHANG Y H, HUANG C Y, CHIANG Y C. A 24GHz down-conversion mixer with low noise and high gain[C]// Microwave Integrated Circuits Conference. IEEE, 2012:285-288.

[10] AHN D, KIM D W, HONG S. A K-band high-gain down-conversion mixer in 0.18 μm CMOS technology[J]. IEEE Microwave & Wireless Components Letters, 2009, 19(4):227-229.

[11] CHIOU H K, KUO S C, CHUNG H Y. 14-30 GHz low-power sub-harmonic single-balanced gate-pumped mixer with transformer combiner in 0.18 μm CMOS[J]. Electronics Letters, 2014, 50(16):1141-1143.

[12] WANG S, CHEN P H. An active marchand balun and its application to a 24-GHz CMOS Mixer[J]. IEEE Transactions on Components Packaging & Manufacturing Technology, 2016, 6(10):1535-1541.

[13] AHN D, KIM D W, HONG S. A K-band high-gain down-conversion mixer in 0.18 $mu$m CMOS technology[J]. IEEE Microwave & Wireless Components Letters, 2009, 19(4):227-229.