基于APB总线的SPI接口设计与实现

刘梦影,王芬芬

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 引言

现如今,数字技术高速发展,许多芯片或作为核心器件用于数据交换,具有承上启下的数据交换枢纽作用,或用于集成电路之间进行数据存储和显示等[1]。为适应通信环境和高速的通信速率要求,通常使用多个微处理器完成信号的收发处理,因此需要一种高效的数据总线快速有效地完成它们之间大量的数据交换。因此,设计一个高效快速的通信接口是至关重要的[2]。

串行外围设备接口SPI总线技术是Motorola公司推出的一种微处理器、微控制器以及外设间的串行数据接口标准[3],主要用于扩展外设和进行数据交换[4]。SPI接口连线简单,配置灵活,传输效率高[5],因此应用广泛,很多器件如E2PROM、FLASH、实时时钟、A/D转换器等都用到了SPI接口[6]。郭艾华[7]设计了一种可灵活配置为主/从设备,设置传输速率,支持DMA功能并适用于多种时钟模式的SPI协议IP核,但从机片选信号只可由主机输出,存在一定的局限性。李琦、贺明等[8]以微处理器S3C2440和嵌入式Linux操作系统组成的嵌入式系统作为开发平台,设计了一款基于ARM嵌入式系统的SPI驱动程序,该设计存在两组8位移位寄存器,支持传输8位数据,但未有效地运用硬件资源。王珏文、金伟信等[9]将FPGA编程的灵活性和SPI总线的易用性结合,实现了FLASH的存取功能,SPI支持的工作模式较为单一。史星晟、王黎明[10]等采用msp430f149系列单片机作为主控,将数据通过SPI接口高速传输给无线传输模块,该SPI接口仅支持8位数据流与外设相互通信。朱道山[2]提出一种新型的可复用SPI接口设计方案,解决了SPI无法由从设备发起通信以及传输无反馈的不足,该设计仅验证了SPI作为发送端或接收端的通信,未实现全双工通信。为实现MCU和外部设备的高速通信,本文基于APB总线设计的一种SPI接口解决了上述设计中存在的问题。

文章首先简要阐述SPI的功能特点;其次描述了SPI模块的设计框架,且较为详细地分析主要子模块的工作原理,本文设计的SPI接口具有1个16位复用移位寄存器,节省硬件资源的同时提高了数据传输的整体速率,而且主设备根据状态机控制产生时钟,工作更加灵活。此外该设计不仅可配置为主/从设备,支持多种通信模式,结合多样性的通信格式和通信时序能满足更为复杂的外设通信要求。最后,采用Verilog HDL语言进行RTL设计,通过仿真验证了该设计的有效性和高效性。

2 SPI协议概述

SPI总线系统是一种同步串行外设接口,其允许MCU和外部设备同步串行通信,支持半双工通信、全双工通信和简单通信等工作模式,从而进行数据接收与发送,将串行数据转化为并行数据,或将并行数据转化为串行数据。通常,SPI通过4个引脚与外部设备连接。MISO为主设备输入引脚或从设备输出引脚,通常用于从设备的数据发送或主设备的数据接收;MOSI为主设备输出或从设备输入引脚,此引脚一般用于主设备的数据发送或从设备的数据接收;SCK作为主设备的串行时钟输出引脚或从设备串行时钟输入引脚;NSS则为从设备的片选引脚。

SPI模块与外部设备进行通信时,根据工作要求可配置MASTR设定SPI工作为主设备或从设备;配置BIDIMODE、BIDIOE和RXONLY设定SPI的通信模式为全双工模式、半双工仅发送、半双工仅接收、简单通信仅发送或简单通信仅接收。主设备可配置BR进而控制数据传输频率。

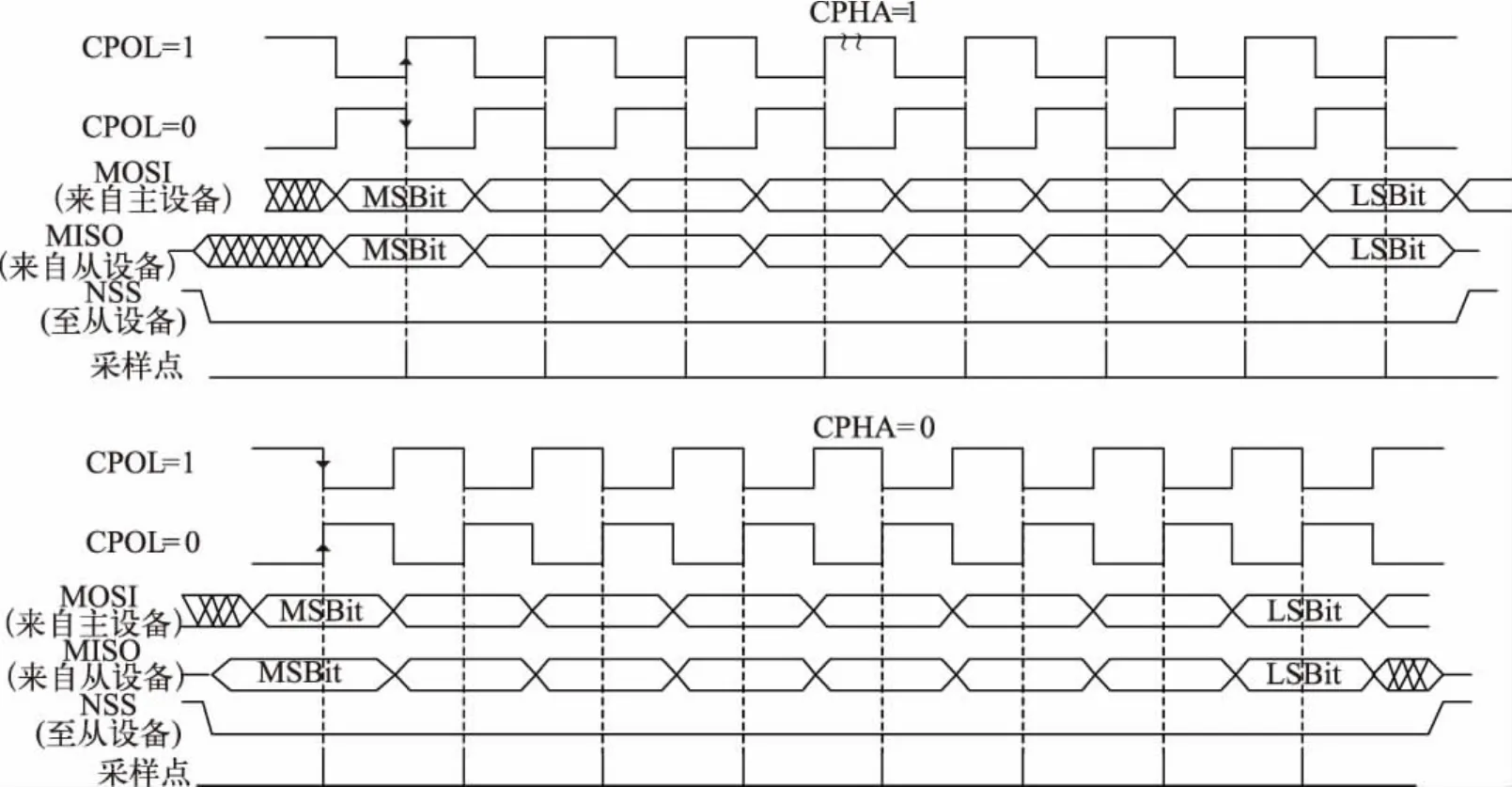

此外,时钟信号的极性(CPOL)和相位(CPHA)的任意配置致使SPI拥有4种传输时序,传输时序见图1。当CPOL=1、CPHA=1,即数据采样点位时钟上升沿,该时刻的数据为有效数据;当CPOL=0、CPHA=1,时钟下降沿的采样数据为有效数据。

图1 数据传输时序图

3 SPI模块设计

本文基于APB接口设计SPI,MCU可通过APB总线对SPI模块进行寄存器配置、数据读写和中断处理等操作,SPI接口则能够使MCU与外设接口进行数据串行通信。

3.1 设计框架

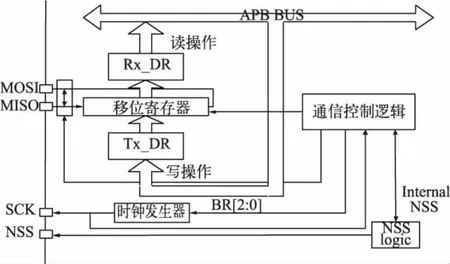

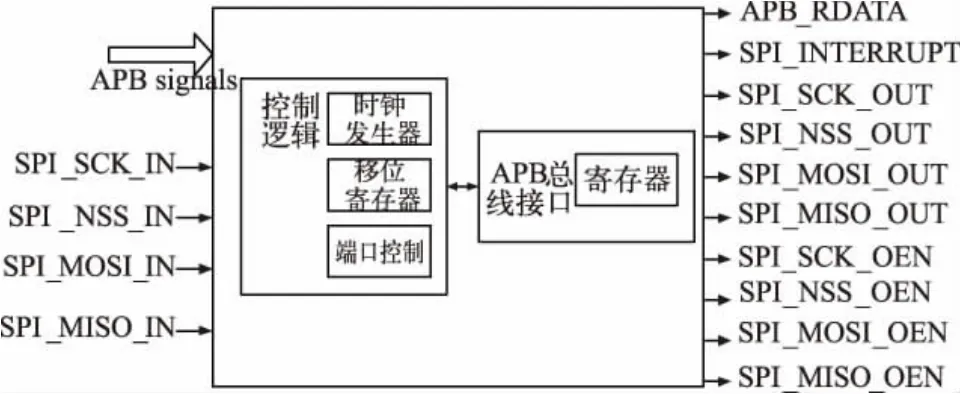

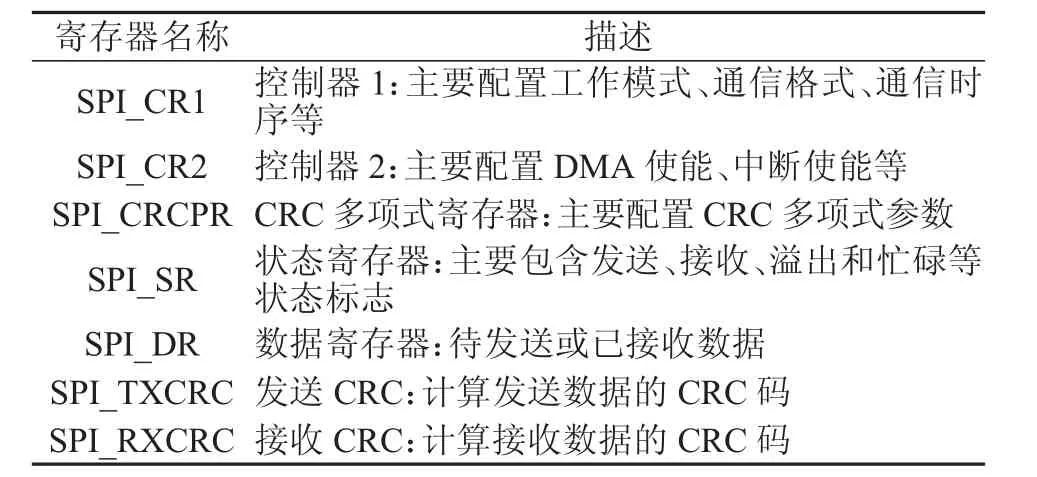

SPI接口的系统结构如图2所示,包括发送数据寄存器、接收数据寄存器、移位寄存器、主设备时钟生成器以及控制逻辑部分。基于该系统结构设计SPI电路,本文设计的SPI架构如图3所示,端口信号包括APB总线信号以及4个引脚的输入信号、输出信号及其输出使能信号,其中主要子模块包括APB接口模块、控制逻辑模块。SPI内部寄存器及功能描述在表1中简要列出。

图2 系统结构图

图3 设计架构图

表1 SPI寄存器描述

3.2 主要子模块设计

APB接口模块主要负责SPI寄存器的读写操作;控制逻辑模块的功能则较为复杂,主要涉及主设备产生串行时钟,移位寄存器串并转换数据、端口信号控制和状态信号控制等。

3.2.1 主设备时钟发生器控制

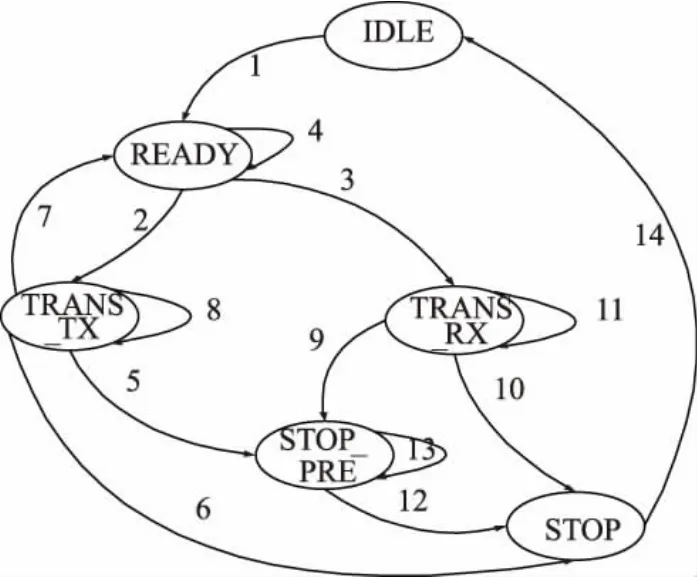

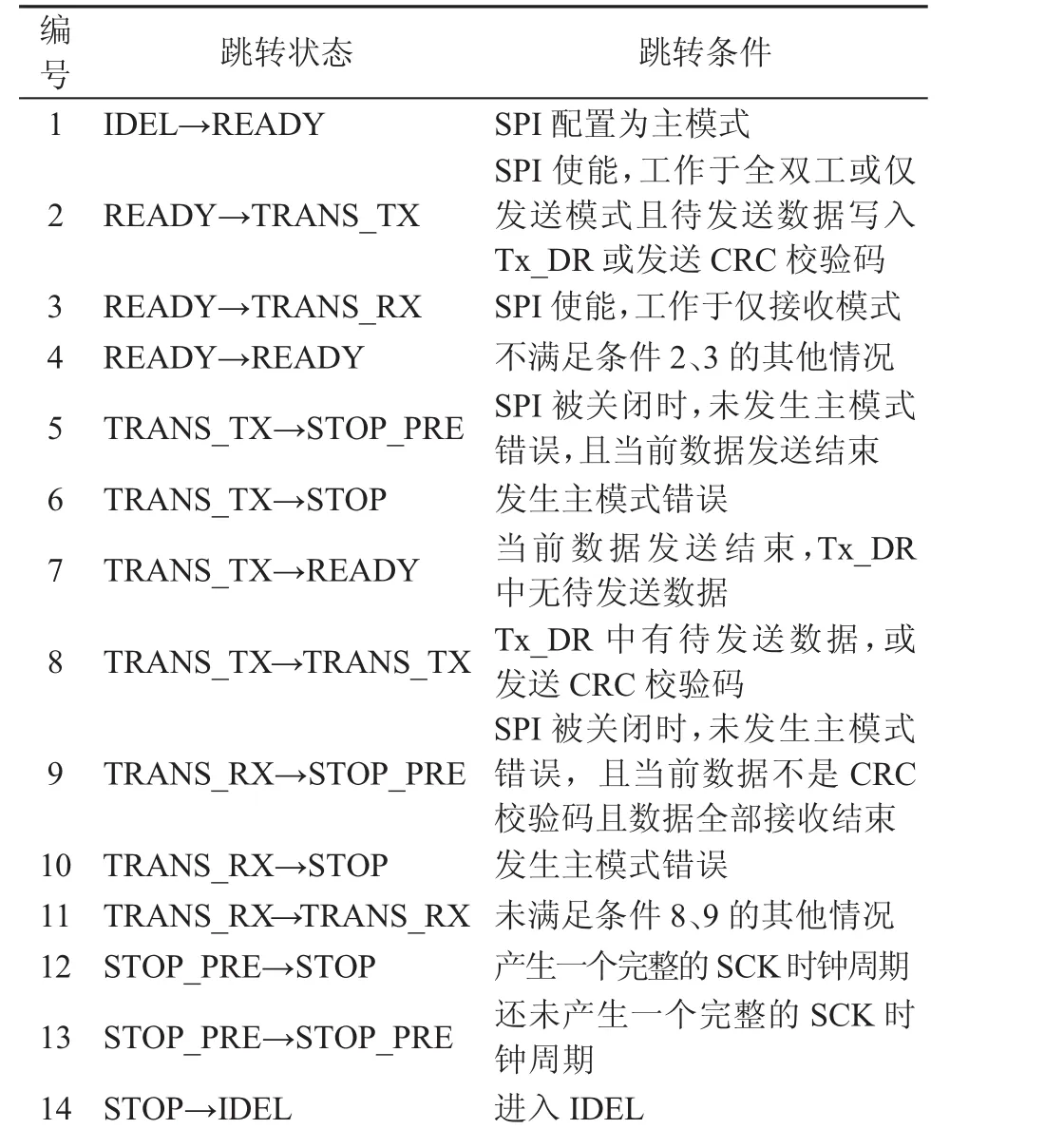

当且仅当SPI工作于主设备,则可产生并输出串行时钟SCK。如果该主模设备发送数据,且Tx_DR中已存入待发数据,那么主设备产生并输出时钟,否则无时钟产生;如果该模块仅接收数据,则连续产生并输出时钟。由于SPI工作模式存在多样性以及数据发送存在随机性,因此本文设计了一个状态机控制主机产生时钟与否。主模块时钟发生器状态图如图4所示。该状态机共包括6个状态,分别为:IDEL空闲状态;READY准备状态,即该SPI配置为主模式,但还未使能;TRANS_TX数据发送状态,即SPI工作为发送端或全双工模式时,数据经过移位寄存器通过总线与接收端进行通信;TRANS_RX数据接收状态,即SPI工作为接收端;STOP_PRE即将进入停止状态,即SPI被关闭,但数据传输还未完全结束;STOP停止状态。

图4 主机时钟发生状态机

如果当前状态为TRANS_TX或TRANS_RX或STOP_PRE,则允许主设备产生时钟。状态之间的跳转及其跳转条件在表2中简要地进行了阐述。

表2 状态机跳转条件

3.2.2 移位寄存器传输控制

移位寄存器传输结构不仅受SPI工作模式影响,且与数据帧格式相关。

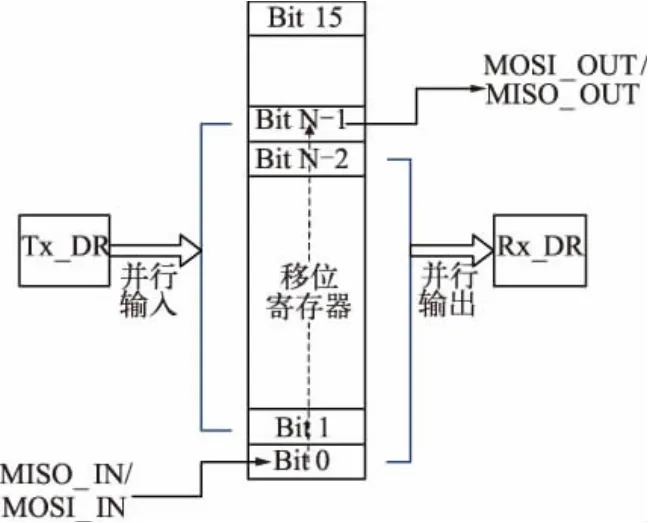

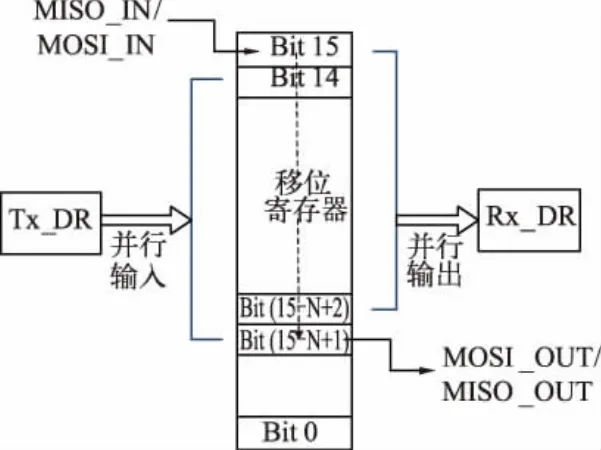

如果配置数据收发顺序为MSB首先收发(LSBFIRST=0),那么移位寄存器传输结构如图5所示。假设SPI工作模式配置为主设备的全双工模式,数据帧位宽N,待发送数据从移位寄存器的第N-1位串行输出至MOSI_OUT;同时,待接收数据串行通过MISO_IN输入至移位寄存器第0位。经过N-1个有效时钟周期,移位寄存器完成移位;最终发送数据串行输出至MOSI_OUT,且待接收数据并行锁存置Rx_DR,从而完成数据串/并转换。

图5 移位寄存器传输结构(LSBFIRST=0)

如果配置数据收发顺序为LSB首先收发(LSBFIRST=1),那么移位寄存器传输结构则在图6中绘出。工作原理与上述情况相似,但是接收的数据从移位寄存器的第15位串行输入,而待发送的数据则从移位寄存器第(15-N+1)位串行输出。

图6 位寄存器传输结构(LSBFIRST=1)

3.2.3 端口信号控制

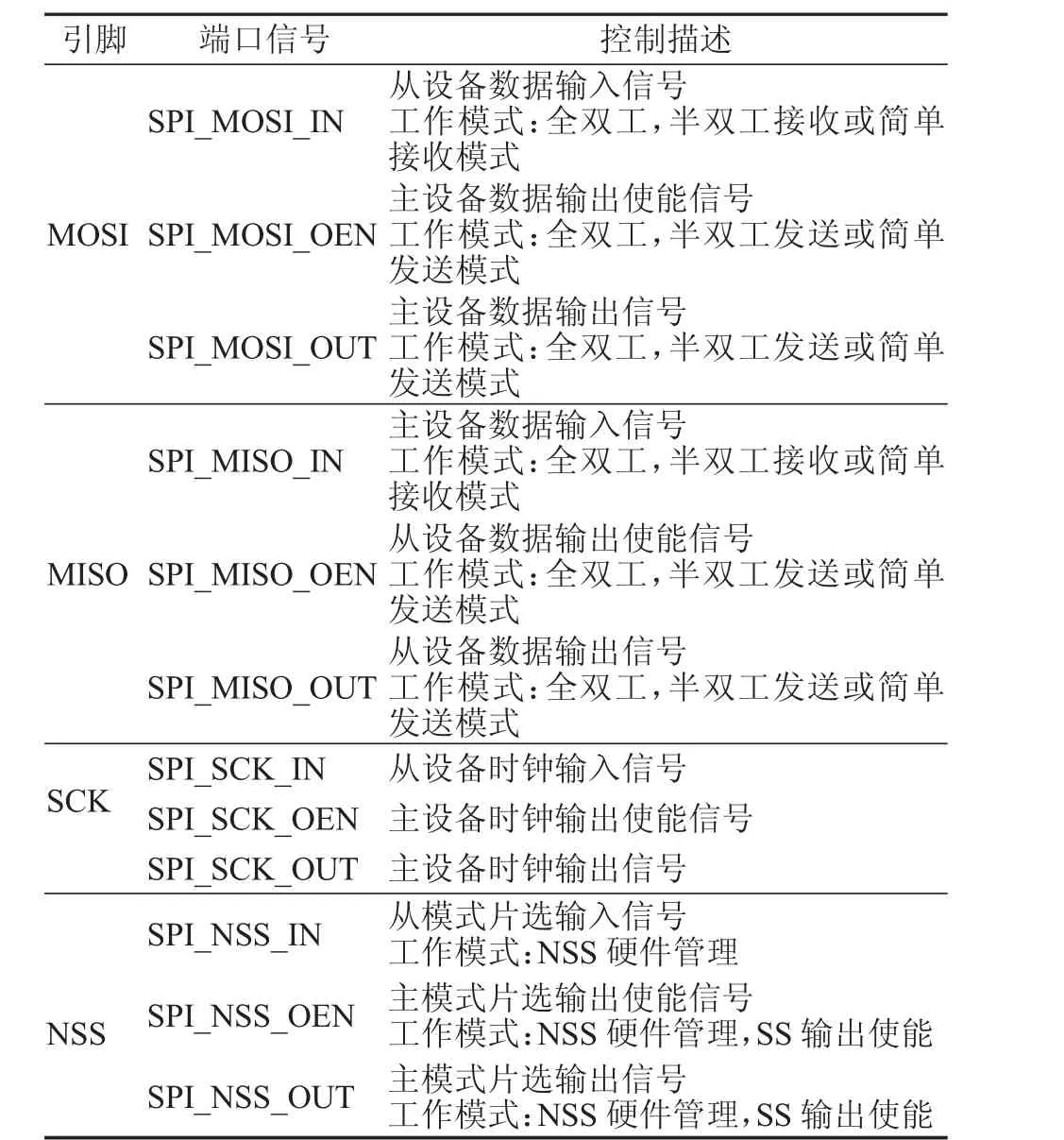

结合模块引脚和图3,SPI模块4个引脚可由对应输入信号、输出信号以及输出使能信号共同控制。各端口信号表示含义及其信号允许输入或输出的工作模式在表3中简要列出。

4 仿真结果

本设计采用Verilog HDL编写,使用ModelSim软件进行功能仿真,并用Debussy软件联合调试并观察波形。为实现主从设备通信仿真,例化一个SPI与外设进行通信。针对SPI的全双工通信、半双工通信和简单通信三种工作模式,同时结合不同的通信格式和时序,分别进行仿真。

表3 端口信号控制描述

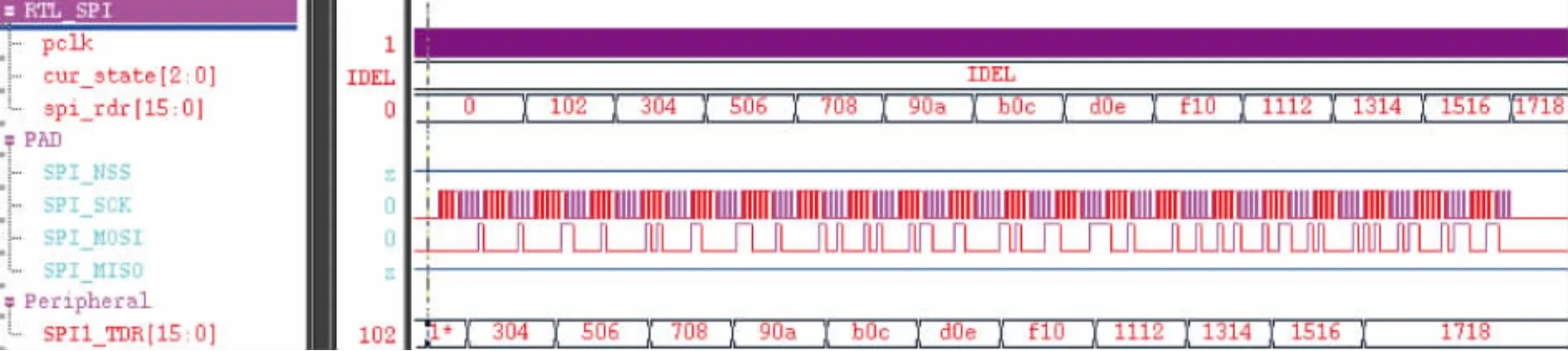

图7为SPI配置为主设备、全双工通信的仿真波形,片选信号NSS由软件配置,数据位宽为8位。配置CPOL=0,CPHA=0,因此在SPI_SCK上升沿采样数据。从仿真图中可发现,从机片选信号由软件配置,未占用NSS端口;此外,主设备不连续地发送数据,数据传输时进入TRANS_TX状态并产生SCK时钟,否则进入READY状态等待新的数据发送且不产生SPI_SCK时钟;主设备将spi_tdr的数据通过SPI_MOSI向从机串行发送数据,主设备通过SPI_MISO接收从机发送的数据并存入spi_rdr,主设备的spi_tdr与spi_rdr的数据分别与从设备的spi_rdr和从机的spi_tdr数据一致。

图7 全双工仿真波形

当SPI配置为主设备半双工仅发送模式,NSS由硬件配置并使能CRC计算功能,数据位宽为16位,配置CPOL=1,CPHA=0,因此在SPI_SCK下降沿采样数据。其仿真波形如图8所示,主设备通过SPI_NSS输出低电平至从设备,且连续发送数据和时钟,因此一直处于TRANS_TX状态,主设备通过SPI_MOSI将spi_tdr中的数据串行向从设备发送,最后一个数据则发送txcrc中的CRC校验码,从设备能够正确接收到主设备发送的数据以及与自身计算一致的CRC校验码。

如果SPI配置为从设备简单通信仅接收模式,数据位宽 16位,配置 CPOL=0,CPHA=1,因此在SPI_SCK下降沿采样数据。从图9的波形可发现,从设备的状态一致处于IDEL,未产生时钟,且能够正确地接收来自外设主设备的数据并存入spi_rdr。

图8 半双工仿真波形

图9 简单通信仿真波形

5 结论

本文运用Verilog HDL设计并实现了基于APB总线的SPI接口,通过SPI总线实现高速通信的系统。本文设计的SPI接口具有1个16位复用移位寄存器,不仅节省硬件资源,更能够提升数据通信的整体速率。此外,该SPI接口允许全双工、半双工和简单通信等多种工作模式,并支持多样化通信格式和通信时序,确保通信可靠性的同时具有更灵活的通信方式,能够满足复杂多变的外设通信要求;最后通过仿真验证了该设计的可靠性。

参考文献:

[1]易志明,林凌,郝丽宏,李树靖.SPI串行总线接口及其实现[J].自动化与仪器仪表,2002,6(104)∶45-48.

[2]朱道山.一种可复用的SPI接口设计与实现[J].通信技术,2017,50(2)∶389-392.

[3]高谷刚,罗春.可复用SPI模块IP核的设计与验证[J].单片机与嵌入式系统应用,2004(11)∶5-8.

[4]赵新雨,许忠仁,付贵增,朱文伟.基于FPGA与单片机的SPI接口的实现[J].工业仪表与自动化装置,2010(2)∶32-33.

[5]汪永琳,丁一.一种3线制半双工SPI接口设计[J].集成电路设计与开发,2010,35(5)∶482-484.

[6]匡春雨,马琪,陈科明.用于SoC的SPI接口设计与验证[J].现代电子技术,2013,36(24)∶149-151.

[7]郭艾华.基于APB总线接口的SPI协议IP核的设计与验证[J].无线互联科技,2013(11)∶132-134.

[8]李琦,贺明,董利民,董健.基于ARM嵌入式系统的SPI驱动程序[J].微型机与应用,2011,30(5)∶5-8.

[9]王珏文,金伟信,蔡一兵,颜莉萍.基于FPGA的SPI总线接口的实现[J].现代电子技术,2010,33(14)∶102-104.

[10]史星晟,王黎明,韩焱,姚金杰,王飞.基于硬件SPI总线的高速无线传输系统的设计[J].算法设计与应用,2012,20(12)∶3315-3316.