基于Virtex5的FPGA全覆盖五倍线确定性布线测试

李 光,谢 达,董宜平,胡 凯

(1.无锡中微亿芯有限公司,江苏无锡 214072;2.中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 引言

可编程逻辑器件FPGA的应用越来越广泛,对FPGA的测试也变得越来越重要。评价FPGA测试方法的好坏标准包括故障覆盖率、配置文件数、自动化程度。目前工业界测试为了达到特定目标,会精心设计每一个配置文件,确定性布线是一个重要方法。而学术界测试方法更关注自动化程度,他们一般设计复杂的测试优化算法自动生成配置文件[1]。

对FPGA进行确定性功能测试一般分为三个步骤:首先,给FPGA配置确定的配置文件;其次,在配置完成后,在相应的管脚施加外部测试向量;最后,通过观察输出管脚的结果来分析判断芯片的故障。

本文介绍了一种基于XDL(Xilinx Design Language)语言的FPGA确定性布线测试方法,对互联资源的五倍线进行测试。

2 Virtex5 FPGA的五倍线结构

Xilinx公司基于Virtex系统架构的xc5vlx330的FPGA, 包 括 IOB (Input/output Block)、CLB(configurable Logic Block)、CLB的互联开关盒 SB(Swith Box)等。基于以上架构的FPGA,IOB的物理位置位于左侧和右侧。

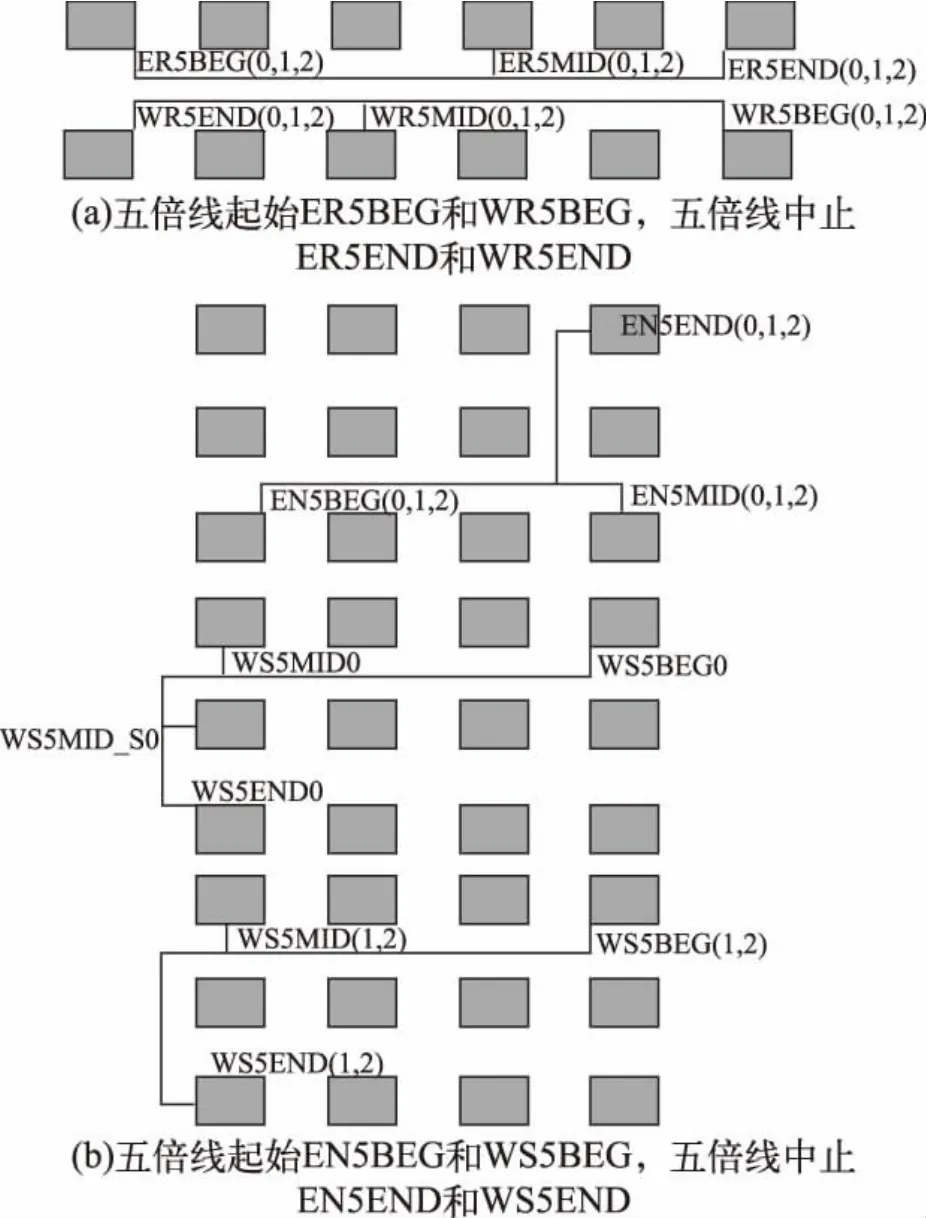

FPGA内部互联开关盒架构包括单倍线、二倍线、五倍线、长线等。V5LX330的五倍线共十六个方向,包括 ER(East Right)、WR(West Right)、EL(East Left)、WL(West Left) 四个水平方向,SL(South Left)、NL(North Left)、SR(South Right)、NR(North Right)四个竖直方向,EN(East North)、WS(West South)、NE(North East)、SW(South West)左下右上四个对角线方向和ES(East South)、WN(West North)、NW(North West)、SE(South East)左上右下四个对角线方向。每个方向三根线,图1以平方向和对角线方向各举一例作为说明。

图1 FPGA V5LX330内部五倍线示意图

3 FPGA布线资源典型故障和测试方法

FPGA功能测试主要分为CLB测试、互联资源测试和RAM测试。在FPGA芯片中,互联资源占据FPGA芯片面积的大部分(50%~90%),是FPGA资源中发生故障概率最高的部分。互联资源一般分为全局互联资源和局部互联资源,本文测试的五倍线资源属于全局互联资源。互联资源的故障一般有:(1)线段的固定型(stuck at)故障;(2)线段的开路(stuck open)故障;(3)线段间的桥接故障[2]。

本文提供的测试方法,针对五倍线互联资源,依据XDL规范进行自主确定性布线,对十六个方向的FPGA进行配对配置,从而形成FPGA的确定性五倍线全局布线。

4 XDL语言规则

4.1 XDL基本格式

XDL语言是赛灵思公司FPGA设计语言的简称,是Xilinx公司一种全功能的物理层设计语言规范。XDL由design声明、module声明、Instance声明和net声明四个声明构成,这四个声明构成了整个文件和电路的描述[3]。

Design声明在XDL是必须存在的,且只能存在一次。该声明包括一个全局的设计名称以及目标FPGA的部分名称。Design的格式如下:

design "V5LX330_WRERtest.ncd" xc5vlx330ff 1760-1 v3.2;

Module声明是一系列instance和net的结合,通常在hard macros里使用。本文不涉及。

Instance声明以关键词’inst’开头,元件类型主要有CLB、IOB、TBUF等几种类型,放置元件关键词placed,所在的 tile即所在的分区。对V5LX330CLB_X1Y0的Instance配置的实例格式如下:

Inst"INST_X0Y0""SLICEM",placed CLBLM_X1Y0 SLICE_X0Y0

Net声明由net、输入管脚 (inpin)、输出管脚(outpin)、PIP(Programmable Interconnect Point)等四部分组成。

4.2 使用XDL生成五倍线测试布线的步骤(以ER5 WR5为例)

使用XDL生成五倍线的测试布线分成五个步骤:步骤1将IOB的输入接入到五倍线的输入;步骤2将同一行同一个CLB的ER5和WR5首尾连接起来,如图2所示;步骤3将同一行不同CLB的所有ER5和WR5首尾连接起来,如图3所示;步骤4将五倍线的输出连接到下一行的输入,将相邻行的五倍线按步骤2相同的方法进行相接,直到所有的行做完;步骤5将五倍线的输出连接到IOB的输出上。

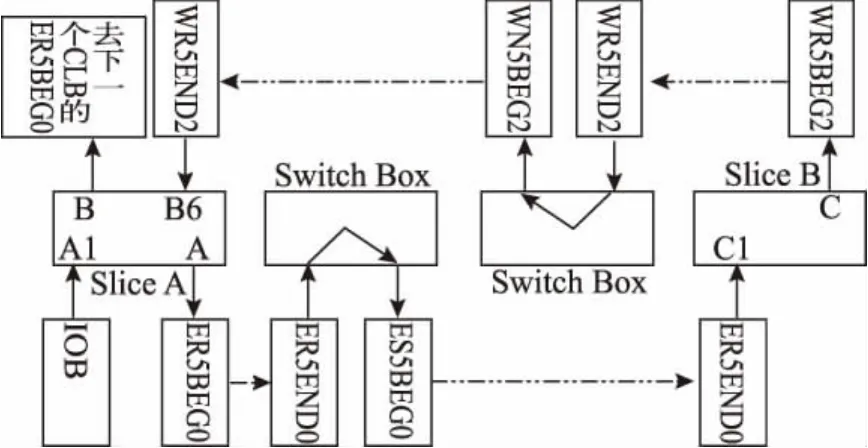

下面以ER50号五倍线ER5BEG0和WR52号五倍线WR5BEG2为例,各步骤如下:

步骤1将一个IOB管脚连接到五倍线的slice输入A1,如图2所示,其中INSTER0in为xc5vlx330的IOB,INST_X1Y0为CLB_X1Y0的 slice X1Y0:

net"NET_IOER0_in",

outpin"ER0_in"I,

inpin"INST_X1Y0"A1,;

步骤2如图2所示,完成同一个CLB内ER5的0号线五倍线和WR5的2号线五倍线的一个来回。

图2 FPGA五倍线布线步骤1和2

如图2所示,首先,通过slice A转接到ER5BEG0,然后ER5BEG0连接到ER5END0,ER5END0连接到ES5BEG0,再通过ES5MID0连接到 ER5BEG0,这样一直向东,直到最后一个ER5END0。然后ER5END0再经过Slice B连接到WR5BEG2进行回线,WR5BEG2和WR5END2相接,直到最后一个WR5END2。然后,WR5END2再接下一个 CLB的ER5BEG0。

实现步骤2中ER50号线从东到西布线的XDL语法如下,其中INST_X1Y0为SLICEX1Y0,INST_X215Y0为SLICE X215Y0。

net"CLB1NET_ER0Row0",

outpin"INST_X1Y0"A,

inpin"INST_X215Y0"C1,

pip CLBLM_X1Y0 L_A->SITE_LOGIC_OUTS8,

pip INT_X1Y0 LOGIC_OUTS8->ER5BEG0,

pip INT_X6Y0 ER5END0->ES5BEG0,

pip INT_X9Y0 ES5MID0->ER5BEG0,

……

pip INT_X118Y0 ER5END0->SR2BEG0,

pip INT_X118Y0 SR2BEG0->IMUX_B6,

pip CLBLL_X118Y0 SITE_IMUX_B6->L_C1,

pip INT_BUFS_L_X58Y0 INT_BUFS_ER5A0->INT_BUFS_ER5A_B0,

pip INT_BUFS_R_X59Y0 INT_BUFS_ER5A_B0->INT_BUFS_ER5A0,

pip INT_BUFS_L_X114Y0 INT_BUFS_ER5A0->INT_BUFS_ER5A_B0,

pip INT_BUFS_R_X115Y0 INT_BUFS_ER5A_B0->INT_BUFS_ER5A0,;

其 中 ,INT_BUFS_L_X58Y0、INT_BUFS_R_X59 Y0、INT_BUFS_L_X114Y0、INT_BUFS_R_X115Y0 是四个有向BUFFER连接。

ER5 0号五倍线ER5END0到达最东边的最后一个CLB后,通过该CLB的SLICE X215Y0的C输出,直接转角到WR5 2号五倍线的WR5BEG2上。WR5 2号五倍线从西到东的XDL布线如下,其中INST_X1Y0为 SLICE X1Y0,INST_X215Y0为 SLICE X215Y0。

net"CLB1NET_WR2Row0",

outpin"INST_X215Y0"C,

inpin"INST_X0Y0"D4,

pip CLBLL_X118Y0 L_C->SITE_LOGIC_OUT S10,

pip INT_X118Y0 LOGIC_OUTS10->WR5BEG2,

pip INT_X113Y0 WR5END2->WN5BEG2,

pip INT_X110Y0 WN5MID2->WR5BEG2,

……

pip INT_X6Y0 WN5MID2->WR5BEG2,

pip INT_X1Y0 WR5END2->SL2BEG1,

pip INT_X1Y0 SL2BEG1->IMUX_B22,

pip CLBLM_X1Y0 SITE_IMUX_B22->M_D4,

pip INT_BUFS_L_X114Y0 INT_BUFS_WR5C_B2->INT_BUFS_WR5C2,

pip INT_BUFS_L_X58Y0 INT_BUFS_WR5C_B2->INT_BUFS_WR5C2,

pip INT_BUFS_R_X115Y0 INT_BUFS_WR5C2->INT_BUFS_WR5C_B2,

pip INT_BUFS_R_X59Y0 INT_BUFS_WR5C2->INT_BUFS_WR5C_B2,;

步骤3把同一行内所有CLB的ER5 0号五倍线和WR5 2号五倍线连接起来,如图3所示。CLB1通过ER5 0号五倍线连接到CLB118,CLB118通过WR5 2号五倍线再回线到CLB1。CLB1中的WR5END2再连接到CLB2中的ER5BEG0,ER5 0号五倍线一直连接到CLB 111,CLB111通过WR5 2号五倍线再回线到CLB2……如此循环,把同一行的所有五倍线连接起来。

4.3 生成rbt文件

通过脚本程序将该方法扩展到整个FPGA,从而生成整个V5LX330的特定五倍线测试的确定性XDL布线,然后调用XDL命令,命令行格式为:XDL-xdl2ncd V5LX330_ERWRtest.XDL,从而生成了ER5和WR5五倍线测试的NCD文件V5LX330_ERWRtest.NCD。然后调用bitgen生成rbt文件,bitgen命令行的命令格式为:bitgen-b V5LX330_ERWRtest.NCD。

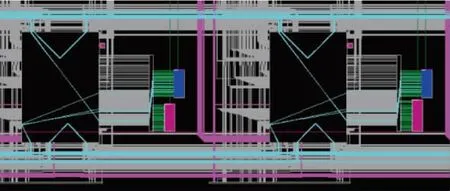

完整的V5LX330的FPGA东西向ER5和WR5的五倍线NCD部分图如图4所示,其中上方的连线包括了WR5BEG0~WR5BEG2,下方的连线包括了ER5BEG0~ER5BEG2,而 CLB上的连线为 ER5和WR5方向的转接线。

图3 FPGA五倍线布线步骤3

图4 完整的东西向五倍线ER5 WR5布线部分

5 使用测试向量对V5LX330进行测试

生成RBT文件后,对FPGA V5LX330进行配置,然后对输入侧对应ER5BEG0~ER5BEG2的IOB施加测试向量。如果对ER5 0号五倍线和WR5 2号五倍线进行测试,则施加(1,0,0)的测试向量,然后在对应输出端的IOB观察输出结果。如果输出为(1,0,0),则ER5 0号五倍线、WR5 2号五倍线无故障,如果输出不为(1,0,0),则ER5 0号五倍线或者WR5 2号五倍线有故障,记录输出结果。然后对ER5 0号五倍线再施加(0,1,1)的测试向量,然后在对应输出端的IOB观察输出结果。如果输出为(0,1,1),则ER5 0号五倍线、WR5 2号五倍线无故障,如果输出不为(0,1,1),则ER5 0号五倍线或者WR5 2号五倍线有故障,记录输出结果。

综合输出结果,故障类型初步判断为:

(1)输出结果始终为(0,0,0),则ER5 0号五倍线或者WR5 2号五倍线固定0故障或断路故障;

(2)输出结果始终为(1,0,0,),则 ER5 0号五倍线或者WR5 2号五倍线固定1故障;

(3)如果输入为(1,0,0),ER5 0号五倍线位置为1,而其他位置也出现了1,则出现了桥接故障。

6 结论

利用XDL脚本程序对五倍线进行确定性布线的方法,通过一次配置文件就能判断出故障。由于采用确定性布线,在布线时选择了所有能测试的五倍线,所以故障覆盖率可以达到100%。通过实施,发现确定性布线方法可以快速实现特定线段的测试,相对于自动化算法布线,具有应用快速、覆盖率可控的优势。

参考文献:

[1]代莉.基于布线资源图的FPGA互连测试算法[J].计算机工程,35(14).

[2]董宜平,谢文虎,李光.基于Virtex 4的全覆盖FPGA二倍线内建自测试[J].电子与封装,2017,17(1)∶19-23.

[3]Christian Beckhoff,Dirk Koch,Jim Torresen.The Xilinx Design Language(XDL)∶Tutorial and Use Cases[M].

[4]M Renovell,Y Zorian.Different Experiments in Test Generation for XILINX FPGAs[C].ITC INTERNATIONAL TEST CONFERENCE,2000,32.2∶854-862.

[5]Mehdi Baradaran Tahoori,Subhasish Mitra.Fault Grading FPGA Interconnect Test Configurations[C].ITCINTERNATIONAL TEST CONFERENCE,2002,22.2∶608-617.

[6]http∶//china.xilinx.com/[EB/OL].

[7]成飞.基于ATE的FPGA测试[D].上海:复旦大学,2011.

[8]王世颖.基于ATE的百万门级FPGA测试方法的研究[D].成都:电子科技大学,2012.

[9]张秀均,陈诚,孟祥媛.一种用perl编写Xilinx的FPGA内建测试向量的方法[J].电子与封装,2014,14(3)∶18-20.