测试成本的挑战及对策

章慧彬

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

集成电路测试是唯一贯穿于集成电路设计、制造、封装、应用全过程的产业,见图1。随着集成电路进入后摩尔时代,高复杂性、高集成度、高性能的产品给测试成本和难度带来了巨大的挑战。

图1 测试贯穿于集成电路制造全过程

2 测试经济学

为了保证产品的高质量,需要在产品研制过程中对每个测试阶段进行大量的投资,包括设备、场地、人力、技术等,这些投资即为测试成本。虽然产品质量要求测试投资尽可能多,但产品的经济效益(如成本)却限制了测试方面的投资,如何在保证产品质量的前提下尽可能降低成本,这就是测试经济学。

测试最本质的意义是检查产品与需求的一致性,即检查产品的“好”与“坏”,并将所有不合格产品在到达用户手中之前剔除出去。但是从测试经济学意义上看,测试还有一个价值就是要体现产品的经济性,如果测试成本居高不下,客户难以接受,产品就失去了生产的意义。有学者指出,未来的集成电路测试成本可达整个产品成本的40%~50%甚至更高。如何有效降低测试成本,就成了测试经济学的主要研究内容。

成本是可测量的数量,它在经济学中起着关键作用。成本主要包括固定成本和可变成本。总成本是指固定成本和可变成本的总和,随产量增加而增加;平均成本是总成本除以产量,平均成本随着产量的增加而降低。固定成本是必须的,并且不随着使用而改变,例如厂房和设备这些成本不随生产数量改变而改变,不管是生产100只电路还是生产10000只电路,固定成本保持不变,但分摊到每只电路上的固定成本却随着产量的增加而降低;可变成本是随产品的产量增加而增加,生产10000只电路的可变成本是生产100只电路的100倍,在这里可变成本通常由人力、能源和原材料的成本组成。

测试成本主要包括ATE成本、测试开发成本和DFT的成本。ATE成本属于固定成本,测试开发成本和DFT成本属于可变成本。若能将更多的可变成本转化成固定成本,随着产量的增加,就能降低单个产品的成本。将来,DFT将成为测试经济学的主导因素,扫描设计技术可以显著降低测试矢量生成成本,BIST方法可以降低ATE的复杂性和成本。因此,DFT技术就成为测试经济学中一个重要的研究内容。

3 集成电路产业链发展对测试成本的挑战

随着集成电路设计、工艺、封装技术的不断发展,在单个芯片上可以集成上亿个晶体管,时钟频率高达数十吉赫兹,同时集成数字电路、模拟电路;先进封装技术使得电路引出端数量增加,引脚间距越来越小,这些对集成电路测试的成本和难度都带来了巨大的挑战。

3.1 时钟速度提升对测试成本的影响

随着集成电路时钟频率呈指数级增长,全速测试(at speed test)将越来越重要。为了实施全速测试,ATE的频率必须与被测电路的频率一致甚至更高。所以,ATE不得不面临持续提高时钟速度的压力。然而,高速ATE非常昂贵。参考近几年ATE的价格,配置256个管脚数,施加测试激励频率从100 MHz提升到1.6 GHz的ATE,其价格从25万美元上升到了50万美元,从1.6 GHz提升到9 GHz,其价格上升到100万美元左右。因此,用这样的测试仪器进行高速测试的费用很高。测试设备硬件投资成本是进行电路全速测试需要考虑的问题。

3.2 高度集成对测试成本的影响

随着纳米制造技术的飞速发展,电路中晶体管的特征尺寸每年大约减小10.5%,晶体管的密度每年大约增长22.1%,再加上晶圆和电路的尺寸增长,晶体管密度几乎呈平方级增长,芯片面积与封装面积之比越来越接近于1。晶体管密度不断增长,使得在一个管芯上能集成越来越多的功能模块,电路的集成度越来越高,电路的引出端数量从数百PIN发展到数千PIN。参考近几年ATE的价格,一个能以1.6 GHz的频率施加测试激励的ATE,每增加一个测试引脚其价格就上升3000美元左右,ATE信号端口数量的增加导致ATE硬件成本快速增长,这也是测试必须考虑的问题。

3.3 混合信号集成电路对测试成本的影响

随着集成电路集成度的提高和消费类电子、汽车、通信等领域的发展,混合信号集成电路的需求不断上升,在一块芯片上集成模拟和数字电路的应用越来越广泛。电路类型不同,测试方法也不同,需要的测试资源也不同。这对ATE的需求也提出了更高的要求,不仅要满足高速数字逻辑测试需求,还要满足高精度模拟测试需求。数模混合ATE的成本随电路速度、精度要求的提升,成本更加凸显。因此,混合集成电路测试需求导致ATE硬件成本快速增长,也是测试必须考虑的影响。参考近几年ATE的售价,表1反映了ATE随管脚数、时钟频率、向量深度不同的价格增长趋势(仅供参考)。

从表1中可以看出,ATE的价格随ATE所能提供的管脚数、时钟频率、功能板卡种类数量和数据存储向量深度的增长呈现快速增长趋势。另外,ATE的发展技术永远都滞后于芯片的发展步伐,高性能ATE的价格也使得测试在产品总成本中的占比不断增加。随着产品功能越来越复杂、集成度越来越高,采用传统的ATE实施外部测试的方法所带来的测试成本已远远不能满足客户对复杂产品的测试成本要求,必须考虑将更加复杂的测试移到设计阶段。

本次抽水试验为单孔抽水试验,抽水试验孔SW01孔深为50.2 m,其中0~10.5 m为第四系橘子洲组(Qj)红色亚黏土层,其下部砾石层及松散的砂砾层厚度为8.5 m;10.5~50.2 m为泥盆系棋子桥组(D2q)灰岩,其中10.5~45.1 m岩溶裂隙发育,富水性较好,45.1~50.2 m岩芯较为完整,未见岩溶裂隙发育,富水性差。钻孔稳定水位埋深为10.2 m。

表1 ATE不同配置价格增长趋势

4 降低测试成本的对策

早期集成电路的测试主要依赖ATE实施外部测试,即通过ATE在电路的输入端施加测试信号源,在电路输出端观察输出响应的正确性。随着集成电路设计、工艺、封装技术的不断发展,集成电路的集成度越来越高,性能越来越复杂,仅有外部测试已不能满足要求,必须引入内部测试,即将电路测试的难度尽量在设计阶段就加以考虑和解决,从而降低测试成本。内部测试的关键技术就是可测性设计技术,将一系列复杂的测试问题移至设计阶段,由设计的领域来解决测试的问题,将一部分复杂的测试功能纳入芯片设计中,使芯片本身拥有测试该芯片部分功能的能力,从而大幅降低测试设备的复杂度以及测试成本。

4.1 积极发展可测性设计技术

可测性设计(design for testability,DFT)是在微电子芯片设计中加入了先进的测试设计,使得所涉及芯片的制造测试、开发和应用变得更为容易和便宜。可测性设计的目的是实现电路可测量性和可控制性。可测试设计技术的核心思想是在设计一开始就要考虑测试问题,通过适当增加一些专门用于测试的电路,提高电路测试的可控制性和可观察性,从而降低电路的测试难度和复杂性,提高电路的测试效率,降低测试成本。可测性设计常用方法主要包括扫描测试(scan chain test)和内建自测试(built-in test,BIST)。

4.1.1 扫描测试(scan chain test)

扫描测试技术是指通过对电路增加一个测试模式,当电路处于此模式时,所有触发器在功能上构成一个或多个移位寄存器,可以对电路中任一节点的状态移进或移出来进行测试定位,其特点是测试数据的串行化,测试数据从芯片输入端口经移位寄存器等组成的数据通路穿行移动,并在数据输出端对数据进行分析,以此来提高电路内部节点的可控制性和可观察性,使得本来很难测试的电路转化为容易测试的电路,从而降低测试矢量生成成本。扫描测试技术分为全扫描技术、部分扫描技术和边界扫描技术,针对这些技术都有专门的理论,这里不再详细介绍。

4.1.2 内建自测试(built-in test,BIST)

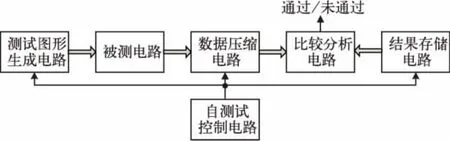

内建自测试技术就是在电路内部建立测试生成、施加、分析和测试控制结构,使得电路能够自身测试。内建自测试通用结构图如图2所示。

图2 内建自测试通用结构图

(1)可提供层次化解决方法,有效测试电路内部各功能模块和互联,减少全速测试对ATE时钟频率的要求;

(2)可提高测试故障覆盖率,单个故障覆盖率达98%,互连故障覆盖率达100%;

(3)可进行局部化测试,解决复杂电路可观测性差的问题,减少对ATE复杂性的要求;

(4)可在电路中设计无限的测试点;

(5)BIST能力随工艺进步而增强,而对于外部测试,测试能力总是落后于工艺能力,即ATE技术总是滞后于工艺技术;

(6)BIST可以使用CAD工具自动加到电路中,可提供90%~95%的故障覆盖率,甚至可达99%,减少了对ATE数据存储向量深度的需求。

4.2 研发标准化的EDA接口测试技术

随着芯片功能复杂度的进一步增加,测试复杂度也在随之上升。设计、测试之间如果没有一个有效、紧密的结合,很容易会产生测试困难并增加测试成本,如测试结果不准确、测试问题难以定位、测试时间长、测试结果难以反标到设计/工艺生产中等问题,加快研发与芯片可测性设计相结合的ATE设备一体化测试解决方案,实现ATE无缝对接DFT输出文件,是降低测试成本的有效方式。

5 总结

随着集成电路复杂度的提高和特征尺寸的日益缩小,特别是进入纳米级超高集成度的发展阶段,通过集成各种IP核,系统级芯片的功能更加强大,未来的测试有很多尚未解决的挑战,不断提升测试技术,寻求降低测试成本的有效方法,是发展集成电路测试的首要目标。

参考文献:

[1]Michael LBushnell.超大规模集成电路测试[M].北京:电子工业出版社,2005.

[2]雷绍充.邵志标VLSI测试方法学和可测性设计[M].北京:电子工业出版社,2005.

[3]高成,张栋.最新集成电路测试技术[M].北京:国防工业出版社,2009.