一种自适应补偿的宽输入LDO设计

严利民,殷晓文

(上海大学 微电子研究与开发中心,上海 200072)

在各类便携式电子设备中,低压差线性稳压器(Low Dropout Linear Regulator, LDO)的主要功能是为系统提供可靠稳定的基准电压[1-2].其中宽输入的LDO芯片,直接起到直流转换器(Direct Current-Direct Current converter, DC-DC)的降压作用,特别是在锂电池系统中,电源电压跨度大,宽输入LDO能够很好地匹配不同电池组的电压域,而且减少了成本[3],增加了芯片的市场应用范围.而且相较于DC-DC,LDO输出精度高,纹波小,能够更好地在输出端抑制噪声,并且不会产生电磁干扰(Electromagnetic Interference, EMI)问题[4],可以用来驱动敏感负载.此外,在实际应用中,当负载条件变化时,系统内极点变化使得LDO的稳定性补偿变得困难,自适应技术能在电路内产生一个随负载变化的零点[5],以抵消在不同负载条件下极点变化带来的影响,确保整个系统的稳定性,使得芯片可以在全负载范围下工作.本文基于CSMC 0.35μm HV40V标准CMOS工艺设计了一种自适应补偿的宽输入LDO,采用共源共栅运算跨导放大器(Operational Transconductance Amplifier, OTA)作为误差放大器(Error Amplifier,EA)和超级源随器(Super Source-follower)技术,设计了一种输入范围4.5~24V,系统稳定输出为4V的LDO.电源从4V变化到24V时,线性调整率为2.375mV/V,在1μA到20mA负载范围下,负载调整率最差为0.05V/A.可以看出,设计的LDO综合性能良好.

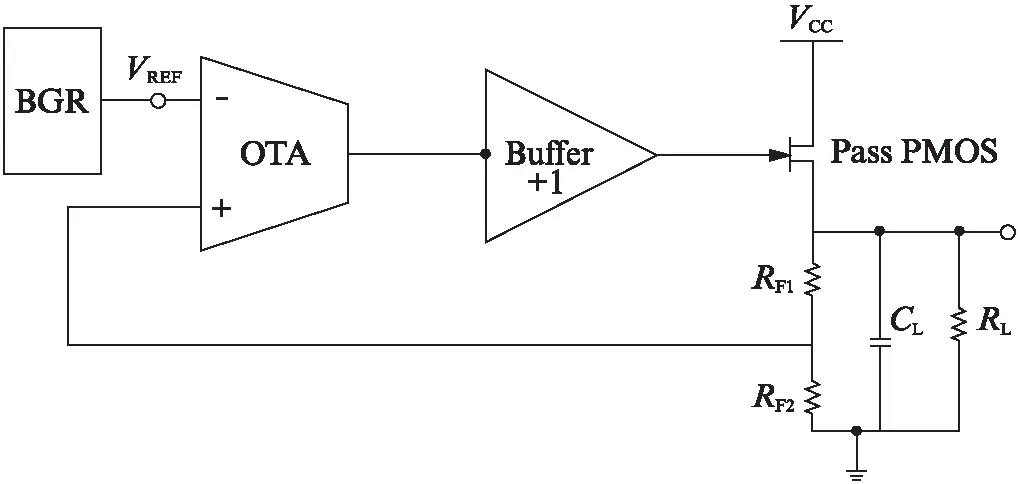

1 LDO系统原理

自适应补偿的宽输入LDO主要包括: 高压带隙基准(Bandgap Reference, BGR),跨导放大器作误差放大器,缓冲器(Buffer),PMOS调整管作为系统的输出级,输出端为Vdda.图1(看86页)为LDO的电路结构.其中,在负反馈条件下,运算跨导放大器根据不断比较基准电压VREF和经电阻网络RF1和RF2反馈回来的电压来实时调节调整管的栅级电压从而稳定输出.

LDO的核心电路结构如图2(看86页)所示,其中第一级为自偏置高压带隙基准,因为是中高压应用情景,所以采用折叠共源共栅结构.高输出阻抗带来的屏蔽特性能够减少电源输入跳变对系统的干扰.

电路通过一个自偏置的启动电路摆脱简并点,当电源输入升高时,PM3和PM4导通,电流镜像至高压管PM5,短时间内抬高支路电压,当PM8,PM9支路电流建立起来之后,PM1和PM2进入线性区,RST电位接近电源电压,将PM5支路关断.最终VREF端输出1.25V基准电压.

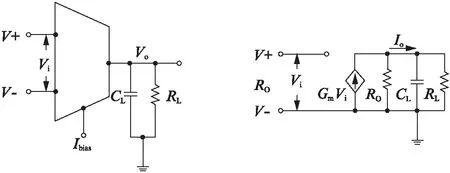

第二级为单端输出的对称型运算跨导放大器,NMOS电流镜作有源负载,差分输入对,PM18和PM19支路的电流分别镜像到NM7和NM12支路中,电流由输入器件产生,被放大了镜像比例α倍(α为NM8支路与NM9支路的电流比值,这里设置为4),流进输出负载.可以将运算跨导放大器等效为图3的小信号电路,很容易得到它的低频增益.

图1 电路结构Fig.1 The structure of circuit

图2 整体电路图Fig.2 Core circuit

图3 OTA等效电路模型Fig.3 Equivalent circuit model of OTA

小信号输入为Vi,输出电压为Vout,输出电流为Io,偏置电流为Ibias,Gm为电路等效跨导,gm为MOS管跨导,下标即为MOS编号,ω0为截止频率,rds为沟道长度调制效应电阻,CL为负载电容,RL为负载电阻并联.首先可以得到运算跨导放大器的跨导表达式为:

(1)

由此可得到电路的传输函数Av(s)为:

(2)

在式(2)中,s为拉普拉斯变换.由于共源共栅结构的存在,节点V1的阻抗乘上了(1+gm×rds)因子,因此运放的输出阻抗Ro,OTA为:

Ro,OTA=gm,NM11×[(1+gm,NM12rds,NM12)×rds,NM11+rds,NM12].

(3)

经过后续仿真验证,虽然是单级的放大器,但经过电流因子α和共源共栅本征增益放大后的输出阻抗可以保证运放增益可以达到60dB.此外,两端输入具有相同的直流电压和负载阻抗也提高了匹配,提供了更好的失调和共模抑制比(Common-Mode Rejection Ratio, CMRR)特性[6].

2 稳定性分析

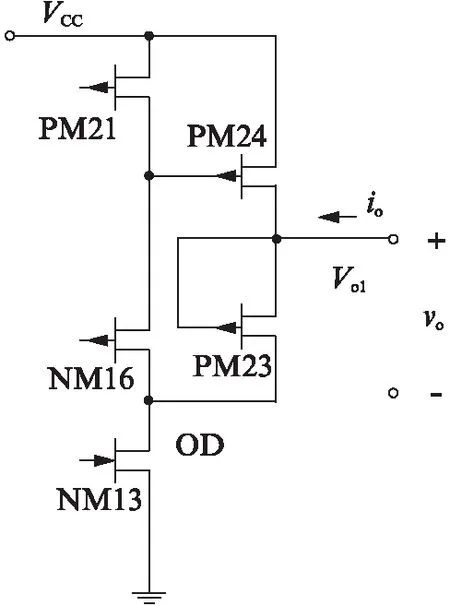

Vo1是高阻抗节点,因为PM27作为输出级,本身寄生电容比较大,所以Vo1在此处产生一个低频次主极点,如式(4)所示:

(4)

图4 超级源随器Fig.4 Super source-follower

但是这个极点的存在会降低系统的相位裕度,我们希望将这个次主极点向右平移到单位增益带宽之外,所以在放大器的输出端加上一个缓冲器,隔离运放输出端的高阻点和PMOS传输管栅端大的寄生电容[7],降低Vo1点阻抗.从而提高误差放大器的电流驱动能力.

(5)

(6)

增加反馈环路后,输出电流变化为式(7).最终得到输出电阻为式(8):

(7)

(8)

(9)

(10)

NM15工作在深线性区,所以NM15阻值大小为式(11),其中μn代表电子迁移率,Cox为单位面积栅氧化层电容.

(11)

(12)

将RNM15带入零点Z后,得到自适应补偿之后的零点表达式和主级点表达式如式(13)、(14).

(13)

(14)

3 LDO整体仿真结果

整体电路的设计和前仿采用Cadence Spectre以及H-spice完成,版图设计和后仿采用Cadence Virtuso工具完成.库文件使用的是CSMC 0.35μm HV40V标准CMOS工艺.工艺角为tt.图5是当负载电流分别为1μA和20mA时,LDO的稳定性仿真.

当负载电流为1μA时,低频增益约为103.0dB,相位裕度为80.81°,系统稳定.图中可以看出在单位增益带宽内只有一个输出端的主级点,说明经过缓冲器的作用,节点Vo1产生的极点被成功移出单位增益带宽外.

当负载电流增大为20mA时,可以看出主级点右移,直流增益下降为77dB,输出级零点Z跟随极点P1变化,向右半平面移动,依然可以保证LDO系统稳定,相位裕度为80.81°左右.仿真结果表明自适应补偿网络具有良好的跟随性.

图5 负载电流从1μA变化至20mA的波特图Fig.5 Bode plots of the load current varying from 1μA to 20mA

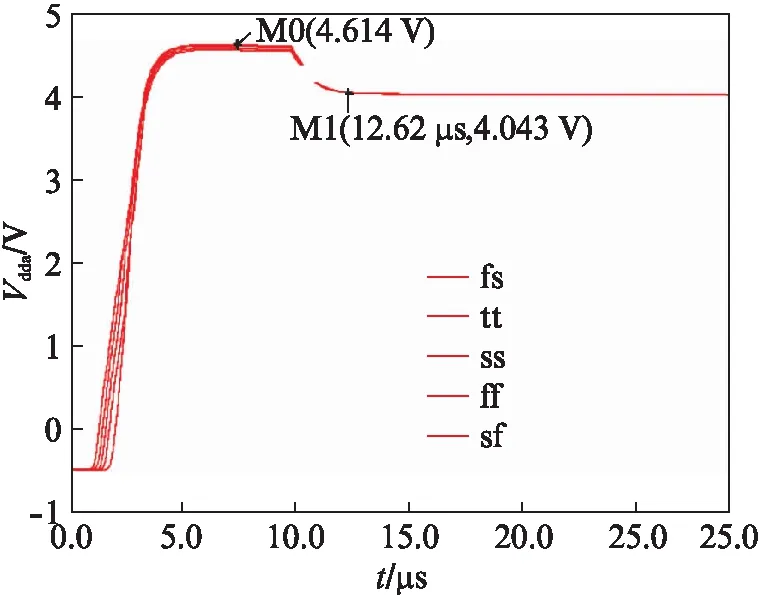

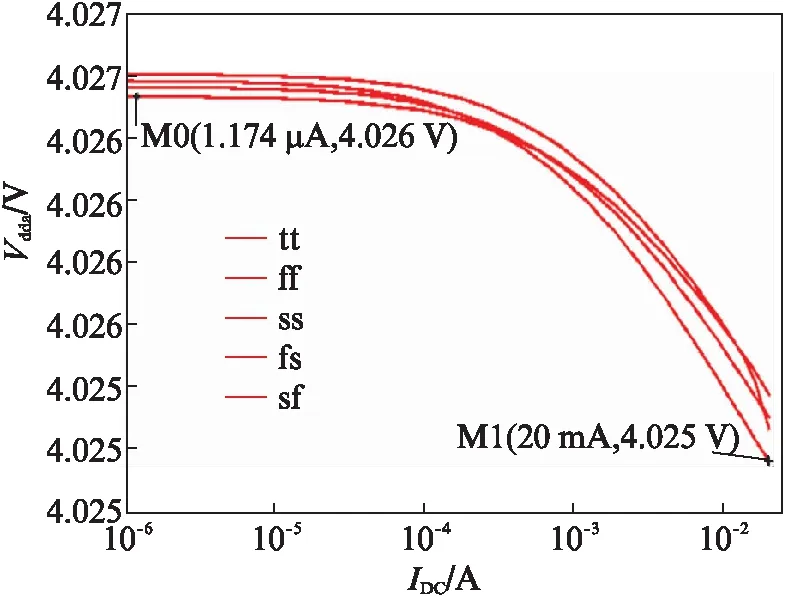

图6是线性调整率仿真图,仿真条件为当负载电流为20mA时,电源输入分别从0~35V,结温分别为-40,25,40,70,125℃时不同工艺角下的调整管输出电压Vdda.可以看出在不同环境下,仿真曲线基本重合,在125℃,工艺角为ss的最差情况下,电源输入接近4.3V时,输出Vdda建立压差(drop-out)为271mV.同样在最差条件下,电源输入从4.5V到24V,输出Vdda只变化19mV,线性调整率满足需要.图7为极快速上电仿真结果.由于输入电压为0~24V,存在中高压应用情况,所以需要保证在快速上电情况下,电路输出不发生较大的过冲.仿真时,设置电源输入从0~24V,上升时间为10μs,在不同工艺角下模拟快速上电情况,Vdda在12.57μs内即可稳定下来.可以看出在有限的电源抑制比(Power Supply Rejection Ratio, PSRR)下,电源输入VCC变化斜率过快时,Vdda会有过冲,最差情况下(工艺角为sf)最大值可以保持在4.7V以下,因此对内部电路不会有安全性问题.

图6 线性调整率Fig.6 Linear adjustment rate

图7 快速上电情况Fig.7 Fast power on

图8和图9分别体现了此LDO的带载能力及稳定性,电源电压取临界值4.5V,电流负载从1μA变化到20mA,工艺角为sf的最差情况下,输出Vdda变化1mV左右,得到负载调整率为0.05V/A.同样在电源电压下,电流负载从0mA跳变到20mA再跳变到0mA,图9中可以看出负载由轻转重时,输出电压下降71mV,稳定时间为1.15μs;重载转轻载时,输出变化120mV,稳定时间1.91μs.表明该LDO完全可以满足对负载变化的响应.

图8 负载调整率Fig.8 Load regulation rate

图9 瞬态响应Fig.9 Transient response

图10为版图图片,采用CSMC 0.35μm HV40V标准CMOS工艺,面积大小为550μm×300μm.版图中对主要运放的输入对管以及带隙基准模块中的电阻进行了匹配.

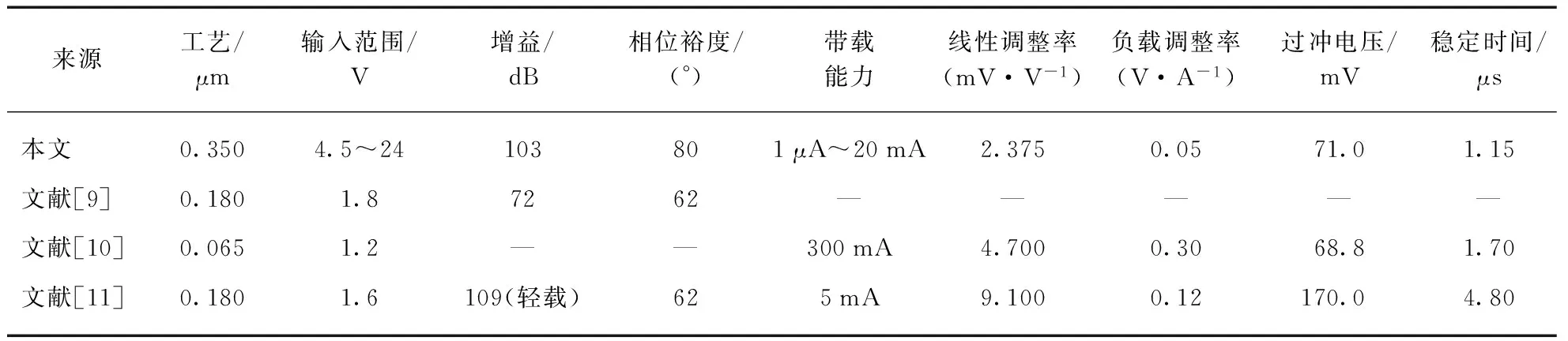

本文设计的LDO与文献[9-11]中LDO的性能参数进行对比,对比结果表明本文设计的LDO有着更宽的输入范围,在负载范围内有着更好的线性调整率和负载调整率,在负载突变时稳定时间更短,体现了良好的负载特性.

表1 本文LDO与其他文献的性能参数比较

4 结 论

采用基于CSMC 0.35μm HV40V标准CMOS工艺设计了一种能够自适应补偿的宽输入LDO,文中给出了超级源随器和自适应补偿网络的电路结构,并进行了详细的电路推导.经过仿真验证,该LDO在1μA到20mA的全负载范围下,LDO的相位裕度都在80°以上,体现了自适应网络具有良好的极点跟随性.在电源输入范围4.5~24V,负载电流为20mA时,输出稳定在4V,并且在快速上电模式下,输出过冲不超过5V,不会出现安全性问题.负载调整率和线性调整率均满足要求.综上是一款良好的宽范围LDO,能够应用于多种电压域场景.

参考文献:

[1] MIHHAILOV J, STRIK V, STRIK S, et al. Low noise LDO architecture with consideration for low voltage operation [C]∥Electronic Conference(BEC), 2014 14thBiennial Baltic. Tallinn, Estonia: IEEE Press, 2014: 41-44.

[2] GUPTA H, MISHRA G K, RIZVI N Z, et al. Design of high PSRR folded cascode operational amplifier for LDO applications [C]∥International Conference on Electrical, Electronics, and Optimization Techniques(ICEEOT). Chennai, India: IEEE Press, 2016: 4617-4621.

[3] MARTINEZ-GARCIA H. Cascoded OTA based low dropout(LDO) voltage regulator [C]∥Emerging Technology and Factory Automation(ETFA). Barcelona, Spain: IEEE Press, 2014: 1-5.

[4] WANG Z, ZHOU C, LIU T, et al. Nonlinear behavior immunity modeling of an LDO voltage regulator under conductedEMI [J].IEEETransactionsonElectromagneticCompatibility. 2016,58(4): 1016-1024.

[5] HAN X, BURGER T, HUANG Q. An output-capacitor-free adaptively biased LDO regulator with robust frequency compensation in 0.13 μm CMOS for SoC application [C]∥2016 IEEE International Symposium on Circuits and Systems(ISCAS). Montreal, QC, Canada: IEEE Press, 2016: 2699-2702.

[6] SANSEN W M C. Analog design essentials [M]. 1st ed. US: Springer Science & Business Media, 2007: 147-148.

[7] SUBBIAH I, ELNEEL N A, VARGA G, et al. Low power on-chip load tracking-zero compensation method for low dropout regulator [C]∥New Circuits and Systems Conference(NEWCAS), 2015 IEEE 13thInternational. Grenoble, France: IEEE Press, 2015: 1-4.

[8] HOLDER M E. Thevenin’s theorem and a black box [J].IEEETransactionsonEducation, 2009,52(4): 573-575.

[9] GUPTA H, MISHRA G K, RIZVI N Z, et al. Design of high PSRR folded cascode operational amplifier for LDO applications [C]∥Electrical, Electronics, and Optimization Techniques(ICEEOT), International Conference on. Chennai, India: IEEE Press, 2016: 4617-4621.

[10] KIM Y, LEE S. A capacitorless LDO regulator with fast feedback technique and low-quiescent current error amplifier [J].IEEETransactionsonCircuitsandSystemsⅡ:ExpressBriefs, 2013,60(6): 326-330.

[11] WANG J H, TSAI C H, LAI S W. A low-dropout regulator with tail current control for DPWM clock correction [J].IEEETransactionsonCircuitsandSystemsⅡ:ExpressBriefs, 2012,59(1): 45-49.