红外焦平面信号读出及处理技术

李敬国,卓 毅

(华北光电技术研究所,北京 100015)

1 引 言

随着红外探测器及集成电路技术的发展,作为红外探测器组件核心部件的读出电路正朝着第三代焦平面读出电路的方向发展,其主要特点是大面阵、小间距、高帧频、数字化、大电荷处理能力等。焦平面读出电路信号处理技术在提高了组件小型化、智能化水平的同时,大大提高了组件的动态范围和信噪比,提高了系统的灵敏度。

2 读出电路关键性能指标

读出电路的典型工作原理如图1所示,其主要功能是对红外探测器的电流信号进行积分,电荷电压转换、放大,最后经过时序选通缓冲放大器输出。

读出电路一般通过铟柱倒装互连的形式与红外探测器连接,封装在真空杜瓦适配制冷机,形成了红外探测器组件。表征其图像质量的两个关键性能指标分别为动态范围与信噪比。

图1 读出电路工作原理图Fig.1 Readout circuit schematic

动态范围定义为最大的非饱和信号与无光输入条件下组件噪声之比,参见公式(1),动态范围大的组件通常会产生高的图像质量[1]。

(1)

(2)

虽然,平均噪声功率会随着光信号iph增加而增加,SNR还是会单调增加;刚开始,读出电路噪声占主导时,SNR以20 dBs/dec斜率增加;最终,散粒噪声占主导时,SNR以10 dBs/dec斜率增加。

组件的动态范围、信噪比与红外探测器暗电流水平、读出电路的电荷处理能力、读出电路噪声水平直接相关。对于低背景、弱目标应用而言,读出电路噪声水平至关重要,其噪声水平由读出电路输入级噪声水平决定。

3 读出电路输入级技术

根据应用背景不同,通常会选用不同的输入级结构,读出电路的输入级结构主要有源随结构、直接注入结构、CTIA结构。图2为源随输入级结构[2]。

图2 源级跟随器输入级原理Fig.2 Source Follower input stage schematic

源随输入级结构的主要特点是光电二极管复位后,光电流直接在输入节点电容上进行积分,积分节点电压通过开关源随结构读出,通常情况下,每列源随结构公用一组电流源。由于输入节点电容主要是由光电二极管节电容组成,节点电容会随着积分节点电压而变化,因此源随输入级结构的主要缺点是先天存在非线性特征,同时二极管偏压的不恒定导致像素之间电容效应。另外,由于未与读出电路去耦,二极管偏置电压会受到读出电路各种电效应的影响,比如电耦合、电荷注入。

源随输入级结构除了复位噪声,源随MOS管是唯一的像素噪声来源,其输出噪声为热噪声,其值参见公式(3),在大规格阵列中,由于其负载电容比较大,源随结构的噪声电子会非常低。

(3)

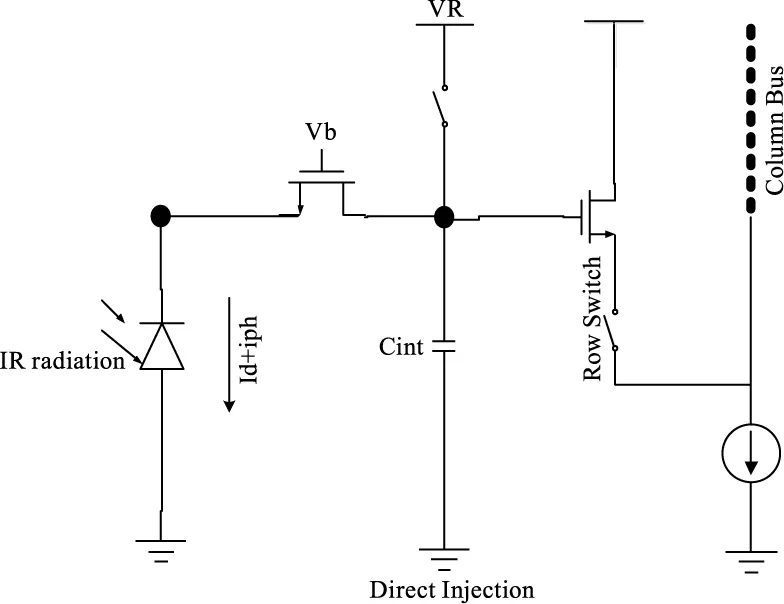

与源随结构相比,直接注入输入级结构主要特点是其积分电容可以独立设计,因此其具有独立的电容电压转换因子。对同样的读出电路链路噪声,直接注入结构可以提供更好的噪声性能,其主要缺点是电流注入效率取决于由光电流决定的MOS管的跨导,参见公式(4)~(6),输入电流超低的情况下,采用直接输入级结构要求非常高的动态阻抗,但同时会导致比较低的截止频率,从而给积分时间设定了下限。动态阻抗在1014Ω,至少需要1 fA的电流才能取得比较好的注入效率。

(4)

(5)

(6)

图3 直接注入输入级原理Fig.3 Direct Injection input stage schematic

与DI注入结构相似,CTIA输入级结构同样可以调节电荷电压转换因子,提供精确的低阻光电二极管的偏置,但不会存在注入效率的问题。CTIA输入级结构受面积约束比较强,因此放大器的低频噪声是噪声的主要贡献者;采用CDS相关双采样技术可以消除大量的复位噪声,达到降噪目的,但积分时间会决定最终的噪声水平,因为积分时间会改变CDS滤波器的谱响应。积分节点之后的读出链路(像素级的源随放大器、输出缓冲器)会产生一个恒定的电压噪声,其值主要取决于链路带宽和功耗限制。当CTIA反馈电容足够小,高转换增益产生高的信噪比会弥补像素运放产生的额外噪声。其噪声传输函数参见公式(7)[3]。

(8)

图4 CTIA输入级原理Fig.4 CTIA input stage schematic

图5为采用CDS相关双采样后,CTIA噪声与积分电容、积分时间、读出电路链路噪声仿真图。当帧频很低时,读出电路链路带宽很小,噪声水平比较低,通常在100 μV以下;但是,由于积分时间很长,经过CDS以后,运算放大器的闪烁噪声仍然比较明显,CTIA噪声水平比较高。另外,参考电压和电源电压的低频噪声会进一步抬高CTIA的噪声的水平[3]。

图5 CDS后的CTIA噪声、积分电容、积分时间关系Fig.5 The relationship of CTIA noise,integration capacitor,integration time

4 读出电路低噪声设计技术

当红外探测器组件应用环境为低背景、弱目标时,由于CTIA输入级结构注入效率很高,通常会被采用,CTIA结构的KTC噪声对成像质量影响较大,其主要与CTIA的反馈电容和输入电容相关,当CTIA输入级结构增益比较高时,复位输入参考噪声可以达到几百个电子,消除KTC噪声对低噪声成像应用至关重要,消除KTC噪声的主要方法是采用相关双采样。相关双采样一方面可以通过列级后续相关双采样实现,图6(a)为滚动模式下的CDS电路结构,在滚动积分模式下,Cint是信号电荷积分电容,Cs是像素内复位信号采样电容。读出阶段分为两部分,首先对存储在Cs上的复位信号进行采样,然后时钟信号psc变为高电平,对积分信号进行采用读出,时序见图6(b)所示。两次采样差值就是消除复位低频噪声后的信号。

列级后续相关双采样主要局限:由于要进行连续的两次操作,读出电路的带宽翻倍,影响整个系统的功耗;另外晶体管漏电在两帧读出方式相关双采样模式下会通过噪声引起误差。

图6 滚动积分相关双采样时序Fig.6 CDS timuy in rolling mocle integration

另外一种相关双采样模式为像素级相关双采样[4],如图7所示。其原理主要是将积分节点通过交流耦合至干净的参考电压V_CLAMP,像素里的交流耦合抑制了复位的不确定性。由于复位开关执行复位时,会引起运算放大器干扰;为了减小干扰,在积分电压允许交流耦合到相关双采样左侧之前,利用系统容许足够时间让复位干扰瞬态建立,采样钳位开关Clamp断开时间要比CTIA复位开关RST断开时间延迟10 ~100 ns。一旦采样的钳位开关断开,复位电平就存储在相关双采样电容上,然后,采样电容的左侧开始跟随积分电荷,最终形成纯的像素输出信号。

图7 像素级相关双采样Fig.7 Pixel level CDS

5 大电荷处理能力设计技术

传统的模拟读出电路一般采用积分电容进行红外探测器光电流信号的搜集,最大的电荷处理能力等于总的积分电容与积分电容上最大电压之积,由于受到工艺技术的限制,即:工艺电压与电容密度,通常模拟读出读出电路的的最大电荷处理能力只能达到30Me左右,限制了红外探测器的最小温度分辨率。读出电路像素单元的电荷处理能力决定了焦平面芯片的最大灵敏度。

假设读出电路是理想电路,红外探测器组件的总噪声来自于信号光电流内在的统计波动,即散粒噪声受限探测,最大信噪比为:

(9)

为了突破传统模拟集成电路电荷处理能力的限制,世界许多研究机构开发出了像素级电荷包计数技术以提高读出电路的电荷处理能力。

像素级电荷包计数计数原理框图如图8所示。它是将探测器的光电流信号转换为与之成正比的脉冲信号,对脉冲个数进行计数,通过计数器输出的数字码来反映探测器光电流的大小。像素单元电路主要由探测器、内部积分电容Cint、比较器、复位电路、反馈电路和计数器、移位寄存器等组成[5]。

其工作原理是当光照射到探测器时,产生的光电流给探测器的电容放电,导致了Vint电位的下降,Vint和Vref通过比较器进行比较,Vref由片上的DAC或者由分压电路产生。当Vint电位低于Vref时,比较器输出为高电平,经反馈电路反馈到复位电路,使Vint的电位复位到初始电平。

图8 像素级ADC原理Fig.8 Pixel level ADC schematic

根据电荷守恒定律,采用像素级电荷计数包方式,可以实现最大电荷处理能力如公式(10)。

Qmax=Iph×Tint=2N×Cint×(VR-VREF)

(10)

其中,VR为复位电平;N为计数器的位数。

与传统的模拟读出电路电荷处理能力相比,采用像素级电荷计数包的方式,读出电路的电荷处理能力可以提高10倍,信噪比可以提高2.5倍以上[6]。

6 结 论

通过深入分析与红外探测器组件成像质量密切相关的关键指标动态范围和信噪比的影响因素以及读出电路输入级结构特点,总结了读出电路输入级的选择方法、读出电路的低噪声相关双采样以及大电荷处理能力设计技术。在实际应用中,如果背景、目标信号非常弱小,读出电路噪声占比较大,红外探测器组件工作在非背景限条件下,要重点进行低噪声读出电路设计;如果背景、目标信号比较强,红外探测器组件工作在背景限条件下,要重点进行读出电路大电荷处理能力的设计、降低暗电流以提高组件的动态范围与灵敏度。

参考文献:

[1] LI Jing guo.Noise analysis and study of ROIC for infrared focal plane array[J].Laser & Infrared,2010,40(5):542-545.(in Chinese)

李敬国.红外焦平面读出集成电路噪声分析研究[J].激光与红外,2010,40(5):542-545.(in Chinese)

[2] Bruno FIEQUE,etc.Infrared ROIC for very low flux and very low noiseapplications.Proc.SPIE 8176,Sensors Systems and Next-Generation Satellites XV,October,2011.

[3] F Guellec,etc.Roic development at cea for swir detectors:pixel circuit architecture and trade-offs[J].International Conference on Space Optics,Tenerife,Canary Islands,Spain,October 2014.

[4] S Kleinfelder,Y Chen,K Kwiatkowski.High-speed CMOS image sensor circuits with insitu frame storage[J].Nuclear Science,IEEE Transactions on,2004,51:1648-1656.

[5] Matthew G Brown,Justin Baker,Curtis Colonero,et al.Digital-pixel focal plane array development[J].Proc.SPIE 7608,Quantum Sensing and Nanophotonic Devices VII,2010,760281-1-1:10.

[6] Kenneth I Schultz,Michael W Kelly,etc.Digital-pixel focal plane array technology.[J].Lincoln Laboratory Journal,2014,20(2):36-51.