基于SoC FPGA抓包的电站控制系统时钟同步设计

刘玉升,项文蔚,王 楠,王 巍

(国核自仪系统工程有限公司,上海 200241)

0 引言

电站控制系统[1]是基于工业以太网的分布式控制系统[2],系统庞大、复杂,设备分布化程度高。各设备间要协调工作,就必须有统一的时间基准,即时钟的精确同步。所有现场设备间的精确时钟同步是实现同步数据采集和控制的核心技术之一。基于嵌入式软件控制方式的时间同步方案,如网络时间协议(network timing protocol,NTP),由于其实现机理的限制,同步精度难以满足事件顺序记录(sequence of event,SOE)为1 ms的要求。

IEEE 1588定义了一个能够在测量和控制系统中实现高精度时钟同步的协议。基于IEEE 1588协议,可实现微秒级的同步精度。本文提出了一种基于片上系统现场可编程门阵列[3-5](system-on-chip field-programmable gate array,SoC FPGA)的时间节点硬件实现方式,以IEEE 1588作为时钟同步协议,以嵌入式软件形式实现TCP/IP通信和时钟同步,通过SoC FPGA准确捕获报文时间戳。这种硬件抓包辅助[6]的时钟同步方法实现了主控时钟节点和从I/O设备节点间微秒级的精确定时同步,并提高了电站控制系统的时钟同步精度[7]。

1 时钟同步算法设计和精度分析

1.1 IEEE 1588的时钟同步原理

IEEE 1588的基本功能是使分布式网络内的参考时钟(reference clock,RC)与其他时钟保持同步。它定义了一种精确时钟协议(precision timing protocol,PTP)[8]。在采用多播技术的分布式总线系统中,使用PTP协议对各个节点设备的时钟进行精确同步。PTP协议也适用于对标准以太网的时钟进行精确同步。PTP技术规范中特别定义了一套基于消息的同步协议,通过周期性地发布带有时间戳的信息包,使各个测控节点的时钟得到校正,从而实现整个系统的同步运行。

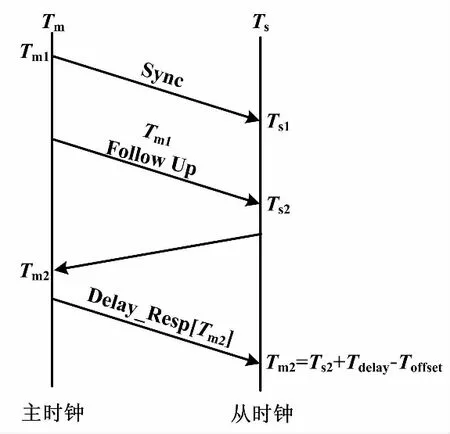

PTP协议使用主从式的结构来组织整个时钟同步系统。主时钟和从时钟是相对的。通常将能提供绝对时间基准,如全球定位系统(global positioning system,GPS)、接收机提供的协调世界时(coordinated universal time,UTC)或相对时间基准(如高精度稳定的时钟信号源)的时钟称为主时钟。系统中的全部从时钟都要同步于同一个主时钟。PTP协议时间同步,通过交换报文来确定主、从时钟间的时间偏移及报文传输的网络延迟。PTP时钟误差校正原理如图1所示。

图1 PTP时钟误差校正原理图

IEEE 1588同步过程分为偏移测量和延迟测量两个阶段。

偏移测量阶段用于修正主、从时钟的时间差。其实现过程如下。

①主时钟Tm采用多播方式,周期性地向网络发出同步时间报文(Sync报文,缺省为0.5 次/s),并在报文发送过程中记录Sync报文的发送时间戳Tm1;从时钟Ts接收Sync报文,并在报文发送过程中记录Sync报文的接收时间戳Ts1。

②主时钟采用多播方式向网络上发送Follow Up报文,其中包含主时钟发布Sync报文的发送时间戳Tm1。

通过时钟使用Follow Up信息中的发送时间戳Tm1和接收时间戳Ts1,可计算出从时钟与主时钟之间的时间偏差Toffset:

Toffset=Ts1-Tm1-Tdelay

(1)

式中:Tdelay为主、从时钟间的网络传输延迟时间,在延迟测量阶段测出。偏移测量阶段提供了一个校正时间,将从时钟校正为:

Tadjust=Ts-Toffset

(2)

延迟测量阶段用来测量上述网络传输造成的延迟时间Tdelay。此阶段实现过程如下。

①从时钟在收到Sync报文后,在Ts2时刻采用单播方式向主时钟发送延迟请求信息包(Delay_Req);主时钟Tm接收Delay_Req报文,并记录下Delay_Req报文的接收时间戳Tm2。

②主时钟收到Delay_Req报文后,在延迟响应信息报文(Delay_Resp)加时间戳,反映准确的接收时间Tm2;然后,采用单播方式,将Delay_Resp报文发送给从时钟。

这样,从时钟就可以非常准确地计算出网络延迟时间Toffset。与偏移测量阶段不同的是,延迟测量阶段的延迟请求信息包是随机发出的,没有时间限制。

假如网络延迟是对称的,则在以上两个阶段,可得到以下方程组:

(3)

解得方程组如下:

(4)

这样可得到从时钟和主时钟之间的时钟偏差值。采用这个差值调整各从时钟节点时钟,直到与主时钟的时间同步为止。

1.2 影响同步精度的因素分析

IEEE 1588协议通过周期性校正来实现主、从时钟同步。同步精度取决于主、从时钟间的偏差值。影响时钟偏差值的主要因素有三个:一是网络通信链路传输延迟的不确定性,二是时间戳的精度,三是主、从时钟同步时间间隔。

①传输延迟。报文在协议栈中的封装和解析过程所用的时间具有非常强的不确定性,造成了网络传输延迟的不确定性。但本文所述的电站控制系统为相对本地化的局域网系统,子网或内部组件所处环境相对稳定。该系统采用交换芯片连接各I/O设备的设计,可确保报文在网络传输中的固定延迟。

②时间戳精度。不同时间戳加盖方式的时间戳精度也不同。在应用层加盖方式中,无论是在网络驱动层,还是在介质无关接口(media independent interface,MII)产生的时间戳都必须返回到PTP应用层并经由内核处理,才能发送到PTP终端。但协议栈的操作延迟和负载都会对同步精度造成影响,因此这种方式的同步精度最低。通过网络驱动程序,在网络驱动层加盖时间戳。由于以太网自身的CSMA/CD机制、上一层通信(如TCP及UDP)的误差检测及翻译障碍等,都占用以太网的时间,因此精度略低。在协议栈物理层加盖时间戳的硬件方式中,由于时间戳的获取点更靠近传输介质,大大降低了网络传输延迟的不确定性,避免了协议栈上部较大的时间抖动,也消除了报文传输中的网络延迟。该方式获取的发送和接收时间戳精度最高。

③同步间隔。同步间隔决定了两条Sync报文的间隔时间。主、从时钟之间通过收发同步消息来获得时间戳,进而计算出同步偏差,并对从时钟时间进行调整。由于主、从时钟的频率不一致,主、从时钟在同步间隔的时间内会产生偏差。当同步间隔变化时,从时钟时间的调整频率也会发生变化,从而对同步精度产生影响。根据IEEE 1588协议,建议将PTP同步间隔时间设为2 s;同时,通过同步间隔时间对从时钟偏差的测试分析[9]可知,主、从时钟同步时间间隔按2 s设计,可保证从时钟时间偏差在微秒级范围内。因此,本系统中主、从时钟同步时间间隔也按2 s设计。

基于上述分析,本设计中的传输延迟和同步间隔均易于实现。为了获得最精确时间戳,实现更精准的时间同步,本设计采用基于SoC FPGA和硬件描述语言(Verilog HDL)的时钟同步系统,通过SoC FPGA抓包辅助技术在协议栈的物理层加盖时间戳。

2 基于SoC FPGA的时钟硬件同步系统设计

2.1 时钟同步系统硬件架构设计

SoC FPGA是近年来的主流嵌入式控制技术。由于其具有低功耗、高性能、低成本、高集成度等特性,因而适用于网络时间节点。为了控制成本、提高时钟同步精度,电站控制系统采用时钟同步设计。实时数据网采用NTP对时,控制网使用基于SoC FPGA抓包辅助实现的高精度PTP对时。时钟同步系统结构如图2所示。

图2 时钟同步系统结构示意图

由图2可知,时钟同步系统包含一个主时钟节点(NTP服务器),若干从时钟节点。其中:主时钟节点上带有GPS接收机或者北斗卫星,NTP服务器发出的秒脉冲信号将主时钟同步于UTC,实时数据网上的所有网络从时钟节点(主控制器时间节点里的NTP客户端)通过以太网的通信链路同步于NTP服务器;通过NTP完成对时后的主控制器时间节点将作为主时钟,控制网上的从I/O设备时钟节点也均使用高精度IEEE 1588协议完成与主控制器的高精度对时,实现了控制器与I/O设备间微秒级的精确定时同步。

2.2 基于SoC FPGA抓包的硬件设计

FPGA实现信号的输入、输出及信息处理,具有纳秒级别的数据处理和运算能力。系统中的主控制器时钟节点和从I/O设备节点均采用SoC FPGA抓包技术,辅助实现高精度IEEE 1588协议。为了充分体现SoC FPGA中的以太网时间戳获取模块对电站控制系统时钟同步精度的关键影响,本设计中的系统时间节点均基于赛灵思的SoC FPGA。SoC FPGA内置ARM内核高性能处理器,本身又具有可编程逻辑单元。SoC FPGA具有高集成、低成本、低功耗、极速中断反应以及高速处理效率等特点。

系统中有关抓包部分的每个时间节点都包含SoC FPGA、以太网介质访问控制(media access control,MAC)器、以太网物理(physical,PHY)层收发器这三个主要模块。本设计采用博通公司的以太网PHY芯片;利用SoC FPGA的可编程逻辑单元实现三个以太网MAC,并通过逻辑编程实现对MII接口上PTP网络报文的获取、硬件时钟计数器等功能。PHY和MAC通过标准的媒体独立接口MII相连,内嵌CPU通过内部级联总线与MAC相连。PHY、MAC和内嵌CPU构成了通信协议栈,完成数据包的发送与接收。SoC FPGA的内嵌CPU主要负责驱动MAC完成相关的通信功能;作为主时钟节点时,内嵌CPU还负责通过MAC向本地网络广播Sync报文。

2.3 基于SoC FPGA抓包的逻辑设计

PTP时钟同步系统逻辑是基于IEEE 1588协议的精准对时原理设计的[10]。

SoC FPGA是实现电站控制系统高精度时钟同步的核心器件。其实现了两个主要逻辑功能:一是控制三个以太网MAC,并使得多网卡具有统一的时钟源;二是在协议栈的物理层获取精准时间戳。基于SoC FPAG的时钟同步方案内部采用结构化的硬件描述语言,设计了MII兼容的以太网发送/接收数据提取模块、硬件时钟计数器FRC、双端口RAM等模块。其中,PTP报文时间戳获取模块通过监听MII接口上的信号,抓取符合条件的PTP报文;时钟计数器FRC值是SoC FPGA基于外部高精度时钟源产生的,发送和接收捕获到的PTP报文,并加盖当前FRC时间戳;SoC FPGA通过监听并分析MAC和PHY之间MII接口的发送和接收信号,确定数据包的发送时间戳和接收时间戳,并将每个网络发送和接收的数据包都存放在各自的RAM中以供CPU读写。由于SoC FPGA内嵌CPU,CPU通过内部高速级联总线实时读取RAM中存放的网络数据包,故内嵌CPU比外置CPU的架构更精简,读取速度更快。

2.4 FPGA实现抓包处理过程

网络数据抓包的程序处理是提取网络时间包的关键,既要保证符合条件的包都被抓取到,又要精确提取想要的时间域。抓包程序需要对抓取网络数据包进行匹配,丢掉无用包。所需抓取时间包的内容包括:固定的16进制UTP特征码(08 00 45 11 01 3F)、FRC值、sourceuuid(发送端MAC)、sourceportid(网络序号)和帧起始精准时间戳。只要带同步时间包的数据包中有符合条件的时间包,FPGA就负责抓取,并将所有的数据都存放在固定的寄存器中;当系统读取时,一次性地以RAM的形式进行传送。每个网络发送和接收的数据包,都存放在各自的RAM中。其中:RAM0可以进行读写,RAM1、RAM2、RAM3和RAM4只能读取相应的网络数据包数据。

根据抓包数据读写操作处理流程,采用Verilog HDL语言开发基于SoC FPGA的以太网发送/接收数据提取模块,采用systemverilog等语言开发以太网发送/接收数据提取模块的测试用例并对其进行充分测试。基于SoC FPGA,采用硬件方法在MII接口处获取时间戳,这是一般CPU无法完成的工作。由于时间戳的获取点更靠近传输介质,网络传输延迟的不确定性大大降低,避免了协议栈上部的较大时间抖动,也消除了报文传输中的网络延迟,获取的发送和接收时间戳的精度最高。根据同步精度的因素影响分析,采用SoC FPGA硬件技术捕获时间戳的方法,对电站控制系统时钟同步精度提升起到了关键的作用,可以避免在软件层获取时间戳精度时受制于操作系统任务调度的影响。

3 系统测试

SoC FPGA抓包对电站控制系统时钟同步精度的辅助实现效果,通过对电站控制系统平台原理样机的测试来显现。将千兆NTP服务器连接到GPS或北斗接收机,主时钟节点CPU每隔2 s向网络发送同步时间报文。

为了充分测试SoC FPGA抓包技术对电站控制系统的时钟同步精度辅助实现情况,从以下三个方面对本设计进行测试。

①SoC FPGA抓包数据测试。

②主控制器时间节点与UTC同步情况测试,从I/O设备时钟节点延迟与偏移情况测试。

③从I/O设备时钟节点间SOE事件时间偏差测试。

3.1 SoC FPGA抓包数据测试

通过对SoC FPGA在MII接口处抓取的网络报文测试,检验主、从时钟节点之间传输的报文是否为IEEE 1588协议规定的报文。将主、从时钟以及测试上位机都通过网线连接在交换机上,即可在上位机上利用Wireshark网络包抓取软件获取主、从时钟之间传输的网络报文。

通过从SoC FPGA抓取到的网络报文,可以清楚地看到发送的各个报文的情况,协议类型为PTP V1版本。通过对所抓取的同步时间报文进行解析,可以得到抓取报文的UTP特征码(08 00 45 11 01 3F)。

3.2 主、从时间节点PTP同步精度测试

主、从时钟以及测试机都通过网线连接在交换机上。上位机可清楚地显示主控制器时间节点通过NTP服务器与UTC时间同步的情况,从I/O设备时钟节点与主节点间的延迟与偏移情况。

通过从主控制器时钟节点输出的时间值和从I/O设备时钟节点延迟与偏移测量值可以看出,主、从时钟节点同步完成后的某一时刻,从时钟节点与主时钟节点的偏移为10.403 μs,实现了主控制器时钟节点和从I/O设备从时钟节点间微秒级的高精度同步对时。

3.3 SOE事件的时间偏差测试

SOE是一种带时间戳的数字量输入(data input,DI)采集模块。在发生SOE事件时,由SOE模块记录SOE时间戳。基于电站控制系统原理样机的时钟同步系统构建一个SOE最小系统:将同一SOE变位事件,同时发送给两对不同控制器管辖下的两个不同SOE模块;通过对两个SOE模块记录的SOE事件时标偏差,可以进一步了解整个电站控制系统的时钟同步精度是否满足电站控制系统需求。SOE最小系统结构如图3所示。

图3 SOE 最小系统结构示意图

首先,组建一个SOE最小系统,将任意两个SOE模块(采样频率为10 kS/s)、两对控制器以及测试上位机都通过网线连接到各自的交换机上,SOE信号发生器分别接入两个SOE模块的任一通道。

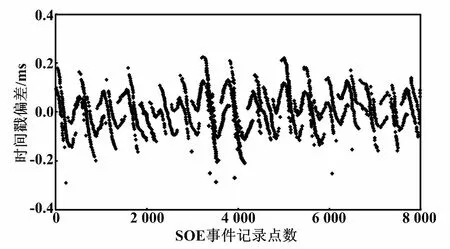

抓取两个SOE模块记录的大量SOE点,通过分析,在测试上位机显示两个从时钟节点间SOE事件的时间戳偏差,如图4所示。

图4 SOE事件时间戳偏差

由图4可以看到,在电站控制系统时钟同步稳定过程中,SOE事件时间戳偏差在±300 μs以内,满足SOE相对时间误差不大于1 ms的要求。由于SOE事件时间戳偏差是由电站控制系统的时间同步精度决定的,因此,SOE时间戳偏差测试结果也间接表明了整个电站控制系统时钟达到了微秒级的时钟同步精度。

基于SoC FPGA抓包辅助技术实现的时钟同步系统,其所达到的时钟同步精度指标完全满足电站控制系统时钟同步精度的要求,并在核电仪控系统工程样机上得以验证。基于本设计的电站控制系统已成功应用于国内某火力发电厂的200 MW机组,计划进一步应用于更大功率的发电机组;验证成熟后,将正式用于核电站控制系统中。

4 结束语

为了满足电站控制系统中多网络节点统一时钟源和精确时钟同步的要求,本文设计并实现了基于SoC FPGA抓包的IEEE 1588对时协议时钟同步。该设计基于SoC FPGA 抓包,获得了精确的时间戳,降低了电站控制系统时钟同步设计的复杂度。硬件采用SoC FPGA实现时钟节点,提高了电站控制系统的集成度。

通过对电站控制系统平台原理样机的长期系统测试和实际应用,该设计所达时钟精度指标完全满足电站控制系统全站时钟节点设备同步时钟精度的要求,从而可广泛应用于核电、火电、燃机等各领域的电站控制系统中,保障电站控制系统的稳定、可靠、安全运行。

参考文献:

[1] 顾军.AP1000核电厂系统与设备[M].北京:原子能出版社,2010:465-475.

[2] 王常力,罗安.分布式控制系统(DCS)设计与应用实例[M].北京:电子工业出版社,2010:51-67.

[3] 廉玉.工业以太网时钟同步的研究与设计[D].天津:天津工业大学,2012:21-50.

[4] 汪祺航,吴在军,赵上林,等.IEEE 1588时钟同步技术在数字化变电站中的应用[J].电力系统保护与控制,2010,38(19):137-141.

[5] 任爱锋,罗丰,宋士权,等.基于FPGA的嵌入式系统设计 [M].西安:西安电子科技大学出版社,2014:179-239.

[6] 杨传顺,袁建,李国华.分布式控制系统精确时钟同步技术[J].自动化仪表,2012,33(4):66-69.

[7] 曹禹,邹磊,时维铎,等.基于IEEE 1588时间同步系统的硬件实现[J].电测与仪表,2013,50(3):107-112.

[8] EIDSON J,KANG L.IEEE standard for a precision clock synchronization protocol for networked measurement and control systems[C]//IEEE,2008.

[9] 覃斌毅,陈铁军,邱杰,等.基于IEEE 1588协议时钟同步精度影响因素的研究[J].计算机测量与控制,2014,22(10):3312-3315.

[10]戚明珠.基于FPGA的IEEE 1588 IP核开发[D]. 济南:山东大学,2012:34-63.