一种基于RapidIO总线的高速图像数据传输设计

李 宾 刘 鑫 杨文良 刘昌杰

北京航天自动控制研究所,北京100854

随着图像处理技术应用越来越广泛,基于FPGA+DSP架构的处理系统以其优越的性能得到越来越多的认同。这类系统结构灵活,FPGA进行并行处理和接口控制,DSP进行复杂算法计算,充分发挥2种处理器的优势,从而提高系统的整体性能。但是,随着图像处理算法复杂度的提高,以及对图像帧频、分辨率和实时性要求越来越高,而传统的FPGA+DSP架构的图像处理系统大多采用并行总线互连方式,所能提供的带宽有限,已成为限制高速图像处理系统发展的关键因素。目前,以串行RapidIO为代表的新一代总线结构很大程度上弥补了传统总线的不足,RapidIO总线是一种高性能、低引脚数的高速串行总线,是为满足高性能嵌入式系统需求而设计的一种开放式互连技术标准,能广泛满足嵌入式系统应用中处理器、处理平台和IO设备间的互连需求[1]。

本文设计了一种基于RapidIO总线的图像处理系统,成像装置输出的实时图通过Camera Link接口进入该系统,FPGA按协议对实时图数据进行解码、缓存,再通过RapidIO总线将图像高速、实时地传输到DSP处理器中。由于Camera Link接口速率与RapidIO总线速率不同,本文设计了一种FIFO缓存结构,解决了2种接口间的速率匹配问题。

1 系统概述

本文设计的高速图像处理系统采用FPGA+DSP架构,FPGA与DSP间通过串行RapidIO总线互连,FPGA选用Xilinx公司的Kintex-7系列XC7K325T,DSP选用TI公司的多核系列处理器TMS320C6678[2]。在该系统中,FPGA主要用于系统的控制和图像采集、传输,DSP主要负责算法实现。图像由高帧频、高分辨率的CCD成像装置采集,经由Camera Link接口传输至图像处理系统,在系统内,图像经过Camera Link接收芯片的串并转换后发送给FPGA,FPGA对其进行预处理后再将数据发送到DSP,进行复杂的算法计算。图像数据传输框图如图1所示。

图1 图像数据传输框图

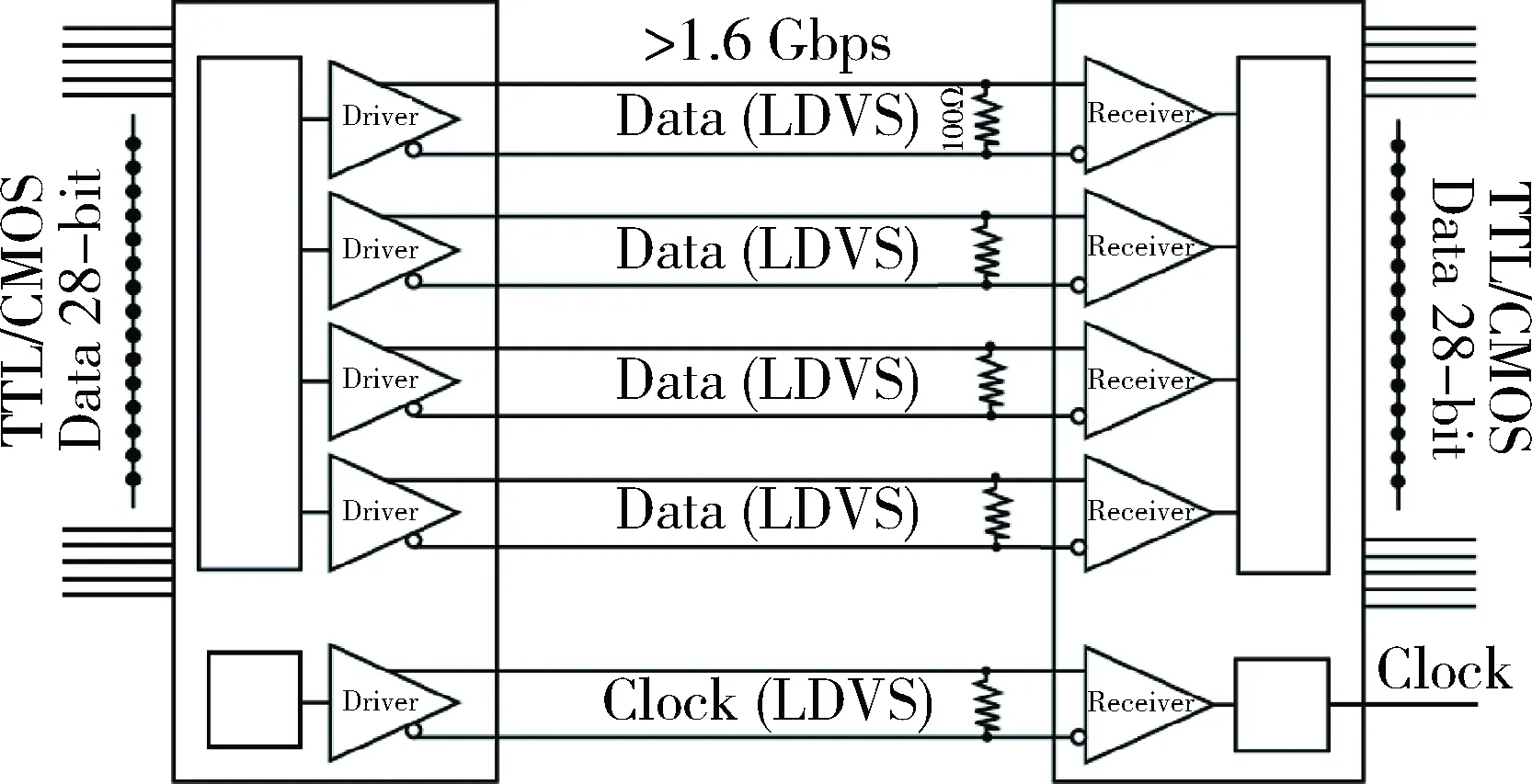

2 Camera Link协议

目前,Camera Link协议是一种应用比较广泛的数字图像传输协议[3],它由ATA制定、修改及发布,用于解决数字图像在成像装置和接收设备间的高速传输。Camera Link是一种高速串行的传输标准,将28位并行数据信号和1位时钟信号转换为5对LVDS信号在链路上传输,从而降低了传输信号的数量,提高了传输可靠性。

图2 Camera Link发送接收原理图

Camera Link信号分为4类:视频信号、相机控制信号、异步串行通信信号和电源信号。

表1 Camera Link接口信号

Camera Link将24位图像数据分成3组,每组8位信号成为一个端口。Camera Link标准定义了8个端口(A~H)。Camera Link接口有3种配置模式:Base,Medium和Full[4]。3种模式所使用的连接器和转换芯片数量各不相同,具体配置方式见表2。

本文使用的成像装置配置为Medium模式,每帧图像为2528×2000像素,每个像素点为8位数据,帧频为50Hz。图像处理系统从成像装置接收数字视频图像数据,帧频为50Hz,内容为2528×2000的8位图像信息。成像装置的Camera Link接口工作在Medium模式下,使用A,B,C和D共4个端口,每个时钟传输4个字节数据,时钟频率为66MHz,因此图像数据速率达到2.112Gbps,并行总线难以满足需求,所以本文使用串行RapidIO总线实现FPGA到DSP的高速实时数据传输。

表2 Camera Link端口配置方式

3 串行RapidIO总线

RapidIO总线是迄今为止唯一的开放式高速串行互连总线标准,也是唯一的嵌入式互连正式国际标准,它针对高性能嵌入式系统芯片间和板间互连而设计。2001 年初,RapidIO 1.1 版发布,很多半导体厂商开始支持RapidIO 接口,推出了包含RapidIO接口的处理器,FPGA厂商也提供了RapidIO软核或者硬核。

串行RapidIO是一种高性能的开放式互连总线标准,具有效率高、稳定性好、速度快、成本低和引脚少等优势,为嵌入式系统提供了一种可行的高带宽、低延迟且高可靠性的数据传输解决方案[5]。RapidIO是在物理层采用差分信号进行传输的总线标准,RapidIO 1.x标准支持的信号速率为1.25 GHz,2.5 GHz和3.125 GHz,RapidIO 2.x 标准在兼容RapidIO 1.x 标准基础上,增加了支持5 GHz、6.25 GHz的传输速率[6]。

本文设计的图像处理系统选用的Kintex-7系列FPGA,集成了高速串行收发模块GTX transceiver,可用作串行RapidIO等高速串行协议的物理层实现。选用的DSP具有串行RapidIO硬件接口[7],支持RapidIO 2.1标准,支持的信号速率为1.25 GHz,2.5 GHz,3.125GHz和5GHz,支持1×,2×和4×多种工作模式。Xilinx公司为串行RapidIO接口提供了IP核[8],本文在IP核的基础上实现了RapidIO的数据传输等功能。

历史上,山东男篮的东家如走马灯一样不断更换。从体育局到金斯顿再到黄金男篮,之又有高速男篮和西王男篮。每一轮更换东家,必然会让球队经历模式、思路的转型,换血、换帅、不系统的训练,这些问题,似乎始终与山东男篮有缘。

图3 串行RapidIO IP核原理框图

Xilinx RapidIO IP核由逻辑层、缓冲层、物理层、封装层和参考设计构成[9],其中逻辑层、缓冲层和物理层是软核,封装层是硬核,IP核的大部分信号对用户是不可见的,直接与用户相关的是逻辑层上的用户接口[10]。对用户接口进行合理配置和控制,RapidIO接口可实现数据发送和接收等功能。本文在图像传输的功能需求下,进行了相关设计,以下详细介绍设计方法。

RapidIO的IP核可以由Xilinx的开发工具ISE软件生成,在生成时需要注意以下配置项:用户接口I/O格式。Xilinx的RapidIO IP核支持2种类型的I/O格式,分别为Condensed I/O格式及Initiator/Target格式。Condensed I/O只有一条单独的发送和接收通道,而Initiator/Target则根据操作对象是本地还是远端分为2条通道。分析可知,采用Initiator/Target格式允许将本地发起的事务和远端发起的事务分开进行用户接口设计,因此可以简化设计工作,本设计选用Initiator/Target格式。

图4 Condensed I/O格式和Initiator/Target格式

RapidIO IP核用户接口使用AXI4-Stream总线协议,AXI4-Stream采用tready,tvalid和tlast握手机制来实现数据包的传输,发送端和接收端在进行通信时,需要先收到接收端发送的tready信号进行握手,然后将数据tdata和tvalid信号发送给接收端,tvalid信号为高时指示数据tdata有效,一个数据包发送完成时最后一个时钟周期发送tlast信号。AXI4-Stream信号时序如图5所示。

图5 AXI4-Stream信号时序图

4 基于FIFO缓存的RapidIO接口设计

图像处理系统中,FPGA将Camera Link接口接收到的图像通过RapidIO总线发送到DSP内存中。本系统成像装置Camera Link接口的时钟频率为66MHz,数据宽度为32位,FPGA与DSP间的RapidIO接口配置为2×3.125Gbps模式,此时FPGA RapidIO IP核用户接口的时钟频率为78.13MHz,数据宽度为64位。Camera Link接口和RapidIO接口数据速率不匹配,而且数据格式也不同,Camera Link接口的数据和控制信号并不能直接用在RapidIO IP核的用户接口上。

在传统并行总线图像处理系统中,通常会在Camera Link接收芯片后增加FIFO芯片,对图像数据进行缓存,然后通过FPGA、并行总线传输到DSP,如图6所示。FIFO芯片通常数据位宽为8位、16位或32位,Camera Link接口数据宽度为32位,RapidIO IP核数据宽度为64位,进行数据输出时,要进行2个时钟周期的读操作,才能得到1个64位数据。若采用2片FIFO并联设计,输入端也需要将2个32位数据拼成1个64位数据,应用较为不便。

图6 传统并行总线图像数据传输框图

为解决该问题,本文设计了一种FPGA内部FIFO缓存,降低了硬件设计复杂度。Camera Link接口进来的数据先存入FPGA内部设计的FIFO,然后再按需要从FIFO中读出,并按照AXI4-Stream接口的时序,将数据通过RapidIO总线发送到DSP的内存中。FPGA内部FIFO可以设计成输入宽度为32位,输出宽度为64位,输入输出时钟不同,更符合本系统的应用需求。

FPGA中包含Block RAM资源,可以很方便地实现不同宽度和深度的FIFO。同样,FIFO也可以由Xilinx的开发工具ISE软件生成。FIFO主要包括4部分,分别为物理存储单元、写控制接口、读控制接口和状态检测接口。在配置存储单元时,由于读写接口采用的时钟频率和数据宽度均不同,所以设计成读时钟rd_clk和写时钟wr_clk独立的模式,读接口数据宽度为64位,写接口数据宽度为32位。为了得到FIFO的存储状态,需要配置FIFO输出空满状态标志。为了精确获得FIFO存储的数据量,配置FIFO输出写入的数据长度和可读出的数据长度。

图7 基于RapidIO总线的图像数据传输原理图

包的长度设计为16。由于AXI4-Stream数据总线的宽度是64位,所以一包数据的长度是16×64/8=128字节。AXI4-Stream译码模块设计时,需要按照图5的时序对数据进行打包处理,由于时序较为复杂,所以在设计时使用了状态机,如图8所示。

图8 AXI4-Stream接口状态机设计图

系统开始工作时,状态机进入空闲状态(REQ_IDLE);当检测到链路和端口初始化完成后,进入等待状态(REQ_WAIT);当检测到ireq_tready信号为高电平且FIFO内的数据大于等于128字节时,进入帧头发送状态(REQ_HDR),帧头包含的信息有数据包类型、源地址、目的地址和包长度等;当检测到ireq_tready信号为高电平时,进入写状态(REQ_WRITE),直到完成16次写操作后,状态机回到空闲状态(REQ_IDLE)。

图9是串行RapidIO IP核在发送图像数据时使用ISE软件监测到的关键信号波形图,各信号的时序与AXI4-Stream接口要求的时序相符。经验证,DSP端可以收到FPGA传输过来的图像数据,数据无误。RapidIO总线配置为2×3.125Gbps模式时,实际测得传输速率可达3.91Gbps,而Camera Link输入的数据速率为66MHz×32bits =2.112Gbps,可以满足应用需求。

图9 实测RapidIO接口数据发送波形图

RapidIO总线传输采用8b/10b编码,理论速率为2×3.125×8/10 =5Gbps。由于在设计中采用了FIFO缓存,当FIFO中缓存的数据超过一包时才会启动一次RapidIO传输,在FIFO缓存数据时RapidIO总线处于空闲状态。当进行数据传输时,RapidIO总线理论速率为5Gbps。在本系统中,RapidIO总线的实际传输速率只有理论速率的78.2%,有以下几个原因:

1)RapidIO数据传输时,按协议需要传输大量的控制字,用于链路维护、包确认、错误报告和错误恢复等;

2)误码重传机制。当RapidIO链路检测到发送误码,链路维护协议可确保发生误码的数据包得到重传;

3)接收方DSP处理数据的时间。DSP收到RapidIO总线的数据后,DSP内部数据总线需要把数据转移到内存中,占用一定的时间;

4)测试方法中存在计数计时的测量误差。

5 结论

介绍了一种基于RapidIO总线的高速图像处理系统中的数据传输设计方案。首先介绍了成像装置Camera Link协议和FPGA软件设计时使用的RapidIO IP核。在设计时,采用了基于FIFO缓存的RapidIO接口设计方法,解决了Camera Link接口和RapidIO接口间的速率匹配问题,实现了FPGA与DSP间基于RapidIO总线的高速图像实时传输。实验验证,当RapidIO总线配置为2×3.125Gbps模式时,实际的图像传输速率可达3.91Gbps,可以满足系统的应用需求。

[1] RapidIO Trade Association. RapidIO Interconnect Specification,Part 1:Input/Output Logic Specification,Rev.1.3[S]. RapidIO Trade Association,2005.

[2] TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor Data Manual, SPRS691C[S]. TI, 2012,2.

[3] Donald G Bailey . 原魁,等.译. 基于FPGA的嵌入式图像处理系统设计[M]. 北京:电子工业出版社. 2013. (Donald G Bailey. Design for Embedded Image Processing on FPGAs[M]. Beijing:Publishing House of Electronics Industry,2013.)

[4] 宁赛男.RapidIO协议在图像处理系统中的应用研究[D].长春:中国科学院长春光学精密机械与物理研究所,2013. (Ning Sainan. The Research on Application of RapidIO Protocol in Image Processing System[D]. Changchun: Changchun Institute of Optics, Fine Mechanics Physics, Chinese Academy of Sciences,2013.)

[5] RapidIO Interconnect Specification,Part 2:Message Passing Logical Specification,Rev.1.3[S]. RapidIO Trade Association,2005.

[6] RapidIO Interconnect Specification,Part 3:Common Transport Specification,Rev.1.3[S]. RapidIO Trade Association,2005.

[7] Keystone Architecture Serial RapidIO(SRIO) User Guide[S]. TI, 2012,11.

[8] Serial RapidIO Gen2 Endpoint v4.0 LogiCORE IP Product Guide[S]. Xilinx,2015.

[9] 蔡叶芳,田泽,李攀,何嘉文. 一种RapidIO IP核的设计与验证[J]. 计算机技术与发展, 2014,24(10):98-100.(Cai Yefen, Tian Ze, Li Qian,He Jiawen. Design and Implementation of a RapidIO IP Core[J]. Computer Technology and Development, 2014,24(10):98-100.)

[10] 何嘉文. 串行RapidIO协议的实现与验证[D]. 西安:西安电子科技大学,2011.(He Jiawen. The Realization and Verification of Serial RapidIO Interconnect Specification[D]. Xi’an: Xidian University, 2011.)