基于ADF4350的锁相环频率合成器设计与实现*

夏江林,邹传云

0 引 言

频率合成技术是经过一系列处理后具有高稳定性和高准确度的标准参考频率产生大量具有相同稳定性和准确性的离散信号,并且输出信号的频率可由数字信号控制[1]。锁相环(PLL)是频率合成器的核心组成部分,是许多电子产品的关键部件之一,可广泛应用于工业、国防、军事和民用等领域。锁相环频率合成器由PD(相位比较器)、LF(环路滤波器)和VCO(压控振荡器)组成[2],原理如图1所示。

图1 锁相环频率合成器的原理

图1 中,fR为输入信号的频率,f0为输出信号的频率。PD用于比较两个输入信号fR和经N分频的输出信号f0。如果两个输入信号的频率不一致,PD将产生一个低频分量,使得VCO的输出频率通过LF变化[3]。LF的作用是产生误差控制电压来控制VCO的输出频率。由于负反馈的影响,这种变化会不断使输出信号f0经N分频后的频率和输入信号的频率fR一致。f0和fR的相位差保持在一个不变的范围内。此时,PLL环路处于所谓的“锁定”状态[4]。最后,使输出信号频率为f0=N·fR。

本文设计了一种用单片机作为锁相环芯片ADF4350的控制器,实现了输出1 GHz的锁相环频率合成器。因为锁相环芯片ADF4350集成了鉴相器、压控振荡器和N分频器,所以本文的主要工作在于设计环路滤波器参数和调试ADF4350内部R0-R5寄存器的控制数值。锁相环(PLL)频率合成器。它的工作电压一般选3.3 V,最大鉴相频率为32 MHz,RF输出功率为4~5 dBm。

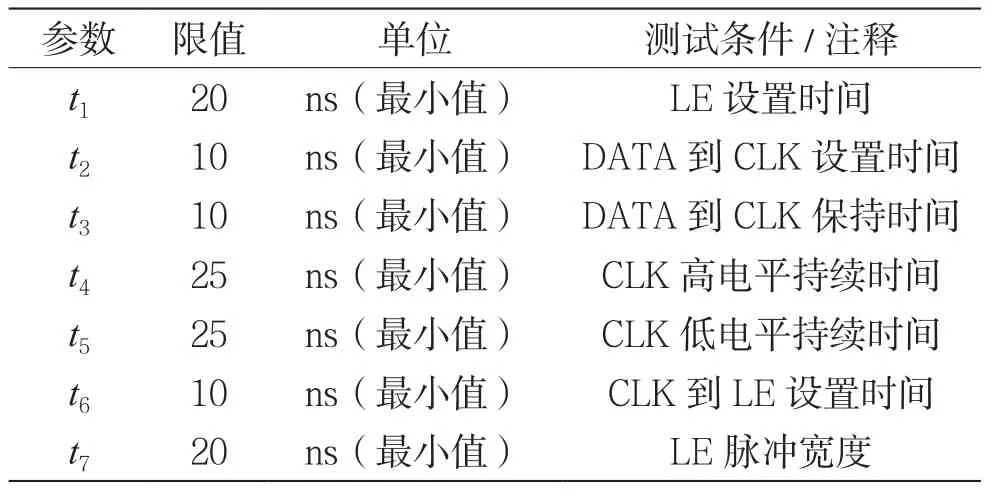

ADF4350的数字接口是与SPI兼容的串行接口,作用在于将数据写入器件。CLK、DATA和LE则控制数据传输。在CLK从低电平到高电平时,将32位数据逐位写入对应寄存器;当LE由低电平变为高电平时,数据被传输至对应的锁存器[5]。ADF4350的时序特性如表1所示,时序图如图2所示。

1 锁相环芯片ADF4350简介

ADF4350是一款由ADI公司生产的集成低噪声VCO的PLL,可以连续调谐137.5 MHz至4 400 MHz。ADF4350结合外部环路滤波器和外部基准频率使用时,可以实现小数N分频或整数N分频

表1 时序特性

图2 时序图

2 锁相频率合成器在ADIsimPLL中的仿真设计

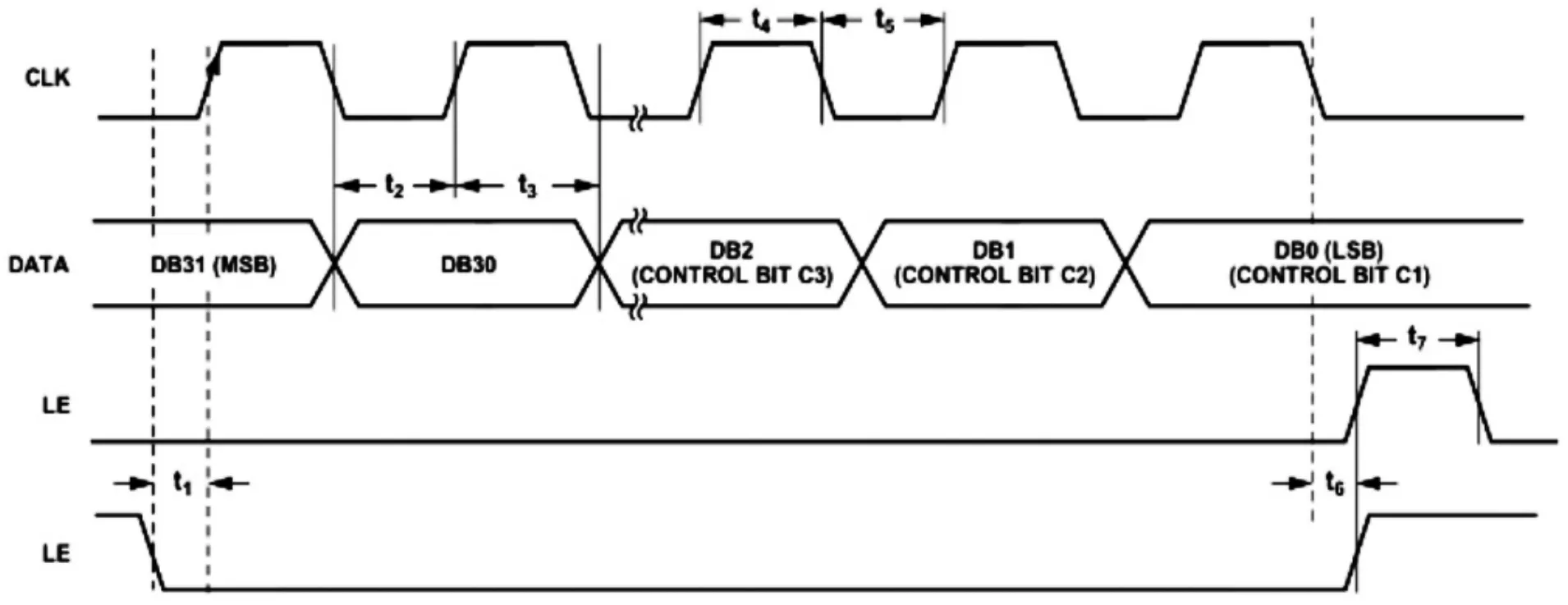

ADISimPLL用于辅助设计ADF4350外部电路,如图3所示。ADISimPLL是ADI公司为其产品提供的PLL辅助设计软件,适用于一切ADFxxx系列的锁相环产品。在已知参考输入频率、输出频率、环路带宽和相位裕度时,可以通过ADISimPLL轻松设计环路滤波器的各项参数。然后,根据实际情况选择相对应的电阻和电容值,就可以实现对环路滤波器的设计。ADISimPLL同样可以对锁相频率合成器系统各部分的相位噪声进行分析[6]。

环路滤波器的设计是PLL频率合成器设计中最重要的一个环节。合理的设计参数直接关系到频率合成器输出信号的杂散、相位噪声、频率稳定度、频率转换时间等诸多指标[4]。它的作用是滤除鉴相器产生的高频信号。相对于有源滤波器,无源滤波器只使用RC低通滤波器,成本低,不像有源滤波器带来噪声和零点漂移。所以,本文采用三阶无源低通滤波器作为PLL的环路滤波器。该滤波器电路结构简单,噪声低,稳定性高。图3中,环路滤波器参数为:C1=8.2 pF,R1=7.5 kΩ,C2=120 pF,R2=15 kΩ,C3=3.9 pF。

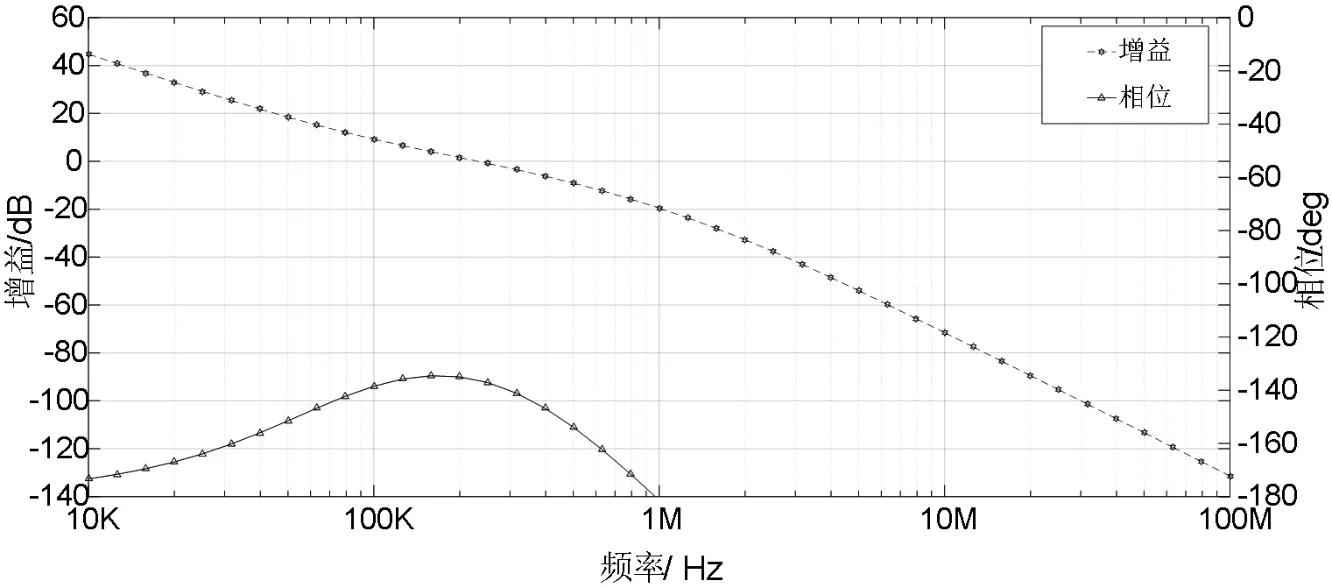

为了实现锁相环的快速锁定,本文将环路带宽设计为200 kHz。通过ADIsimPLL对设计的环路特性进行仿真,环路带宽设置为200 kHz,输出频率为1.0 GHz,系统的开环增益特性如图4所示。

图3 ADF4350的外围电路

图4 系统的开环特性曲线

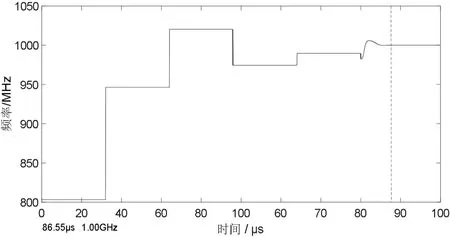

图4 给出了系统开环传递函数的增益和相位曲线。在200 kHz处,对数增益为零,相位裕量在45°左右。当相位偏移为180°时,增益幅度约为-30 dB。可见,当对数增益为零时,相位裕度为正;当相位偏移为180°时,增益幅度为负,符合波特标准稳定条件,所以环路可以稳定[7]。同样,可以通过ADIsimPLL获得系统的输出频率特性,如图5所示。在图5中可以得到,系统输出稳定即锁定的时间为86.55 μs,满足系统的设计要求,锁定时间小于100 μs。

图5 系统输出频率随时间的变化

通过ADISimPLL同样可获得系统输出1 GHz时的相位噪声,如图6所示。在图6中可以清楚看到系统各部分对整个系统相位噪声的贡献。其中,Chip(芯片)和VCO是ADF4350芯片固有的特性,器件选择后不能改变;Loop Filter(环路滤波器)和Ref(参考频率)则可以通过设计和选择来减少对系统相位噪声的影响。从图6可以看出,在1 MHz时,系统的相位噪声约为-128.275 3 dBc/Hz@1 MHz。这个值为理论值,实际应用中由于存在电磁干扰,相位噪声会高于理论值[8]。

图6 1 GHz相位噪声仿真结果

3 锁相频率合成器系统实现

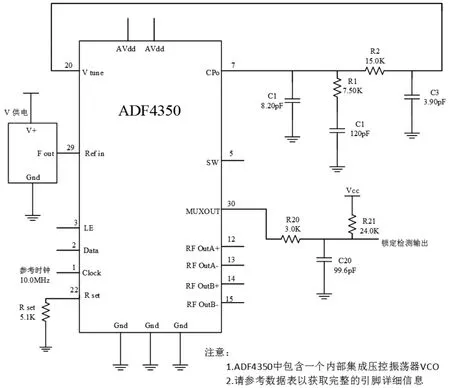

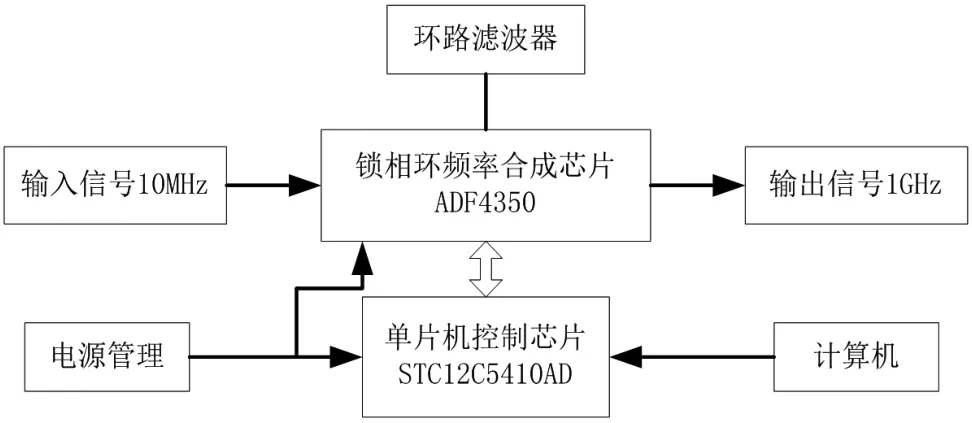

本系统的整体设计,如图7所示。单片机芯片STC12C5410AD实现对整个系统的控制。单片机芯片通过计算机写入相应的控制程序,从而控制锁相环频率合成芯片ADF4350对应的寄存器,完成对输出频率的控制。

图7 锁相环频率合成器的整体设计

3.1 频率合成器硬件电路实现

频率合成器原理图的核心部分,如图8所示。原理图中包含环路滤波电路、电源输入电路和信号输入输出电路,并运用了大量去耦电容和旁路电容提高电路的抗干扰能力。锁相环频率合成芯片ADF4350中,CLK、DATA和LE控制数据的传输,分别与单片机控制芯片STC12C5410AD的P1^7~P1^5引脚相连。

如图7所示,输入信号10 MHz由外部的晶振或信号源提供,要求高稳定度和低杂散,为整个系统提供准确的参考频率。单片机STC12C5410AD的作用是通过对ADF4350内部寄存器Register0~5的控制,实现对整个频率合成器系统输入和输出的控制。另外,电源管理给锁相环芯片ADF4350提供了3.3 V稳定的直流电压,给单片机芯片STC12C5410AD提供了5.0 V稳定的直流电压。环路滤波器的作用是滤除鉴相器产生的高频信号,给后级输入的电压控制振荡器(VCO)提供稳定的控制电压。整个系统最后实现了输出1 GHz的稳定信号。

图8 频率合成器原理

3.2 频率合成器参数实现

对于整个频率合成器系统而言,系统参数设计主要是确定ADF4350中各寄存器Register0~5的值。寄存器Register0~5中包含了锁相环的主要参数,如参考输入频率、输出频率、鉴相器频率、前置预分频器、反馈分频系数、环路滤波器的环路带宽等。本文设计的锁相环频率合成器的输出频率为1 GHz,相位噪声优于-100 dBc/Hz@100 kHz,杂散抑制优于-60 dBc,锁定时间小于100 μs。可以用式(1)分析锁相环频率合成器系统的总体随机相位噪声[6]:

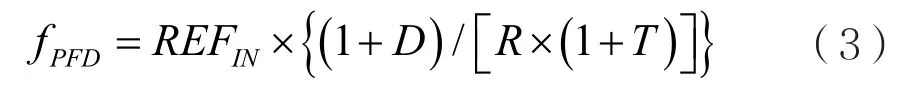

其中PNTOTAL为整个系统的相位噪声,其值是一个负数;PNSYNTH是锁相频率合成器自身的归一化带内相位本底噪声,典型值为-213 dBc/Hz;201g N是一个与分频器N有关的相位噪声增量,其中反馈分频系数N可以在ADF4350的寄存器Register0中进行设置;101g fPFD是一个与鉴相器的鉴相频率有关的相位噪声增量,鉴相频率可以在寄存器Register1中设置。由式(1)可知,锁相环频率合成器的相位噪声主要由PNSYNTH、分频器N和鉴相器频率fPFD决定。而PNSYNTH是由芯片本身决定的一个固定值,可以当作常量处理[9]。所以,可以通过选择较大的分频器N和鉴相器频率fPFD来降低整个系统的相位噪声。本文最终确定采用鉴相频率为10 MHz和分频器N为400。同样,可以根据式(2)、式(3)和式(4)来确定ADF4350中的其他参数。

其中RFOUT是频率合成器的输出频率,INT是整数分频系数,FRAC是小数分频系数,MOD是模数值,fPFD是频率合成器的鉴相频率,DVCO是频率合成器VCO输出频率的分频器值,可取1、2、4、8、16。

其中REFIN是锁相频率合成器的基准输入频率,D是REFIN倍频器位(0或1),T是REFIN基准2分频位(0或1),R是RF基准分分频系数。

其中fRES是锁相中VCO的输出通道分辨率。

根据锁相环系统的设计要求,最终确定各参数 为:INT=400、FARC=0、fPFD=10 MHz、DVCO=4、REFIN=10 MHz、D=0、T=0、R=1、fRES=800 kHz、MOD=12。根据上述参数值,结合ADF4350的datasheet资料,可决定R0~R5寄存器的值为:R0(0x00C80000)、R1(0x08008061)、R2(0x00004EC2)、R3(0x000004B3)、R4(0x00A6603C)、R5(0x00580005)。

3.3 频率合成器控制程序实现

单片机STC12C5410AD芯片主要用来控制锁相环频率合成芯片ADF4350的内部寄存器配置和输入输出设置。ADF4350数字部分包括10位RF R计数器、16位RF N计数器、12位FRAC计数器和12位模数计数器。在时钟CLK的上升沿时,数据输入32位移位寄存器中,再在LE上升沿时从移位寄存器传输到6个锁存器之一。其中,R0配置16位INT值和12位FRAC值,R1配置12位相位值和12位MOD值,R2配置10位R值和MUXOUT输出参数,R3配置12位时钟分频器和其他参数,R4配置射频输出功率等参数,R5是锁定检测。ADF4350的寄存器序列的初始化顺序为从R5到R0。根据ADF4350的时序特性,如表1、图2所示,可以编写出单片机STC12C5410AD的控制程序。由于篇幅有限,本文仅给出了控制寄存器R5的程序[10]。

4 锁相频率合成器性能测试

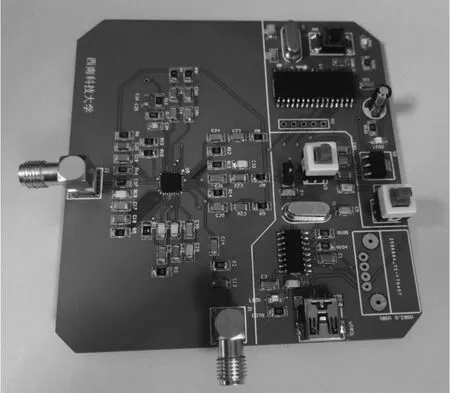

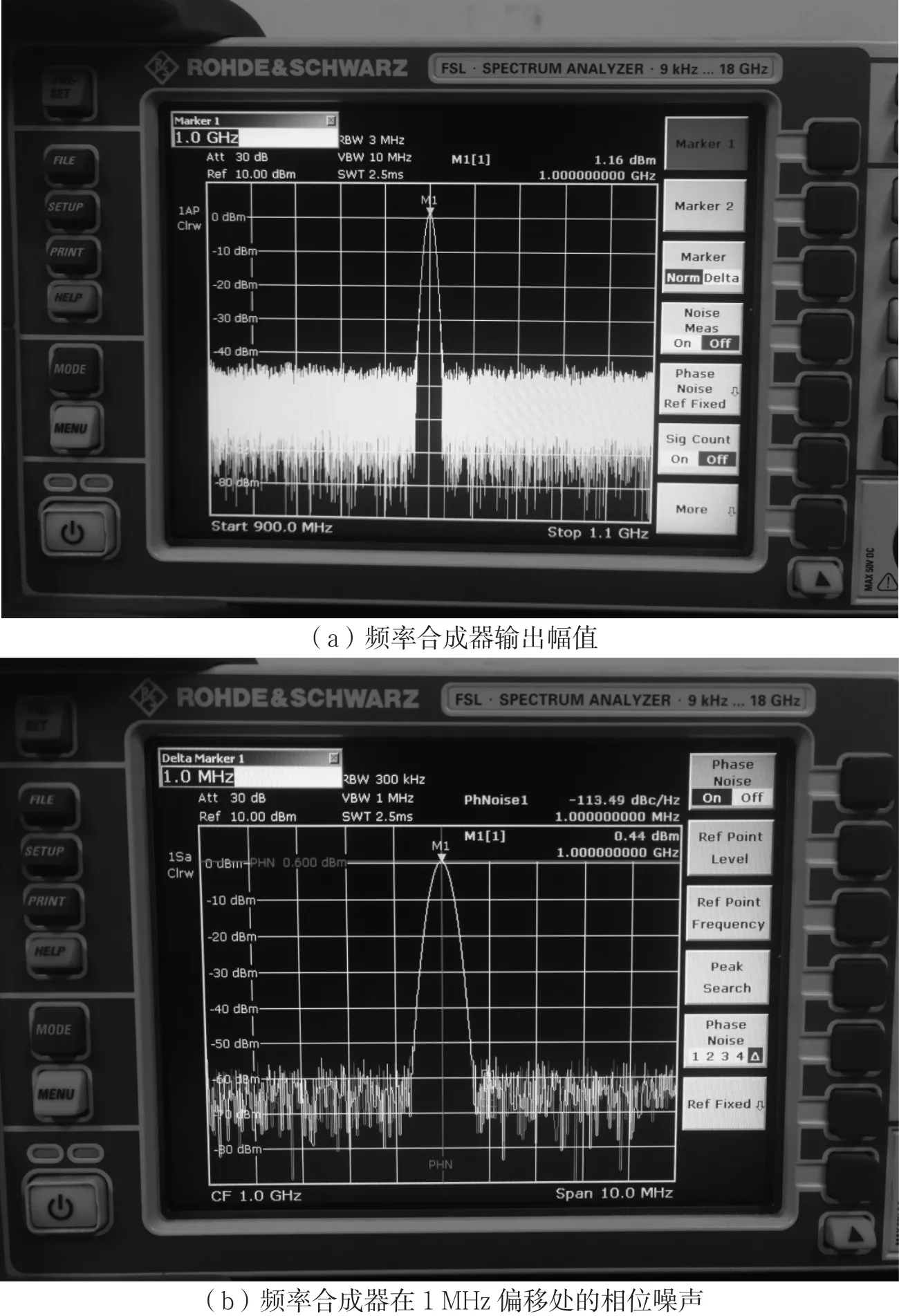

采用以上硬件电路设计,研制出输出1 GHz的锁相频率合成器,实物照片如图9所示。通过对单片机STC12C5410AD的合理编程,实现锁相频率合成器输出1 GHz的稳定信号,并通过频谱仪对频率合成器的性能进行测试,结果如图10所示。

图9 频率合成器的实物照片

在图10(a)的测试中,频率合成器稳定输出1 GHz的信号,且输出幅值达到1.16 dBm。测试相位噪声时,将频谱仪的RBW设为300 kHz,SPAN设为10 MHz,测得在1 MHz处的相位噪声为-113.49 dBc/Hz,其图像如图10(b)所示。

5 结 语

本文介绍了运用ADF4350锁相环芯片和单片机STC12C5410AD设计1 GHz频率合成器的设计过程和设计方法,最终设计完成了大小为45 mm×45 mm、输出幅度为1.16 dBm、相位噪声为-113.49 dBc/Hz@1 MHz的高稳定度频率合成器。实验证明,该频率合成器能很好地运用于本地振荡器。

图10 频率合成器测试结果

[1] 万天才.频率合成器技术发展动态[J].微电子学,2004,34(04):366-370.WAN Tian-cai.Development of Frequency Synthesizer Technology[J].Microelectronics,2004,34(04):366-370.

[2] 李党锋.锁相环频率合成器的发展及应用[J].现代导航,2010(06):37-41.LI Dang-feng.Development and Application of the PLL Frequency Synthesizer[J].Modern Navigation,2010(06):37-41.

[3] 于为健,张娟.基于ADF4350的S频段锁相频率合成器设计[J].电子科技,2013,26(11):69.YU Wei-jian,ZHANG Juan.Design and Implementation of S-band PLL Frequency Synthesizer Based on ADF4350[J].Electronics Technology,2013,26(11):69.

[4] 金玉琳,佘世刚,周毅等.锁相环环路滤波器噪声特性分析与仿真[J].现代电子技术,2011,34(21):193-195.JIN Yu-lin,SHE Shi-gang,ZHOU Yi.Noise Analysis and Simulation of of PLL Loop Filter[J].Modern Electronics Technique,2011,34(21):193-195.

[5] Wideband Synthesizer with Integrated VCO ADF4350 Datasheet[Z].Analog Deices,2008.

[6] 徐述武,汪海勇,唐云峰.基于ADF4350锁相频率合成器的频率源设计与实现[J].电子器件,2010,33(06):725-729.XU Shu-wu,WANG Hai-yong,TANG Yun-feng.Design and Realization of Frequency Source Based on ADF4350 PLL Frequency Synthesizer[J].Electronic Devices,2010,33(06):725-729.

[7] Song Q,Qi J.ADF4350-based Frequency Modulation transmitter design[C].International Conference on Cyberspace Technology IET,2015:1-3.

[8] 黄建钢.锁相环频率合成器相位噪声分析[J].雷达与对抗,1994(03):57-63.HUANG Jian-gang.Phase Noise Analysis of Phaselocked Loop Frequency Synthesizer[J].Radar &Ecm,1994(03):57-63.

[9] Xu H,Peng L.Design of Ultra-broadband Microwave Sources Based on ADF4350[C].International Conference on Advanced Computer Control IEEE,2010:459-462.

[10] Cao H,Qu Y.A Miniaturized Frequency Synthesizer System Design Based on ADF4350[C].IEEE International Conference on Signal Processing,Communications and Computing IEEE,2016:1-4.