高速多负载总线的板级信号完整性仿真与分析*

罗会容,何文浩

0 引 言

随着半导体技术的发展,现代数字芯片的集成度越来越高。同时,为了满足一些数据传输带宽和传输速度的要求,其主频不断提升。一些电路的PCB设计不再仅仅是按照一些设计规则把电路布通,电路板的信号完整性往往也是需要考虑的关键因素。电路板信号完整性关系到单板能不能达到预先设计的功能要求和技术指标,对整个系统的稳定性和可靠性具有重要影响。

1 信号完整性概述

信号完整性(Signal Integrity)是指信号在电路中以要求的时序和电压作出响应的能力。如果电路中信号能够以要求的时序、持续时间和电压幅值达到接收芯片引脚,则该电路具有较好的信号完整性。否则,当信号不能正常响应或系统不能长期稳定工作时,就出现了误触发、过冲等造成时间间歇振荡和数据错误的信号完整性问题[1]。

1.1 板级信号完整性的重要性

在实际的产品设计过程中,由于产品结构的限制,一些频率较高的器件会基于功能的划分而被分配在不同的电路板上,通过接插件或电缆相连接。单板电路的关键信号可以通过仿真方法判断信号完整性的好坏,进而指导PCB布局和布线。对于分布在不同电路板上的高速多载荷总线的信号完整性,需要通过仿真软件先关联板级信号模型,再进行仿真、分析和验证。

板级信号完整性的常见问题:发送端A板上芯片1的高速信号通过接插件到接收端B板上芯片2后,能不能正确判断和接收来自发送端的信号。因为信号反射波与输入信号叠加、信号间的串扰、EMC等因素,造成信号的过充和上升沿振荡,影响信号上升沿的单调性和保持时间,进而影响芯片对信号电平的判断。因为上升沿的振荡会出现将高电平判断为低电平,或者将低电平判断为高电平,如图1所示[2]。

图1 信号逻辑判断

传统的PCB设计是完成原理图的设计和元器件的布局与走线后直接制版,再测试几个板的系统性能。但是,一旦修改设计就会浪费时间、增加成本,在竞争激烈的电子行业是不被接受的。而避免这些缺点的最好方法,就是进行板级信号完整性仿真。板级信号完整性仿真工具可对多板、连接线、电缆等组成部分进行仿真,然后提出修改建议,消除信号完整性问题,从而提高一个产品或者一个系统的稳定性和可靠性。

1.2 常用的仿真工具和方法

SI分析工具众多,如Ansoft公司的SIwave、Cadence公司的SPECCTRAQuset、Mentor Graphic公司的IS_Analyzer、HyperLynx公司的LineSim等。在工程设计和信号完整性仿真领域,应用较多的是Cadence公司的SPECCTRAQuset。本文采用该工具,并结合实际工程应用,对板间信号完整性进行仿真和分析[3]。

2 高速多负载总线板间信号完整性仿真方法和分析

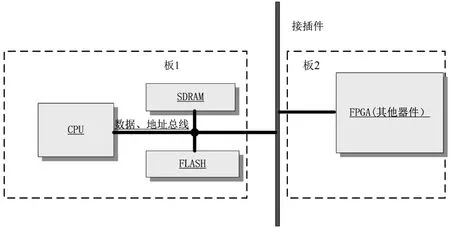

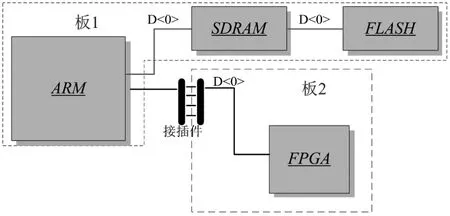

在实际电路设计过程中,高速多载荷的芯片多为控制型(或处理型)CPU,如ARM、PowerPC、DSP等,其数据线和地址线往往连接SDRAM、FLASH。由于CPU还要对相应的数据进行协议处理,数据(或地址)总线往往与FPGA或专用协议处理芯片相连接。此外,由于CPU和专用协议处理芯片分布在不同电路板上,二者常需通过接插件连接,连接示意图如图2所示。

图2 连接示意

2.1 板级信号仿真流程

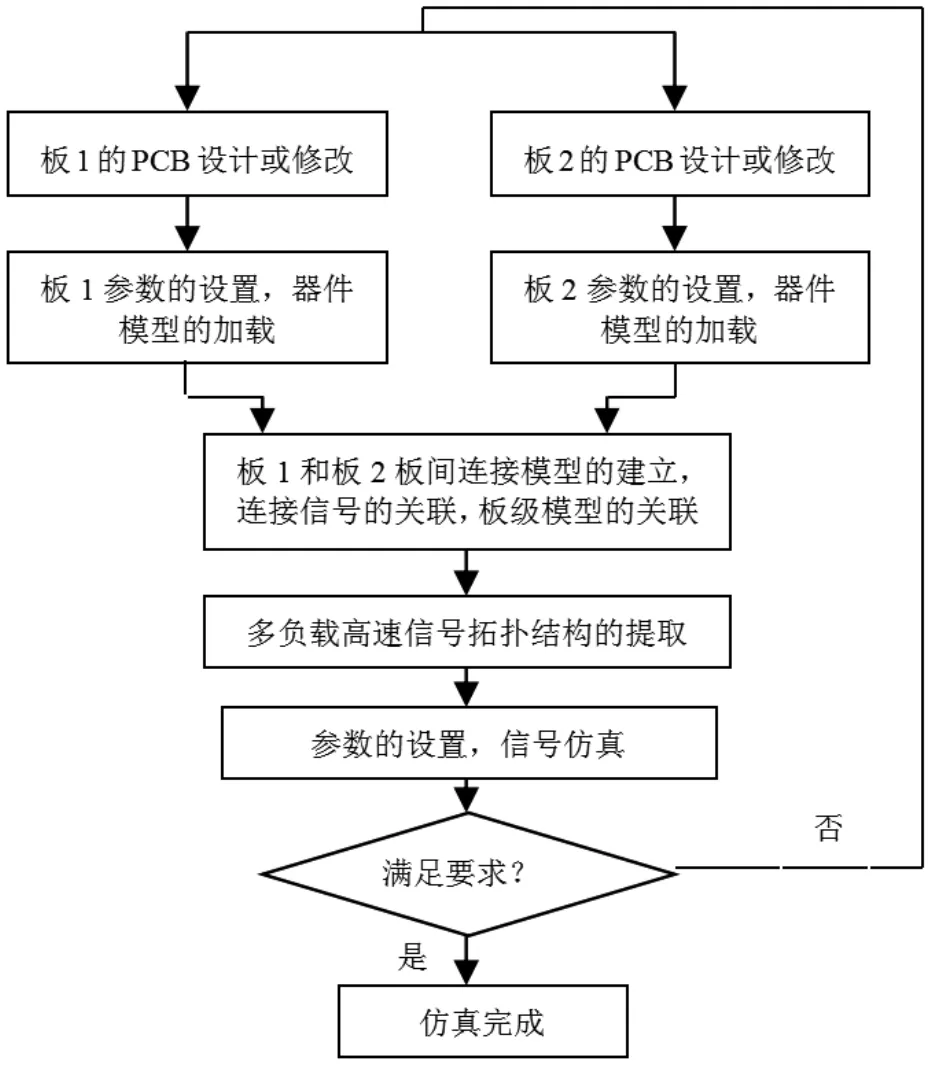

板间信号的仿真可以借助仿真软件实现。Cadence公司的仿真软件SPECCTRAQuset具有板级信号仿真的功能,板级信号仿真流程图如图3所示[4]。

图3 板间信号仿真流程

2.2 仿真系统的建立

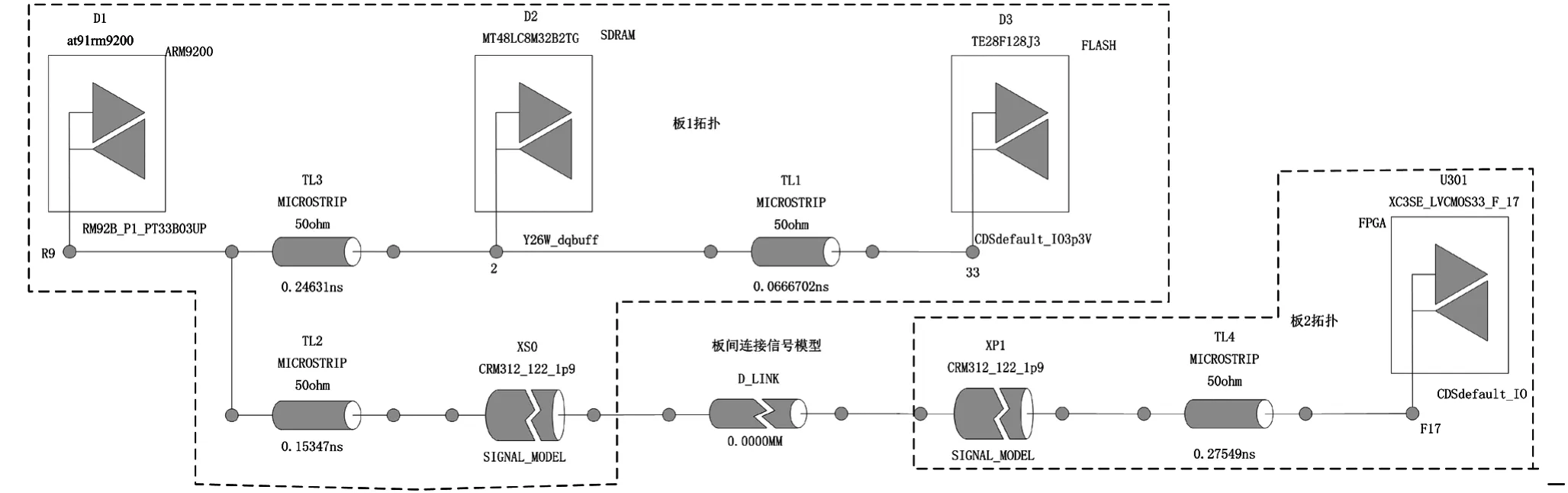

仿真目标系统中,板1为CPU连有SDRAM和FLASH的核心板,板2为含有专用FPGA芯片的协议处理板。两板通过接插件连接,其中CPU型号为AT91RM9200,FPGA型号为FPGA1600E。分析接插件相关参数特性后,构建连接器IBIS模型D_LINK。以CPU和FPGA互联数据总线D<0>为分析对象,分配器件仿真模型提取拓扑结构并关联后,板级信号仿真拓扑如图4所示。

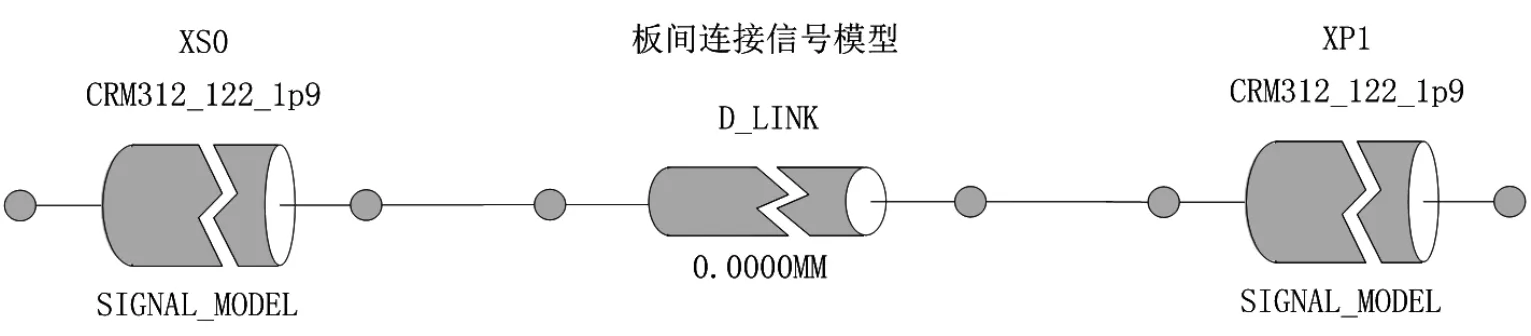

图4中,左上框包含的部分为板1中的拓扑结构,右下框为板2提取的拓扑结构,它们之间通过预先建立的接插件模型D_LINK连接,如图5所示。

2.3 Reflection仿真和结果分析

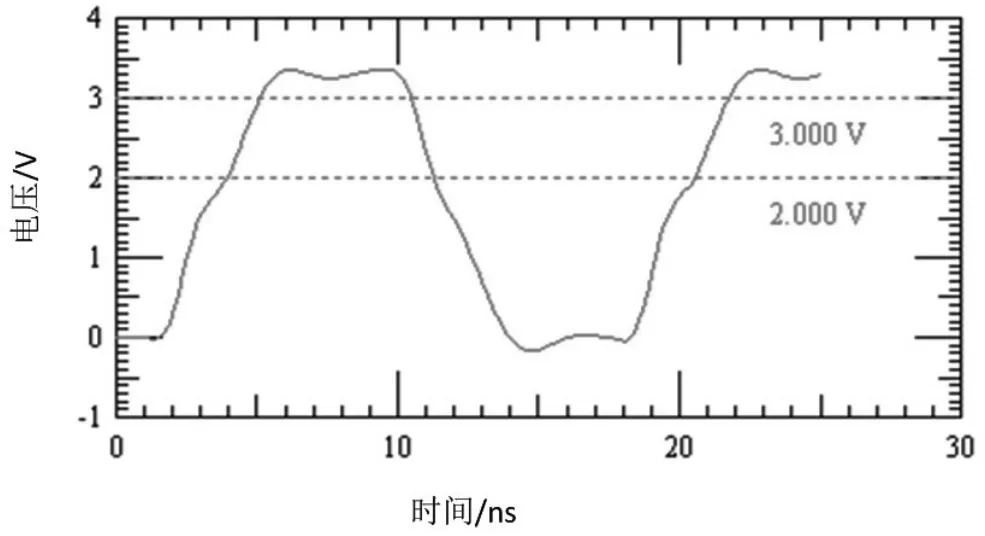

AT91RM9200主时钟频率为60 MHz,数据线在60 MHz左右的频率工作,设置ARM为信号源,根据提取的拓扑结构进行Reflection仿真,仿真波形如图6所示。

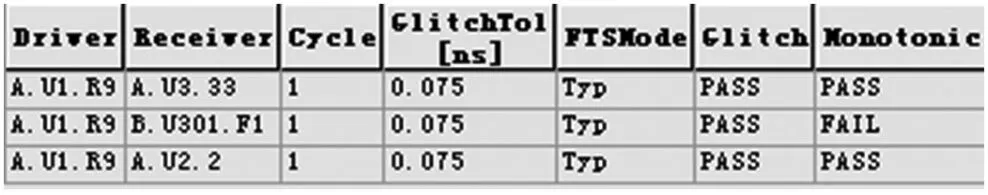

软件根据仿真结果和器件IBIS模型得出的仿真结果,如图7所示。由图7可以看到,对于过冲(Glitch),SDRAM、FLASH、FPGA都通过(PASS),但单调性(Monotonic)U301(FPGA)没有通过(FAIL),即板1中ARM的数据线D<0>的信号通过接插件到板2后,信号的单调性没有通过。FPGA的接收波形如图8所示。

图4 板1和板2数据线D<0>连接信号的拓扑

图5 连接板1和板2的模型D_LINK

图6 D<0>仿真信号波形

减少或者消除反射的方法是依据传输线的特性阻抗,在其发送端或接收端采取一定的匹配措施,使源端反射系数或负载端反射系数为零,从而达到抑制反射的作用[6]。

3 分析与改进

图7 仿真结论

ARM与SDRAM、FLASH以及FPGA连接的拓扑示意图,如图9所示。

图8 FPGA接收波形

图9 系统拓扑

从图8可以看到,上升沿有明显的振荡,影响到FPGA对电平的判断。这是因为两板互联,信号从板1传送到板2,介质阻抗发生了变化,从而导致信号在介质交接处产生了信号反射,影响信号的完整性[5]。此外,由于传输线和负载的阻抗不匹配引起的振荡、过阻尼、欠阻尼等信号完整性问题也较为明显。

由图9可以看到,ARM一端连接SDRAM和FLASH两个载荷,一端只连接FPGA一个载荷,导致接收端阻抗小于传输线阻抗。载荷小的一端FPGA,对来自接收端的信号有一定反射,并与入射波叠加,引起接收芯片FPGA上升沿单调性的振荡,影响传输信号的质量。解决方法为,通过负载端串联端接电阻即在载荷小的FPGA端接电阻来匹配载荷,经过多次反复仿真,此电阻值为50 Ω时效果最好。改进后的拓扑如图10所示。

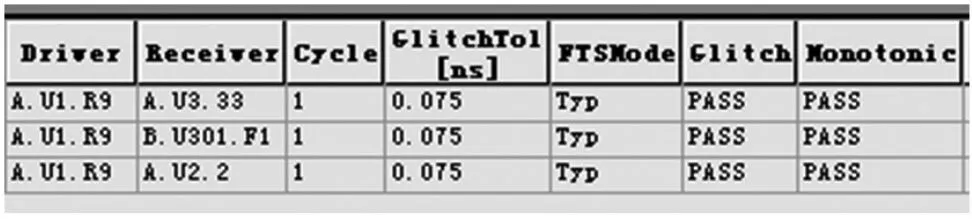

对改进后的拓扑进行Reflection仿真,得到的仿真波形和仿真结果分别如图11、图12所示。

图11 改进后的仿真波形

图10 加端接电阻的拓扑(FPGA前加一匹配电阻50 Ω)

由图12的仿真结果可以看到,SDRAM、FLASH、FPGA的过冲、单调性都通过(PASS)。

通过显示设置,只显示FPGA的接收波形,如图13所示。从图13可以看到,仿真波形上升沿的单调性有明显改进。与图8比较,信号单调性有明显改善,消除了上升沿振荡的影响,使信号边沿严格单调,消除了接收端对发送信号的误判。

图13 改进后FPGA的接收波形

4 结 语

本文针对高速板级多负载总线由于载荷不均导致接收信号上升沿振荡而影响接收端信号单调性的问题,采取串联端接电阻来匹配载荷的方法给予解决。通过仿真验证发现,所提方案能有效提高接收端信号质量,增强信号完整性,可以指导原理图的修改,避免重复制板,节约设计成本和时间,对工程的实际应用具有一定的参考价值。

[1] 董小军,陈岩,杨忠孝.高速数字电路信号完整性问题分析与解决方案[J].中国测试,2010(03):18-21.DONG Xiao-jun,CHEN Yan,YANG Zhong-xiao.Analysis and Solution of Signal Integrity Problems in High Speed Digital Circuit[J].China Test,2010(03):18-21.

[2] 张绍军,黄振.高速数字系统中的信号完整性及实施方案[J].电子技术应用,2002(11):31-33.ZHANG Shao-jun,HUANG Zhen.Signal Integrity and Implementation Scheme in High Speed Digital System[J].Application of Electronic Technique,2002(11):31-33.

[3] 徐永丹,宋海涛,黄志奇等.基于SPECCTRAQUEST多板互联信号仿真与分析[J].电子科技大学学报,2010(04):67-70.XU Yong-dan,SONG Hai-tao,HUANG Zhi-qi,et al.Multi-Board Interlink Signal Simulation and Analysis Based on SPECCTRAQuest[J].Journal of University of Electronic Science and Technology of China,2010(04):67-70.

[4] 周润景,袁伟.Cadence高速电路板设计与仿真[M].北京:电子工业出版社,2006.ZHOU Run-jing,YUAN Wei.Design and Simulation of High Speed Circuit Board[M].Beijing:Electronic Industry Press,2006.

[5] 胡海欣,曹路胜.高速PCB的仿真技术[J].计算机工程与设计,2005,26(03):711-713.HU Hai-xin,CAO Lu-sheng.Simulation Technology of High Speed PCB[J].Computer Engineering and Design,2005,26(03):711-713.

[6] 邵鹏.高速电路设计与仿真分析[M].北京:电子工业出版社,2010.SHAO Peng.Design and Simulation Analysis of High Speed Circuit[M].Beijing:Electronic Industry Press,2010.