基于STM32与FPGA的信号采集电路设计

王 斐, 赵牛杰, 郝志超, 王燕燕, 邸丽霞

(北方自动控制技术研究所, 山西 太原 030006)

我军某型目标识别系统具备光电结合(激光测距、TV跟踪、红外跟踪同全天候的相结合)的特点,且该系统拥有轻便移动、可靠适用、精度高、操作简便等良好性能[1],是现代战争的主战装备.作为当前部队广泛应用的重要装备,其战略地位和实际意义是不言而喻的.部队装备多野外、机动使用,客观条件所限使装备及器材使用数据的采集、汇总、交接常常不够及时,影响了装备的信息化管理,加之系统属于大型复杂装备,其性能和技术状态的有效监控成为主要问题.目前该装备性能变化的动态数据采集缺乏完善的自动化采集手段,完全人工采集存在诸多问题.

其中,PPI(plain position image)显示器用于显示目标原始视频和MTI(moving target indicator)信号、10 km距标、跟踪标志(双脉冲)、敌我识别器标志等信息,搜索状态下提供威力范围内的空情信息,以便捕获选定的目标,跟踪状态下可观察跟踪情况.

文中以PPI显示系统为研究对象,分析其电路特性和信号流程,找到能反映其运行状态的采集点,完成信号采集的电路设计,并将采集到的数据进行处理和整合,打破传统的采集方式,根据被测信号的时序性,通过内部触发和外部触发两级控制,完成采集.这种方式更灵活,采集系统与被采信号具有更好的交互性和时序性.

1 信号采集总体设计

数据采集需要一定的采集设备,传统以PC形式为主通用计算机的采集装置体积大、成本高,安装较为繁琐[2],在实际使用中有一定的局限性;而以嵌入式系统为核心的数据采集装置相对而言适合这种特定应用的背景,使用FPGA(field-programmable gate array)[3]器件,在不失较高性能的情况下,保持了采集装置较小体积和较低功耗.所以,选用嵌入式系统作为数据采集的应用平台,设计一种目标信号采集板.目前,嵌入式系统在数据采集领域已经有很广泛应用,有许多性能出色的芯片可供开发设计,也有许多成熟的商业产品可以直接使用,在实际应用中装备通过信号采集板获得目标信号.

PPI显示器是由扫描电压产生器、锯齿形成电路、偏转功率放大器、视频放大器、故障诊断和报警电路、直流电源、高压电源及显示管头电路等组成.PPI显示器体制为定圈式、磁偏转、电聚焦、随机扫描,采用在两对正交固定的偏转线圈中分别产生一个水平偏转磁场和一个垂直偏转磁场,形成径向扫描;获得径向圆周扫描时,两对偏转线圈中磁场随时间按正、余弦规律变化[4].

在正常状态下,由定时器送来的2 MHz时钟信号和PPI触发脉冲经长线接收通过信号选择电路送入距离标定电路,距离标定电路送出的触发脉冲在2 MHz时钟的同步下产生≥300 μs扫描方波,在扫描方波的同步下产生10 km距离标志.10 km距离标志在标志增辉电路中经放大后与放大的询问应答标志和跟踪标志叠加,视频信号经放大后送混合电路与标志信号混合输出送CRT(cathode ray tube)栅极.在方位扫描支路中,根据当前的方位角经过A/D转换器转换出正、余弦电压[5].该电压在扫描正程方波的控制下,产生受正、余弦调制的锯齿波电压、锯齿波电压由功率放大后推动x,y偏转线圈产生旋转磁场.

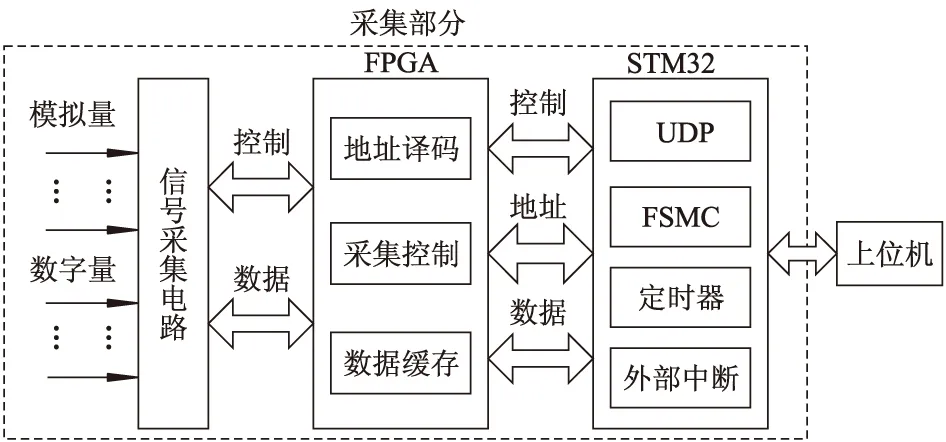

目标信号采集板的设计是数据采集部分软硬件设计中主要完成的工作,由于所采集的信号复杂多样,有多通道、串并混合的特点,所以以单个器件构成的采集系统往往难以胜任,考虑到系统工作效率、外设资源以及造价成本等多方面的因素,文中采用如图1所示的数据采集板设计方案,采用STM32+FPGA的组合方式,利用STM32丰富的外设功能和数据处理能力[6],以及FPGA灵活的逻辑可操控性和并行处理速度快[7]等特征,实现目标信号的采集、处理和传输.

图1 目标信号采集板结构图

目标信号采集板主要由核心器件FPGA,STM32以及采集电路组成,信号的采集由FPGA控制完成,内部的电路功能主要包括地址译码、逻辑控制、数据缓存,在采集完成后,FPGA告知STM32读取采集结果,最后,由STM32对得到的数据进行处理和传输.试验平台搭建如图1所示.

2 硬件电路设计

根据目标信号采集板的总体设计需求,硬件电路设计中应有STM32系统电路、FPGA及配置电路、接口电路以及与之相关的各组成部分, 目标信号采集板如图2所示.

图2 目标信号采集板

STM32最小系统是指能使STM32正常工作的最小电路[8],主要包括STM32微控制器、JTAG下载接口、晶振、电源和复位电路.选用的STM32的引脚封装为LQFP144.

供电电源:STM32使用单电源供电,电压范围为1.8~3.6 V;除此之外,还有2个可选的电源模块,使用备用纽扣电池为实时时钟和一部分备份寄存器供电,当STM32进入深度节点模式时在备份电池的支持下保持数据不丢失;若启用ADC功能,有额外的参考电压引脚VERF+和VERF-,VERF-引脚与VCCA相连,而VERF+接2.4 V~VCC.

下载和复位:STM32下载调试使用5针的JTAG接口,通过J-Link在线下载,为了方便调试,在nRST引脚连接简单的复位电路,并与JTAG调试端口相连,既可实现手动复位,也可使用开发调试工具强行复位STM32.

启动方式:通过STM32的2个外部引脚BOOT0和BOOT1来选择最小系统的启动方式.这里选择将这2个引脚分别与GND相连,即STM32存储空间的起始地址对齐到用户FLASH模块.

时钟源:STM32带有内部RC振荡器,可以为内部PLL(锁相环)提供时钟,但是内部RC振荡器相比而言不够准确[9],

同时也不够稳定.在本设计中使用外部时钟源,外接2个晶振为其内部提供时钟源:一个为外部高速时钟(HSE),使用25 MHz晶振系统提供较为精准的168 MHz主频;另一个是外部低速时钟(LSE),接频率为32 768 Hz晶振,提供日历时钟功能.

FPGA及配置电路:FPGA即现场可编程门阵列,它是在PAL,GAL,CPLD等可编程器件的基础上进一步发展的产物.在FPGA工作过程中,FPGA是通过片内RAM中的程序来设置芯片的工作状态的,但是片内RAM的数据掉电会丢失,所以在设计中需要选择一个非易失性的存储器来存储配置程序,通常将这种存储器称为配置芯片.

AD转换电路:STM32自带AD转换器,但是输入量程较小,电压分辨率小,对模拟信号的输入、调理电路设计要求较高,难以有效抑制噪声、提高信噪比.针对上述情况,设计选用MAXIN公司生产的MAX196作为AD转换器.该芯片外围电路配置简单,有6个单端模拟输入通道,12位采集精度,多量程双极性输入,内部集成有采样保持器,通过具有故障保护功能和多路复用器与内部的ADC相连,每个通道能承受高达16.5 V的输入电压,并且每个通道的故障不影响任何其他通道.

通道转换电路:将外部电路与FPGA芯片连接,在输出电路中由于FPGA的工作电压最高为3.3 V,外设电路的工作电压为5 V,而FPGA向外输出高电平信号并没有达到5 V的电压,加上电路的不稳定,可能该高电平信号就被判定为低电平从而造成数据的丢失.为了解决这个问题,在FPGA与外设电路之间用74245芯片进行缓冲,把FPGA输出的3.3 V提高到5 V,以避免数据的丢失;另外74245芯片还具有双向传输数据能力,根据实际要求,可以通过控制触发端电平的高低,选择数据的传输方向,其原理图见图3.

图3 通道转换电路

3 软件设计

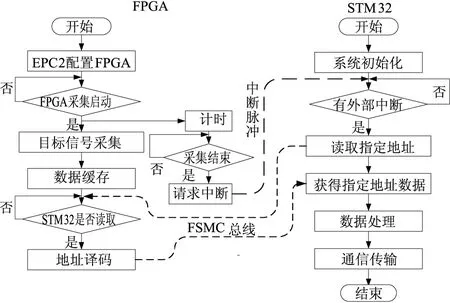

目标信号的采集使用了STM32+FPGA的组合方式,这种组合方式在一定程度上可使各自的长处得以发挥,避免了单一的核心器件在采集和处理上的局限性.利用STM32丰富的外设功能和数据处理能力,以及FPGA灵活的逻辑可操控性,可完成目标信号的采集,采集软件流程见图4.

图4 目标信号采集软件流程

对于STM32的软件设计主要基于ST官方提供的设备固件库,该固件提供了STM32所有外设的底层驱动函数,在这些底层驱动函数的基础上编写应用程序就可以很方便地使用STM32的标准外设;STM32嵌入式系统的开发与传统的单片机系统设计相比,系统开发时间大大缩短[10].开发调试的软件开发环境为Keil uVision4,该软件支持最新的Cortex-M4内核处理器,能够自动配置启动代码,集成了Flash烧写模块、强大的设备模拟、性能分析器等单元.

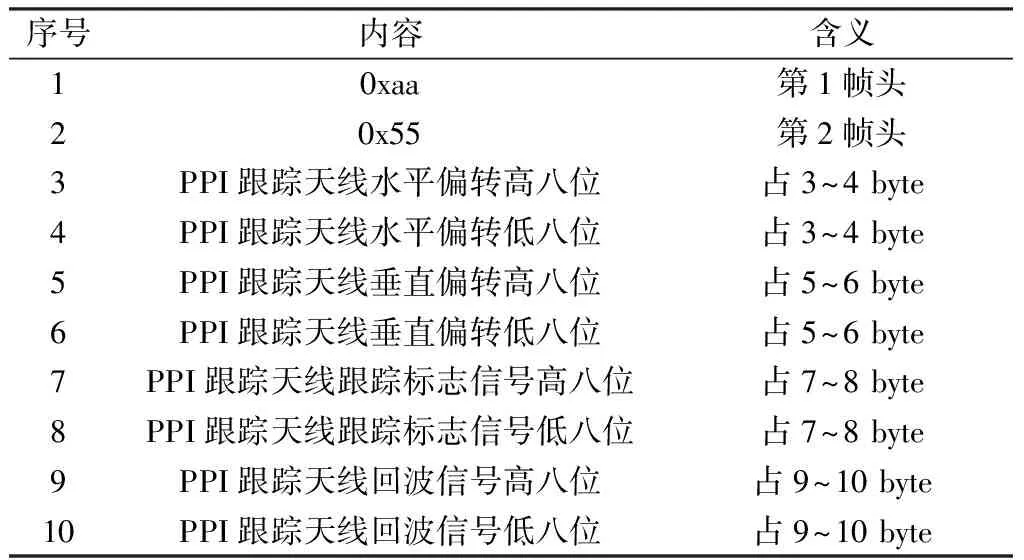

上位机与下位机之间需要通过网络传输数据,其中遵照UDP协议.UDP协议是user datagram protocol 的简称,即用户数据报协议,是OSI参考模型中一种无连接的传输层协议[11],提供面向事务的简单不可靠信息传送服务,用于处理数据包,虽然其有不提供数据包分组、组装和不能对数据包进行排序的缺点,UDP协议仍不失为一项非常实用和可行的网络传输层协议.文中使用UDP协议连接上位机与下位机,通过网络进行传输,具体协议见表1.

表1 通信协议(下位机发上位机收)

FPGA能够控制采集电路完成数据的采集,关键在于FPGA内部逻辑的设计,也可称为FPGA的开发.FPGA作为一种可编程的逻辑器件,从广义上讲,就是可以通过软件手段更改配置器件内部连接结构和逻辑单元,完成既定设计功能的数据集成电路[12].FPGA的设计开发使用Altera公司的综合开发平台QuartusⅡ,该软件集成了Altera的FPGA开发流程中所涉及的所有工具和第三方软件接口,支持器件种类众多,通过使用此综合开发工具,可以方便的创建、组织和管理自己的软件.对于FPGA需要能够顺利进行高效、低耗地工作,同时要对整体的内部运行的空间简化、编译,因此在FPGA里设计一个译码电路,原理图见图5.

图5 译码模块

如图5所示,在该译码电路里,采用器件74688,74154.在74688器件中Q0-Q5接地,而Q6-Q7外接电源,数据输入接口(P0-P7)连接数据锁存电路的A8-A15,完成对高位数据的译码.

74154单片4线至16线译码器是一款高速CMOS器件,非常适用于高性能存储器[13].当G1N和G2N为低时,它可将接受的4位有效二进制地址输入(在该电路中,输入端连接数据锁存电路输出的A0-A3),并提供16个互斥的低有效输出,产生译码地址,地址具体功能见表2.

表2 FSMC总线控制命令

实现调解的方法如下:用4个输入线写出输出线的地址,使得在一个选通输入为低时数据通过另一个选通输入;任何一个选通输入为高时,所有输出都为高.

4 关键模块设计

4.1 数据锁存模块

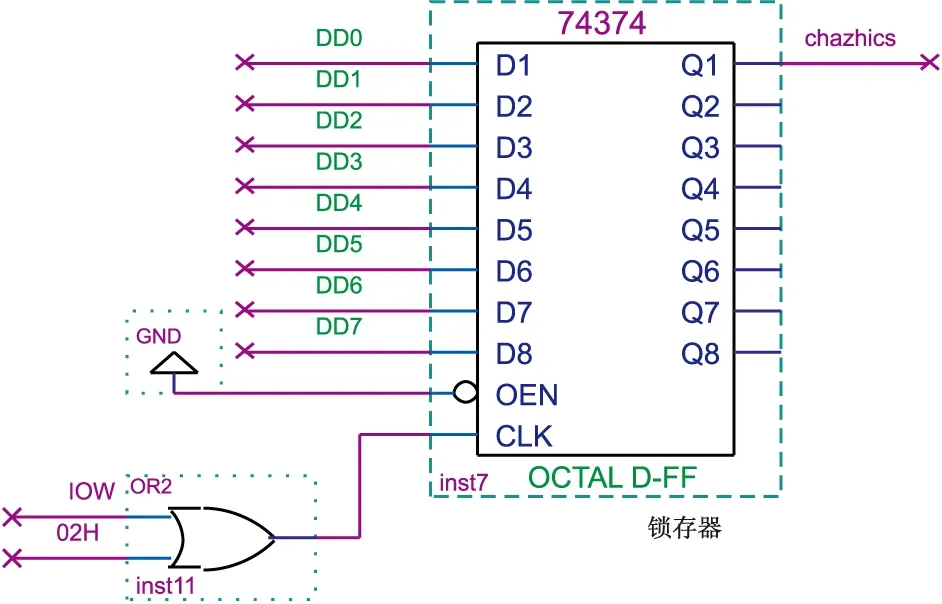

74374为三态输出的8D透明锁存器,具有锁存允许输入有回环特性.当三态允许控制端OE为低电平时,D0-D7为正常逻辑状态,可用来驱动负载或总线.锁存允许端G通过外接I/O接口与单片机AT89S52地址锁存允许信号管脚ALE/PROG 连接,当锁存允许端G为高电平时,输出随数据输入而变.当G为低电平时,输出被锁存在已建立的数据电平,如图6所示.

图6 数据锁存模块

4.2 双向缓冲选通模块

双向缓冲对于由外部MAX196经过A/D转换后的数据,处理时需要进行缓冲,再次返回MAX196,因此需要一个能实现双向传输数据功能的电路.双向缓冲模块如图7所示.

图7 双向缓冲模块

在此选用2个74244器件,当1GN,2GN为高位时,Y为高阻抗;当1GN,2GN为低位时,Y为A.当外接RD为高位时,数据流向是由内部(D0-D7)传输至外部(DD0-DD7);当外接RD为低位时,数据流向是由外部(DD0-DD7)传输至内部(D0-D7).

4.3 MAX196控制模块

该模块的输入端——使能端由译码器产生的地址和单片机传输过来的写信号以或门的形式控制,输出端连接MAX196,控制其采集经过A/D能转换后的数据.而后exint端给STM32输出所读的中断信号,当译码器产生的地址和单片机传输过来的读信号以或门的形式控制74541,读取数据data[11..0],实现了采集模拟量的设计.原理如图8所示.

图8 MAX196控制模块

同时采集了控制信号,对应的控制信号如图9所示,其中D0为en信号,D1为片选信号,D2为写信号,D3为MAX196中断信号,D4为读信号,D7为外部中断信号.

图9 控制信号

当该模块采集完2路信号-正弦值和余弦值后,通过反正切函数求取扫描线的偏转角度,达到实际应用目的.

4.4 差值测量模块

差值测量模块如图10所示,该模块用于计算2个信号之间的延时,采集跟踪标志信号和回波信号,确定跟踪标志在扫描线的位置和回波的位置.其有4个输入端,其中cs端控制模块是否工作,输出端连接74541,当译码器产生的地址和单片机传输过来的读信号以或门的形式控制74541,读取数据data[14..0],实现了采集数字量的设计.当采集完差值个数后,乘以时钟的周期,得到差值时间,送至单片机,单片机完成计算距离的工作,达到实际目的.差值测量仿真图见图11.

图10 差值测量模块

图11 差值测量仿真图

cs端控制模块运行,即当cs为高电平的时候,模块运行、计算差值,输出12位数据,如图11所示.

5 结 论

文中以PPI显示系统为研究对象,重点分析了电路特性以及信号流程,找到能反映其运行状态的采集点,完成信号采集的电路设计梳理,搭建信号采集硬件总体结构,并将采集到的数据进行处理和整合,主要对数据传输模式、FSMC总线以及信号采集的接口控制模块的设计方法进行优化,从而使得系统整体具有更加的信号采集能力.这种设计模式打破传统的信号采集方案,根据被测信号的时序性,通过内部触发和外部触发两级控制从而完成信号采集.文中所提方案更加灵活,采集系统与被采信号更具有交互性和时序性.仿真试验也证明了该方案的可行性及优越性.

仍有许多问题需要深入研究,后续工作主要包括:优化硬件设计,选用硬件资源更合适的PFGA芯片;软件系统顶层设计,协调各模块整体功能;根据实际装备进行接口设计等.

)

[1] 程昌彦, 李太全. 基于FPGA的探地雷达数据采集系统设计[J]. 无线电工程, 2017, 47(4): 28-30.

CHENG C Y, LI T Q. Design on data acquisition system of ground penetrating radar based on FPGA[J]. Radio Engineering, 2017, 47(4): 28-30. (in Chinese)

[2] WANG J, LIU S B, XIONG X X, et al. Security enhancement of arbiter-based physical unclonable function on FPGA[J]. Wuhan University Journal of Natural Sciences, 2017, 22(2): 127-133.

[3] 张艳香,陈梦苇,万小强. 基于AD500-9激光测距系统的设计[J].吉林大学学报(理学版),2015,53(4):773-778.

ZHANG Y X, CHEN M W, WAN X Q. Design of laser ranging system based on AD500-9[J]. Journal of Jilin University (Science Edition), 2015,53(4):773-778. (in Chinese)

[4] 张岩, 伍春, 赵志坤. 基于FPGA的多通道数据采集卡的方案设计[J]. 东北师大学报(自然科学版), 2016, 48(4): 63-67.

ZHANG Y, WU C, ZHAO Z K. A design of multi-channel date acquisition card based on FPGA[J]. Journal of Northeast Normal University (Natural Science Edition), 2016, 48(4): 63-67. (in Chinese)

[5] RINDER P, BERTELSEN N. Design of a single frequency GPS software receiver[D]. Denmark Aalborg: Aalborg University, 2004.

[6] 曹彬乾,程远增,杨青. 基于STM32+FPGA的数据采集系统的设计[J]. 计算机工程与设计, 2014, 35(4): 1231-1235.

CAO B Q, CHENG Y Z, YANG Q. Design of data acquisition system based on STM32+FPGA[J]. Compu-ter Engineering and Design, 2014,35(4): 1231-1235. (in Chinese)

[7] 高振斌,赵盼,王霞,等.印刷体数字识别系统的FPGA实现[J].重庆邮电大学学报(自然科学版),2015,27(2):213-218.

GAO Z B, ZHAO P, WANG X,et al. Printed digit re-cognition system based on field programmable gate array[J].Journal of Chongqing University of Posts and Telecommunications (Natural Science Edition), 2015,27(2):213-218. (in Chinese)

[8] VENDELIN G D, PAVIO A M, ROHDE U L. Microwave Circuit Design Using Linear and Nonlinear Techniques[M]. [s.l.]:Wiley-Interscience, 1990.

[9] 王龙, 杨承志, 吴宏超, 等. 基于FPGA的数字基带多模雷达信号源设计[J]. 电子技术应用, 2016, 42(8): 87-90.

WANG L, YANG C Z, WU H C, et al. The design of digital multi-mode radar signal generator based on FPGA[J]. Application of Electronic Technique, 2016, 42(8): 87-90. (in Chinese)

[10] 李红刚, 杨林楠, 张丽莲, 等. 基于FPGA的高速多通道数据采集系统的设计[J]. 计算机测量与控制, 2006, 14(10): 1407-1409.

LI H G, YANG L N, ZHANG L L, et al. Design of high speed multichannel dara gathering system based on FPGA[J]. Computer Measurement & Control, 2006, 14(10): 1407-1409. (in Chinese)

[11] 何艳, 张流强, 张建, 等. 基于FPGA的高速峰值检测[J]. 核电子学与探测技术, 2016, 36(1): 43-47.

HE Y, ZHANG L Q, ZHANG J, et al. High-speed peak detecting based on FPGA[J]. Nuclear Electronics & Detection Technology, 2016, 36(1): 43-47. (in Chinese)

[12] 刘怿恒. 基于FPGA的数据采集与处理系统设计[D]. 长沙:湖南大学, 2013.

[13] BAKLOUTI M, AYDI Y, MARQUET P, et al. Scalable mpNoC for massively parallel system-design and implementation on FPGA[J]. Journal of Systems Architecture, 2010, 56(7): 278-292.