高速电路设计中信号完整性的反射分析

雷 佩,穆平安,徐德俊

(1.上海理工大学 光电信息与计算机工程学院,上海 200093;2.上海自动化仪表股份有限公司 技术中心,上海 200072)

随着集成电路的复杂程度逐渐增加,系统时钟和总线频率不断提高,随之而来的信号完整性问题变得尤为突出[1]。然而,随着电子设计的集成化导致电路的布局布线密度变大,同时信号的频率还在不断提高,从而使得如何解决高速信号完整性问题成为电路设计的关键。

关于高速信号完整性的研究已有一些成果,文献[2]研究了信号完整性设计中的抖动与振铃消除技术;文献[3]通过对嵌入式系统中DDR2电路部分进行信号完整性分析,提出了PCB设计要点;文献[4]对高速电路中信号完整性问题做了综合介绍,主要针对串扰问题提出了解决措施。基于上述成果,本文主要对高速电路中的信号反射问题进行了研究,提出了解决反射问题的几种端接匹配方式,并通过实际的信号传输模型对不同端接匹配方式进行了仿真验证。

1 信号完整性

信号完整性(Signal Integrity,SI)是指电路信号能够在不影响系统其他信号质量的前提下,通过一段传输路径后到达接收端口波形的完整程度[5]。在时钟频率超过100 MHz或上升时间小于1 ns的高速电路中,信号在传输过程中会受到传输线效应、电磁干扰、噪声等影响,信号质量都会有一定程度的下降,问题严重时可导致接收端不能正确识别,造成系统失效[6]。

本文对高速电路设计中单一网络信号完整性的反射问题展开研究。单一网络通常由一条传输线连接一个设备的源端和另一个设备的负载端而构成,当源端输出信号时,构成信号的电压和电流将传输线看成是一个阻抗网络。当信号在该网络上传播而由于阻抗不连续发生信号突变时,在信号的突变处便会产生反射现象。

2 传输线模型

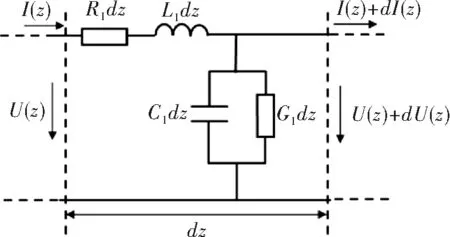

传输线通常定义为能够在两个或多个终端间有效传输电能量或电信号的传输系统[7]。在一般的电路系统中,所涉及到的传输网络都是集总参数的,即电路中各个点之间的信号是瞬间传递的。而在高速电路系统中,信号是以电磁波的速度在互连线上传输的,此时电路参数是在空间分布的,因此必须考虑传输线分布参数对信号的影响[8]。为了将分布参数电路转化为集总参数电路来分析,可用图1的RLGC模型[7-8]来表示传输线的微分等效电路。其中,串联电阻R1dz表示传输线并不是纯导体而是有损耗的;并联电阻G1dz表示隔离地平面和传输线的绝缘介质是有限大的电阻;串联电感L1dz表示传输线的磁场特性;并联电容C1dz表示传输线和地平面之间的电场特性。

图1 传输线微分段等效电路

理论上将传输线上任意点的电压和电流的比值(即Z0=V/I)定义为传输线的特性阻抗Z0[6-7]。利用上述模型,可以得出传输线阻抗表达式

(1)

式中,ω=2π·f,f为信号频率。通常情况下 和 远比其他项小,所以式(1)可近为

(2)

即理想传输线的特性阻抗只取决于连线的单位分布电容和单位分布电感。可以借助类似电磁场求解器这样的工具计算L、C分量,从而得到传输线特征阻抗Z0。

3 信号反射与反射的解决方法

3.1 反射的形成

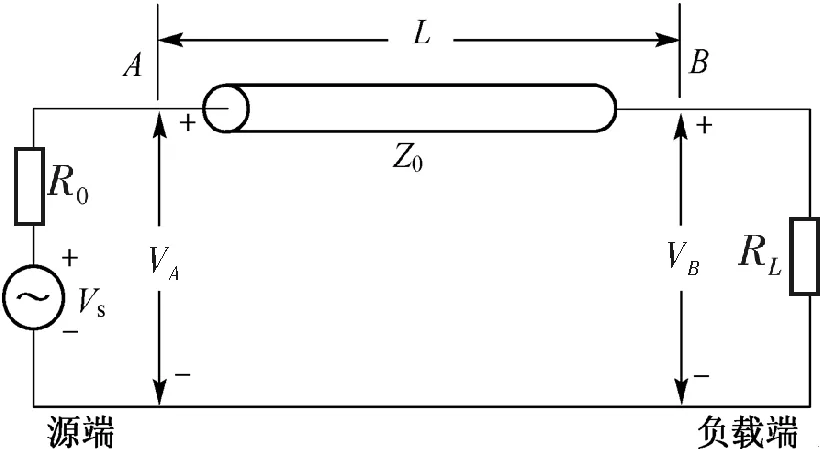

反射就是信号在传输线上的回波。如果一条传输线的电尺寸满足长线的要求时,且没有被合理地端接,那么来自于源端的信号脉冲在负载端被反射,从而引发不预期效应,使信号轮廓失真。可以用图2所示的理想传输线模型[6-7]来分析与信号反射有关的重要参数。图2中VS为驱动源,其内阻为R0,Z0为理想传输线L的特性阻抗,RL为负载阻抗。

图2 理想的传输线模型

根据传输线理论,当负载端阻抗与传输线阻抗不匹配,即RL≠Z0时,一部分信号将在负载端(B点)沿着传输线反射回源端(A点)。反射的大小可以用负载反射系数ρL来衡量,反射系数定义为该反射节点上的反射电压与入射电压的比值[7-9]

(3)

当信号在负载端被反射回源端时,若源端阻抗不等于传输线阻抗(R0≠Z0)就将产生二次反射[8],此时反射电压的幅值由源端反射系数ρS决定,见下式

(4)

理想的情况是当Z0=R0=RL时,传输线阻抗是连续的,不会发生任何反射。但能量的一半消耗在内阻R0上,另一半消耗在负载电阻RL上[10]。如果传输线的源端和负载端都存在阻抗不匹配,信号将在源端和负载之间来回反射,而反射往往会带来过冲/下冲及振荡等信号完整性问题,严重时会导致系统无法正常工作。因此,解决反射问题是保证高速电路信号完整性的关键内容之一。

3.2 反射的解决方法

由上述分析可知,信号的反射是由于源端、负载端和传输线的阻抗不匹配造成的,抑制反射的主要理论依据是通过适当的阻抗匹配让负载反射系数或源端反射系数为零[5-8],通常有两种策略:(1)使负载阻抗与传输线阻抗匹配,即并行端接;(2)使源阻抗与传输线阻抗匹配,即串行端接。

在实际高速电路设计中,要根据具体情况来选择串行端接或并行端接方式,有时也会同时采取两种端接方式。从系统设计者的角度,应首选策略(1),其因是在信号能量反射回源端之前在负载端消除反射,因而消除一次反射,这样可以减小噪声、电磁干扰以及射频干扰;而策略(2)则是在源端消除由负载反射回来的信号,只消除二次反射,在发电平转换时,源端会出现持续时间为2TD的半波波形,不过此策略简单易行,在许多应用中被广泛采用[11]。以下分别介绍这两类端接方案:

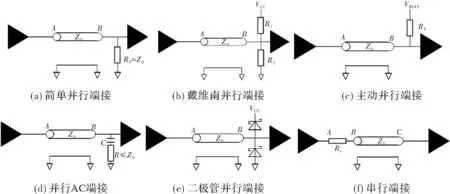

(1)并行端接。并行端接的主要原理是在尽量靠近负载端的位置加上拉或下拉电阻,使终端负载的等效阻抗和传输线的特性阻抗匹配[7-11],以达到抑制反射的效果。根据不同的应用环境和效果,可以分为5种类型:1)简单并行端接:这种端接方式是在靠近负载端处添加一个下拉到地的电阻RT(RT=Z0)来实现匹配,如图3(a)所示;2)戴维南并行端接 :该方式是采用上拉电阻R1和下拉电阻R2构成端接电阻RTH(RTH=R1//R2=Z0),如图3(b)所示;3)主动并行端接:在此端接策略中,端接电阻RT(RT=Z0)将负载端信号拉至一偏置电压VBIAS,如图3(c)所示;4)并行AC端接:该方式是采用电阻和电容网络(串联RC)构成端接阻抗,如图3(d)所示。电阻R值应小于等于传输线的特征阻抗Z0(即R≤Z0),一般情况下电容C=3Tr/Z0,Tr为信号上升时间;5)二极管并行端接:某些情况可以使用肖基特二极管或快速开关硅管进行传输线端接,条件是二极管的开关速度至少比信号上升时间快4倍以上。典型的二极管端接如图3(e)所示。

(2)串行端接。串行端接是通过尽量在靠近源端的位置插入一个电阻RS(典型值为10 ~75 Ω)到传输线中来实现的[10],如图3(f)所示。串行端接是匹配信号源的阻抗,所插入的串行电阻阻值加上驱动源的输出阻抗应大于等于传输线阻抗。这种策略通过使源端反射系数为零从而抑制从负载反射回来的信号,主要是消除二次反射的影响[9-10]。

图3 6种端接匹配方式

4 反射仿真分析

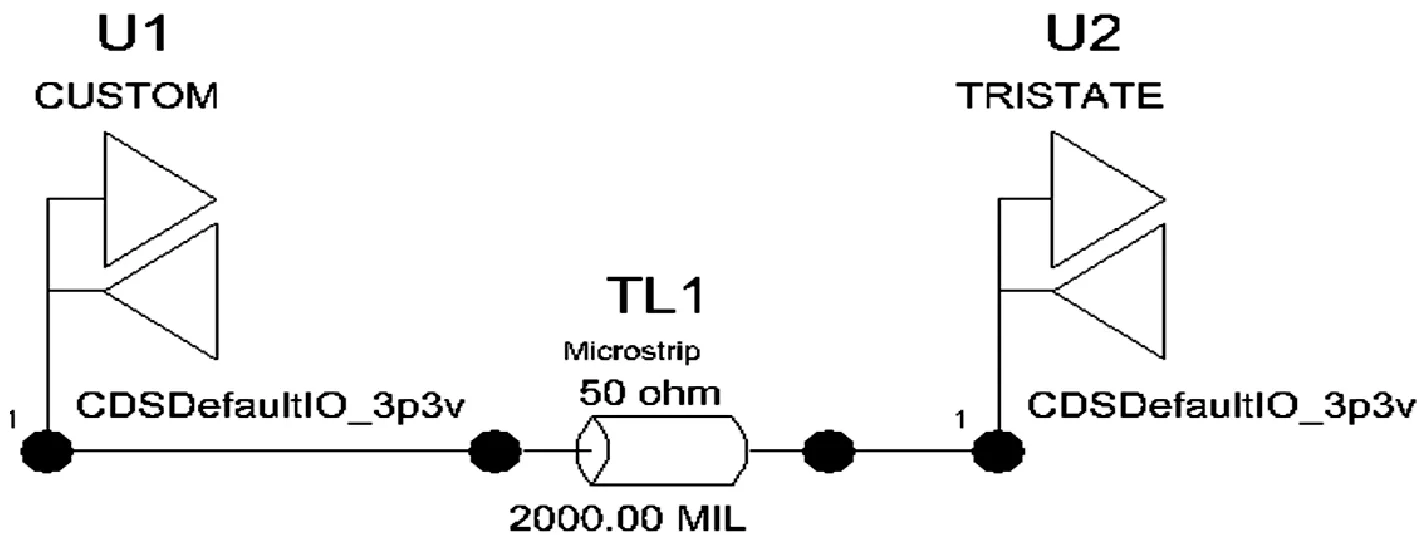

根据以上阻抗匹配理论可知,源端和负载端阻抗匹配方法均能有效解决高速电路中信号反射的问题。针对反射现象,借助Cadence公司的SpecctraQuest仿真工具[12-13]对一个点对点信号传输网络在不同端接方式下进行反射仿真,该网络的仿真模型如图4所示。仿真基本条件为:微带传输线特性阻抗为50 Ω,线长2 000 mil,驱动和接收缓冲器均采用IBIS(输入/输出缓冲器)模型[14-15],其中驱动器U1的上升沿速率为0.833 ns,输出幅度为0~3.3 V、频率为100 MHz、占空比为50%的高低电平信号。

图4 反射仿真模型

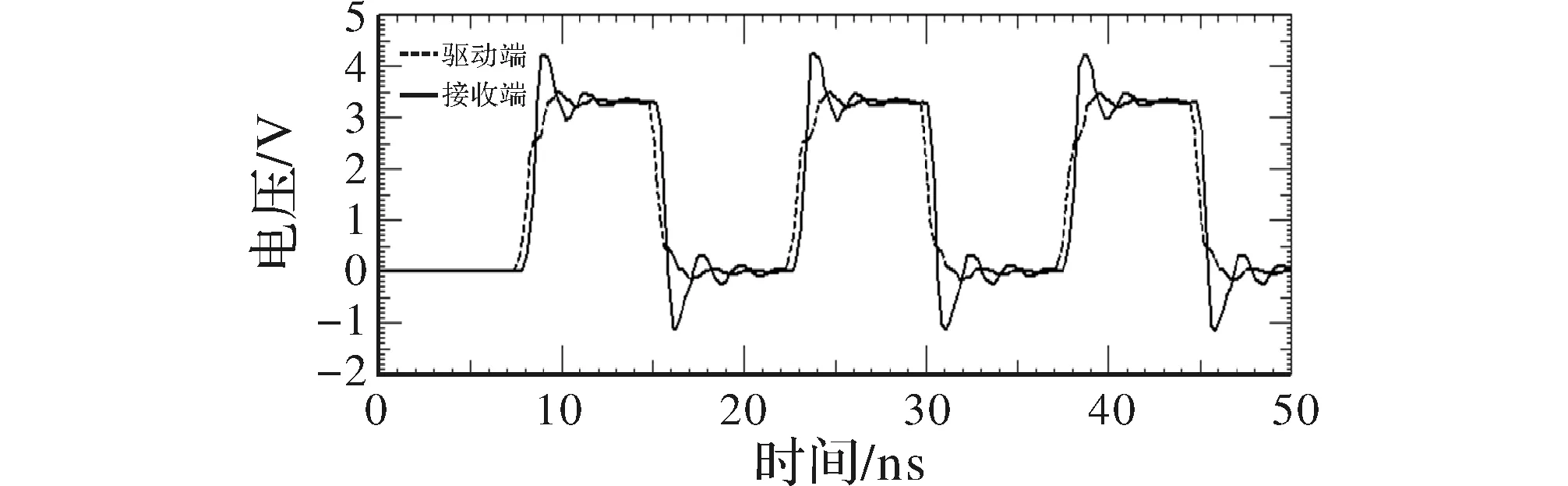

图5为未进行任何端接匹配时的仿真结果,从仿真波形可以看到,在信号的平坦时期,也就是高低电平期间,产生了严重的过冲和下冲以及振铃现象。在高速系统中,振铃现象的存在会使信号多次跨越电平逻辑门限从而导致逻辑功能紊乱,严重时会使系统失效[8-11]。

图5 未端接时驱动端和接收端的电压波形

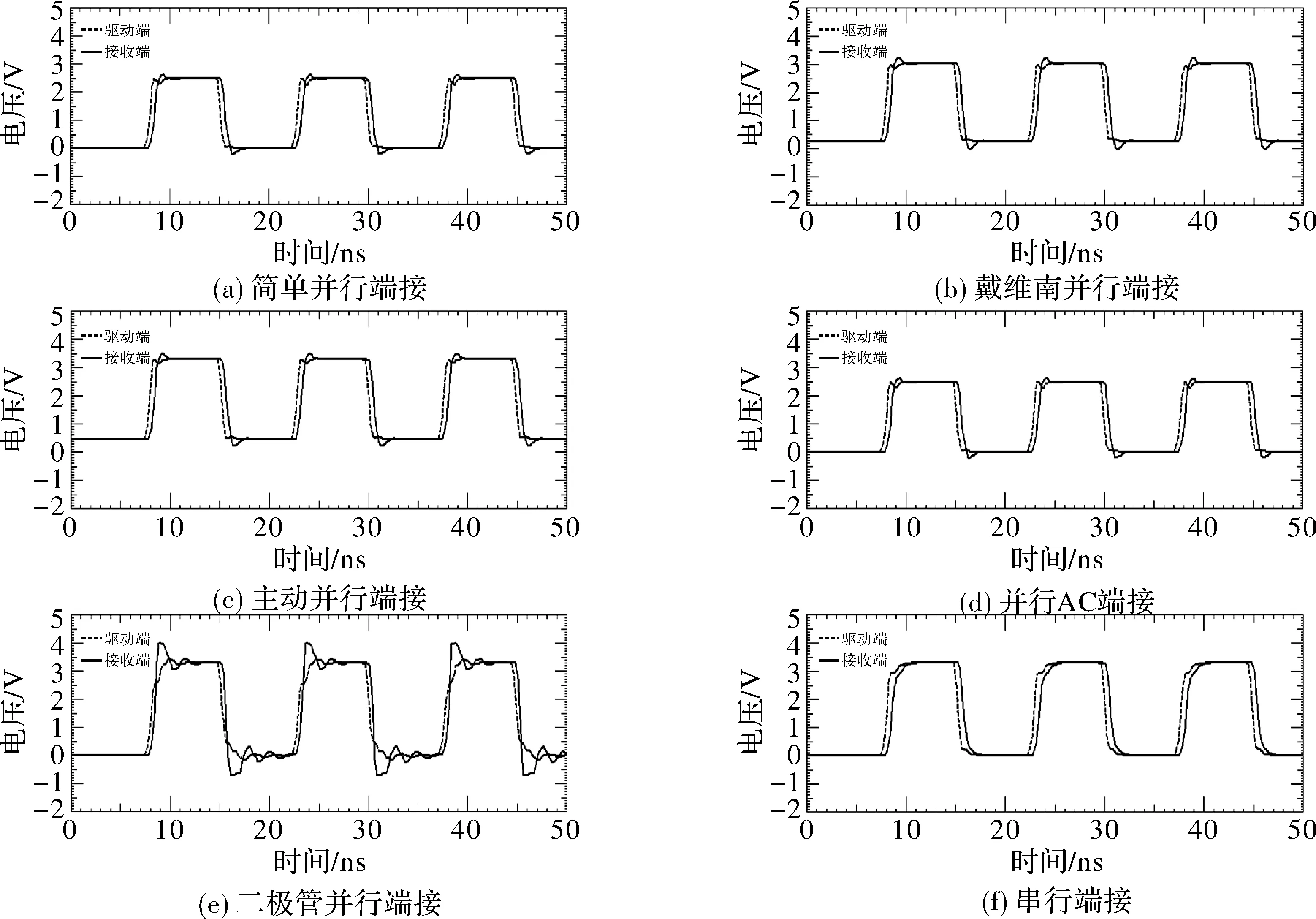

图6显示了对电路加不同端接策略后,驱动端和接收端的信号波形,表1为未端接以及不同端接方式的仿真测量结果。图6(a)为简单并行端接后的波形,并联电阻RT为50 Ω;图6(b)为采用戴维宁并行端接后的波形,并联电阻R1为80 Ω,并上拉至3.3 V偏置电压,电阻R2为120 Ω,并下拉到地;图6(c)为采用主动并行端接后的波形,端接电阻RT为50 Ω,偏置电压为3.3 V;图6(d)为采用并行AC端接后的波形,端接电阻R为45 Ω,端接电容C为0.1 μF;图6(e)采用二极管端接后的仿真波形;图6(f)为源端采用串行端接后的波形,由于源端驱动器的输出阻抗大约为5 Ω,对于特性阻抗为50 Ω的微带传输线,端接电阻R选为45 Ω。

图6 各种端接方式下的仿真波形

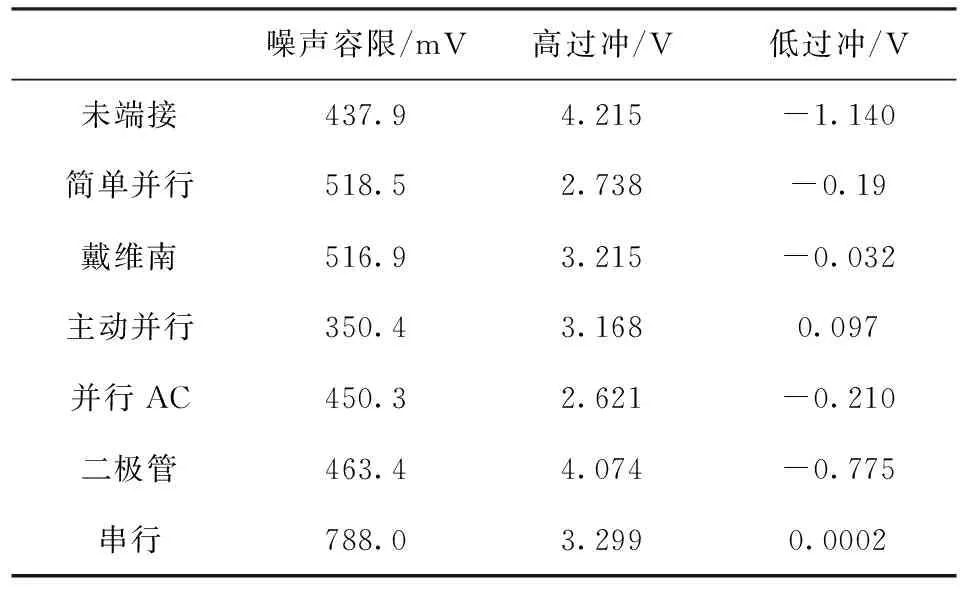

噪声容限/mV高过冲/V低过冲/V未端接437.94.215-1.140简单并行518.52.738-0.19戴维南516.93.215-0.032主动并行350.43.1680.097并行AC450.32.621-0.210二极管463.44.074-0.775串行788.03.2990.0002

从图6的仿真波形可以看到,与未端接前相比,每种端接方式都能不同程度的抑制信号反射,但各种端接方式对信号的影响是有一定差别的。从表1的仿真结果可以看出,在未进行任何端接时,4.215 V的高过冲和-1.14 V的低过冲明显超过了接收端允许的最高电压3.3 V和最低电压0 V,使信号在传输过程中明显失真;此外,在各端接方式中,串行端接方式对反射噪声的抑制作用最为明显,其次是戴维南端接方式和简单并行端接方式;二极管端接方式对反射噪声的抑制作用最弱,简单并行端接方式提高了噪声容限;并行AC端接会拉低信号的高电平,同时主动并行端接会抬高信号的低电平,而如果该低电平接近低电平门限,就会使信号在实际电路中变得不可靠。由此说明,在电路设计中要根据信号质量的要求并综合考虑端接技术对信号的影响,才能得到最佳的端接匹配效果。

5 结束语

在高速电路设计中,由反射引起的振铃、过冲、下冲等信号完整性问题是设计过程中必须解决的问题,借助Cadence公司的仿真工具,对高速电路中由于阻抗不匹配引起的反射问题进行了仿真分析,证实了阻抗匹配方式能够改善信号传输的反射现象。探讨了单一网络的信号反射问题,而对于单一驱动源驱动多负载的情况,阻抗匹配方式也同样适用。同时,高速电路设计是一个非常复杂的过程,设计者可以在设计阶段采用仿真工具建立高速电路模型,对信号完整性问题进行优化,提高设计的成功率。

[1] 周润景,王艳红.Cadence高速电路板设计与仿真[M].5版.北京:电子工业出版社,2015.

[2] 佟星元,朱樟明,杨银堂,等.信号完整性设计中的抖动与振铃消除技术[J].电子科技,2012,39(6):136-141.

[3] 思维,凌凯.DDR2高速PCB设计和信号完整性分析[J].电子科技,2015,28(4):132-138.

[4] 朱园园.高速电路设计中的信号完整性研究[J].电子技术与软件工程,2015(20):36-38.

[5] 章云.高速电路中的信号完整性分析与仿真[D].上海:上海交通大学,2014.

[6] 王雪坤.高速电路设计中的信号完整性分析[D].苏州:苏州大学,2013.

[7] 杨章平.高速PCB设计中的信号完整性分析研究[D].成都:电子科技大学,2014.

[8] 丁立涛.高速电路设计与信号完整性分析[D].西安:西安电子科技大学,2011.

[9] 张松松,刘飞飞.高速电路板级信号完整性设计[J].电子科技,2013,26(10):105-109.

[10] 邬利芳,侯永刚.基于仿真的信号完整性设计与分析[J].信息通信,2012(5):49-50.

[11] 吴业舟.高速电路板的信号完整性分析与设计[D].上海:上海交通大学, 2013.

[12] 覃婕,阎波,林水生.基于Cadence-Allegro的高速PCB设计信号完整性分析与仿真[J].现代电子技术,2011,34(10):169-171,178.

[13] 周楠.基于Cadence软件的高速电路信号完整性仿真[D].昆明:云南大学,2011.

[14] 徐文波,保长先,王健.IBIS模型的信号完整性研究与仿真分析[J].机电工程,2011,28(1):123-126.

[15] 周博远,于立新,褚军舰.IBIS建模和PCB信号完整性分析[J].微电子学与计算机,2010,27(10):111-113.