一种适用于多电源电压IO的阻抗匹配结构

罗尧宇 孙长江 许 迪

(深圳市国微电子有限公司,广东 深圳 518057)

1 引言

为满足片外丰富的电平电压,越来越多的芯片IO接口需要支持多电平标准[1],即IO需满足多电压域电平及不同的IO标准驱动能力。随着芯片工作频率的不断提高,高速环境下的信号反射现象已逐步成为制约信号完整性的关键。为满足这两方面需求,目前主要解决措施是设计一种可配置IOBUF结构,使得输出BUF的阻抗可控,进而满足多电平标准及信号完整性需求。本文首先简要介绍IO输出阻抗匹配原理,进而分析了目前几种可配置IOBUF设计方法,最后设计出一种易于扩展的自动阻抗匹配模块结构及实现电路,并对设计的关键模块进行充分的仿真验证。

2 IO输出阻抗匹配原理

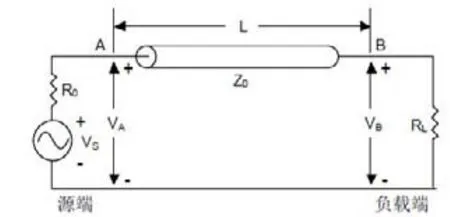

在实际应用中,芯片通过IO接口将内部信号输出到印刷电路板,当两者阻抗不匹配时,输出信号会发生反射,就会引发信号完整性的问题。下面我们以理想传输线模型来分析与信号反射有关的重要问题。图1中,理想传输线L被内阻为R0的信号驱动源VS驱动,传输线的特征阻抗为Z0,负载阻抗为RL。

图1 理想传输线模型

理想的情况是当R0=Z0=RL时,传输线的阻抗是连续的,信号不会发生任何反射,这样传输信号将保持原有状态直到信号源发生改变。如果负载阻抗大于传输线的特性阻抗,那么负载端多余的能量就会反射回源端;如果负载阻抗小于传输线的特性阻抗,负载试图消耗比当前源端提供的能量更多的能量,故通过反射来通知源端输送更多的能量[2]。信号的反射将降低信号质量,严重时其幅值和相位均不能满足IO标准要求。

3 目前流行的可配置IO设计

目前,为适应工艺偏差或兼容多个IO电平标准[3],IO电路设计了多种驱动可调电路,归纳起来主要有三种方式。第一类是固定强度方式,主要为单一电压标准设计。在IO设计时,为适应工艺偏差,除设计主驱动强度外,还设计了弱驱动部分,流片测试后可根据测试情况微调驱动能力。第二类是可配置驱动强度模式,应用于多电压标准。设计IOBUF时,按需要设计了多个驱动强度,然后根据系统配置信号可以改变IO的驱动能力。第三类是阻抗匹配模式,应用于多电压标准。其中极具代表性的是贾艳敏在西安电子科技大学论文中提到的阻抗匹配IO结构,使用DCI数字阻抗匹配网络电路调节阻抗,最终使PAD和外部提供的电阻相匹配[4]。这种设计的主要缺点为配合PMOS和NMOS分开调节,需要较多外围元器件,而且,其自动调节机制电路复杂,当外部阻抗发生变化时,内部调节速率慢。所以难于满足封装成本受限和需要实时自动阻抗匹配的环境。

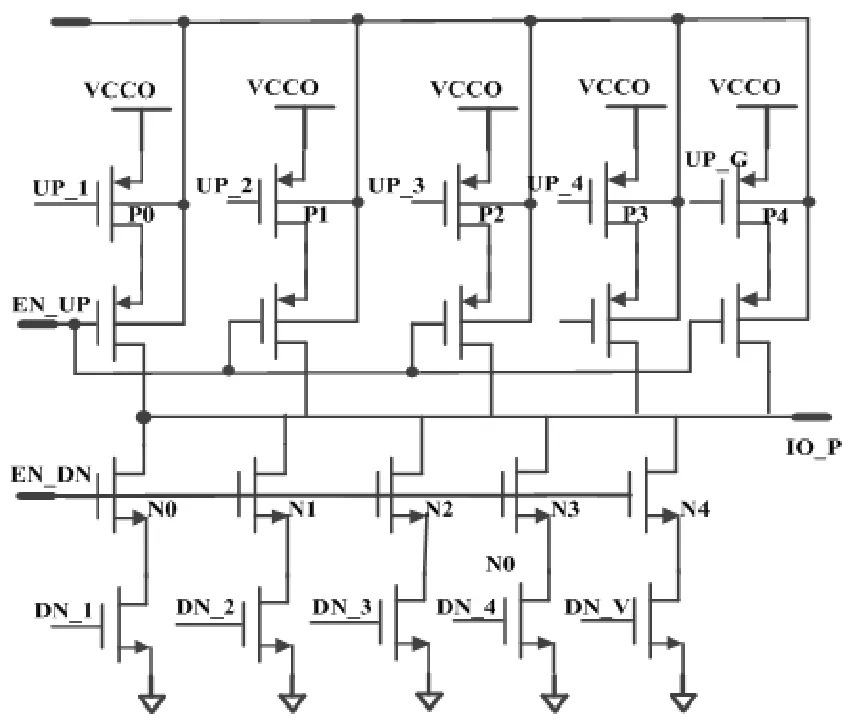

其中可配置IO设计思路如图2所示[5]。在端口配置为输出时,配置使能EN_UP和EN_DN信号有效,然后根据输出的信号值与电平标准打开上拉支路UP_1、UP_2、UP_3、UP_4和下拉支路DN_1、DN_2、DN_3、DN_4,其中UP_G和DN_V是上拉、下拉默认有效值,一般作为输出默认驱动。

图2 可配置强度模式电路

实际设计中,P0、P1、P2、P3、P4 五路上拉PMOS管强度比例可按1∶2∶4∶8∶1,N0、N1、N2、N3、N4 五路下拉NMOS管强度可按 1∶2∶4∶8∶1 设计。这样上拉 PMOS 管与下拉NMOS打开的不同组合,就构成了不同驱动强度。

4 全新片上自动阻抗匹配电路

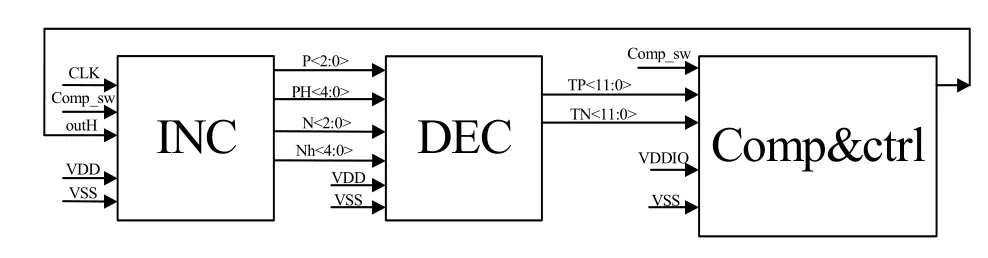

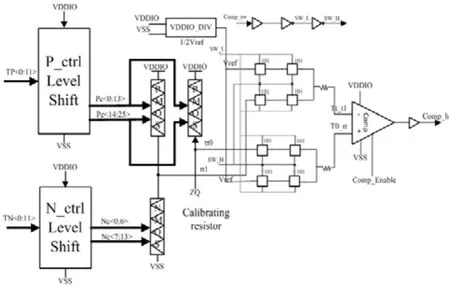

设计可配置自动阻抗匹配电路的方法是:根据用户提供的外部标称电阻和IP内IO镜像BUF电阻比较,经过一定周期调整使得内部BUF阻抗能匹配用户提供的阻抗。为提高精确性和满足高速要求,阻抗匹配系统分粗调和微调电路,通过逐步调整IO镜像BUF驱动使得和用户提供的参考电阻一致,其原理图如图3所示。

图3 自动阻抗匹配模块结构

自动阻抗匹配模块结构分为三部分:第一,Comp&ctrl部分,主要细分成两部分,一是比较源,具体包括粗调和微调的控制的镜像电路、基准电路,其中镜像电路尺寸参考IOBUF设计;其二是比较器部分。第二,INC部分,根据比较器输出的outH信号,实时调节P<7:0>和N<7:0>。第三,DEC电路,主要对INC部分输出信号P<7:0>和N<7:0>进行处理,使之满足Comp&ctrl部分需求,提供控制镜像电路粗调和微调信号。由于INC部分和DEC电路相对简单,以下主要针对Comp&ctrl部分详细的电路介绍和仿真。

4.1 Comp&ctrl模块

Comp&ctrl模块主要实现控制信号的产生和电压的比较,是自动阻抗匹配模块的核心电路。Comp&ctrl模块通过前级DEC模块输出的信号控制PMOS和NMOS,利用MOS电阻属性实现分压,调节MOS宽度来改变阻值大小。通过多次调节,MOS分压逐渐接近片内提供的1/2 IO电源电压,从而达到阻抗匹配目的,其电路结构如图4所示。

图4 Comp&ctrl电路

电路原理:用户根据片外环境设置好标称电阻ZQ后。当Comp_sw为高时,在时钟作用下内核开始阻抗匹配。通过101传输门选择,比较器负端INN连接参考电压Vref,正端t0_tt连接PMOS和标称电阻串接的分压tt0。因为初始PMOS初始状态为全部关断,则PMOS串电阻很高,tt0电压低于Vref,比较器输出Comp_h为低,PMOS模块继续调整而开启,一定周期后,t0_tt电压高于tt_t1电压,比较器输出Comp_h为高,PMOS模块调节结束。当Comp_sw信号为低时,比较器负端tt_t1连接tt1,比较器正端t0_tt接Vref。由于PMOS串前期有调节过,而NMOS初始全部未开启,则tt1电压高于Vref,比较器输出Comp_h输出为低,NMOS继续调节开启,一定周期后,t0_tt电压高于tt_t1电压,比较器输出Comp_h输出为高,NMOS模块调节结束。由于阻抗匹配模块NMOS和PMOS是镜像IO驱动BUF的,自动阻抗匹配模块调节完成也标志着IOBUF驱动调节的完成。下面详细介绍Comp、PMOS、NMOS设计结构。

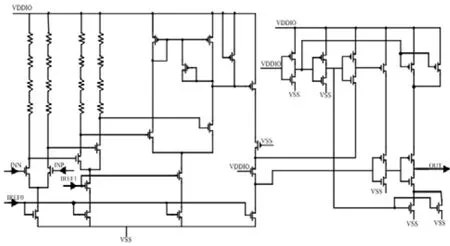

4.1.1 Comp电路

图5 高速Comp电路

因为IP应用于高速环境,比较器Comp电路设计关键在于降低传输延时。Comp实现高速的基本原理是将比较器分成多级级联,每级电路在尽可能小的时延下放大输入信号。从电路看,前两级采用电阻负载的差分放大倍数小,输出信号摆幅逐渐增大到第三、四级时,采用电流镜差分加共源两级运放,实现电压放大,双端输入转成单端输出。一、二级运放注重高带宽,高带宽使信号传输延时较小;对于电流镜差分加共源两级运放,则注重高摆幅和高放大倍数。为了增加输出驱动能力,电路后级还增加了两级INV。以下提供一、二级运放增益和带宽仿真结果。

图6 一二级带宽仿真

图7 Comp整体输入到输出延时

从仿真结果看,一二级低频增益很小,但具有很高的带宽。高速Comp电路从输入到输出的延时是5.68ns,完全满足100MHz以上高速IO设计要求。

4.2PMOS电路

图8PMOS电路

为改善IOBUF驱动能力和减小电源噪声,IOBUF和自动阻抗匹配模块上拉电路分PMOS和NMOS器件,这样当输出为高时,同步打开PMOS电路和漏级接电源的NMOS电路,当输出电压VOH达到VDDIO–Vthn阈值时,NMOS关闭。其中上拉部分电路如下:上图AON为常开上拉电路,在驱动管尺寸设计上,粗调分7级PMOS和NMOS,如上图AO0~AO6,相互尺寸偏差较小,而五级细调AO7~AO11尺寸则有区别,设最小尺寸通电导为1XN,则分别为16XN,8XN,4XN、2XN,1XN。这样在阻抗匹配过程中,先由粗调匹配阻抗进行粗调,在粗调匹配阻抗锁定后,再由细调匹配阻抗精调,这样做的好处就是在当工作环境发生变化时,需要的等效阻抗可能会出现扰动,而系统就可以在一定的范围内进行实时调节,加快了调节速度。

4.3NMOS电路

图9NMOS电路

上图ON为常开NMOS,NO0~NO6为粗调,其他信号控制细调。尺寸方面,NMOS设计方法和PMOS保持一致。由于NMOS多子为电子,电子迁移率为空穴的2~3倍,NMOS尺寸设计较PMOS尺寸小。

5 自动阻抗匹配电路整体仿真

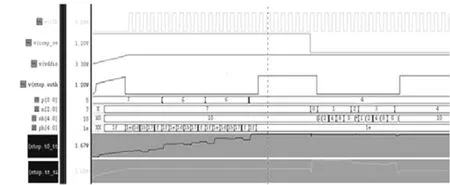

当用户根据芯片应用环境,在ZQ脚连接标称电阻后,自动阻抗匹配模块会根据系统要求自动调整IO阻抗,满足环境阻抗需求。自动阻抗匹配系统调整分两步,仿真也从这两方面着手。以下提供自动阻抗匹配电路整体仿真结果,接下来我们对波形进行详细说明。

图10 自动阻抗匹配电路整体仿真

首先,Comp_sw信号为高,比较器负端连接tt_t1(Vref片内提供的1/2 vddio),正端连接t0_tt(tt0为PMOS和标称电阻串联),从图看,t0_tt电压低于 tt_t1(Vref),输出 Comp_h(在上图为outh)为低。随后INC模块开始调节,粗调P[2:0]逐渐减小,细调PH[4:0]也逐渐变化,DEC模块译码出PMOS控制信号,PMOS逐渐开启,t0_tt逐渐增大,从图看出,当t0_tt电压达到1.67v时,比较器输出Comp_h(在上图为outh)输出翻转为高,PMOS阻抗匹配调节结束。

当Comp_sw信号为低时,比较器负端连接tt_t1(tt1 PMOS和NMOS串联分压),比较器正端接t0_tt(Vref)。从图看出,tt_t1电压较t0_tt高。比较结果Comp_h(在上图为outh)为低。随后INC模块开始调节,随着粗调N[2:0]逐渐增大,细调NH[4:0]也逐渐变化,DEC模块译码控制NMOS控制信号,NMOS控制逐渐开启,tt_t1逐渐减少,从图看出,当tt_t1电压达到1.67v时,输出翻转,NMOS阻抗匹配调节结束。

6 结论

本文提出了一种自动阻抗匹配设计方法,并设计了一种实现电路,该电路能根据用户设置的标称电阻自动实现阻抗匹配,有效解决IO输出驱动能力和阻抗匹配问题。该模块由于采用传输门巧妙选择参考电压和PMOS及NMOS形成的分压,只需要用户设置一个标称电阻,简化了外部电路设计,同时采用一个高速比较器,也减轻了电路和版图设计的难度;采用粗调和细调方式控制PMOS和NMOS模块,调节方法有利于阻抗匹配的实时性,这些都可以成为设计多电平标准IO结构的有益参考。该模块结构简单,可直接集成在芯片IO附近,协助IO克服在高速系统下性能不足的问题,自动实现阻抗匹配和驱动需求,该结构对IO的稳定性和可靠性具有十分积极的意义。

[1]曹小鹏.变压器容量与阻抗电压关系的探讨及其应用[J].中国化工贸易,2012(5):74.

[2]王洪丽.单片机普通I O脚测量电阻与电压[J].牡丹江师范学院学报:自然科学版,2015(4):33-34.

[3]张元吉,赵晋斌,王亚维,等.基于等效内部阻抗的单相电压控制型逆变器控制策略[J].电网技术,2014(2):478-483.