基于FPGA的差分跳频通信关键模块设计与实现*

修 养,蒋 强,冯永新,钱 博

(沈阳理工大学通信与网络工程中心,沈阳 110159)

0 引言

差分跳频(Differential Frequency Hopping,DFH)是一种具有独特数据传输体制的跳频通信技术[1],不同于传统的跳频通信技术,差分跳频信号的下一跳频率是由当前跳频率和当前要发送的信息所决定。它是集编码、调制和跳频为一体的新型跳频通信技术,解决了短波信道下频率资源有限、数据传输速率不高面临的问题[2]。自20世纪90年代美国Lockheed Sander公司成功将DFH技术应用在相关跳频增强型扩频(CHESS)系统以来[3-7],差分跳频技术取得了突破性发展。并在抗多径干扰、抗跟踪干扰、抗截获、抗衰落能力上显示出了非常突出的优势[8]。因此,差分跳频是跳频通信发展的重要方向。

目前针对差分跳频通信,国内外都进行了深入的研究。针对差分跳频信号的产生,有基于m序列、RS码以及m序列和RS码融合的G函数算法[9]。针对差分跳频信号的接收,诸如有频域预加窗的接收方法[5]、基于 STFT 和最大后验概率(MAP)译码算法相结合的跳检测方法[7]、小波脊的时频分析方法[10]。但上述文献的方法无论在信号产生还是信号接收,仅处在理论研究和仿真阶段,文献[11]虽然对差分跳频信号的产生和接收作了逻辑验证,但没有加入无线信道模块,因此,并不能体现出系统的可靠性。

为满足差分跳频通信设备在短波电台上的模块化和结构化应用需求,本文基于软件无线电平台,利用FPGA设计灵活、处理速度快的优点,设计了差分跳频通信关键模块,仿真和平台测试结果表明,设计的模块完成了差分跳频信号的无线收发。基于软件无线电平台的设计,降低了系统的复杂度,且可靠性和精度较高。

1 差分跳频通信机理

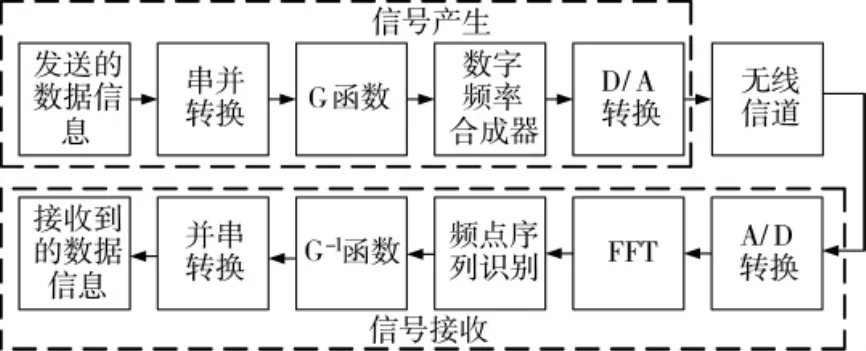

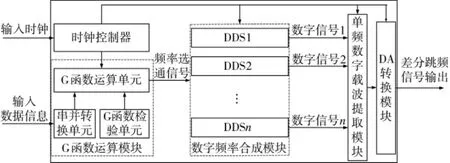

差分跳频通信机理如图1所示,主要包括信号产生和接收两部分。信号产生部分,主要有串并转换模块、G函数映射模块、数字频率合成器模块以及数模转换模块;信号接收部分主要有模数转换模块、傅里叶变换模块、频点序列识别模块、G-1函数解析模块以及并串转换模块。

图1 差分跳频通信机理

与传统跳频不同,差分跳频信号产生的核心归结为G函数的生成。G函数可以看成是一个有向图,其节点代表频率,每个节点分出f=2BPH个分叉,BPH代表每跳传输数据的比特数,f也称为扇出系数[12]。一种G函数频率转移图如图2所示。

图2 G函数频率转移图

常规的G函数表达式可由一个隐式差分方程来表示[13-15],表达式为:

其中,n∈N+,xn∈{0,1}。fn为当前跳频率序号,fn-1为上一跳频率序号,G(·)为频率转移函数。

在信号产生端,若差分跳频信号y(t)的起始频率为f0,要发送的数据序列为X,由式(1)可得差分跳频信号的第n跳频率可表示为[16]:

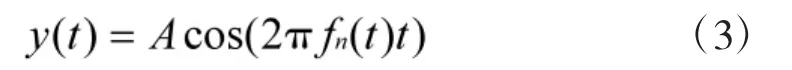

则差分跳频信号表达式为:

其中,A为载波振幅,fn(t)为数据序列为X经过映射后的跳频频率。

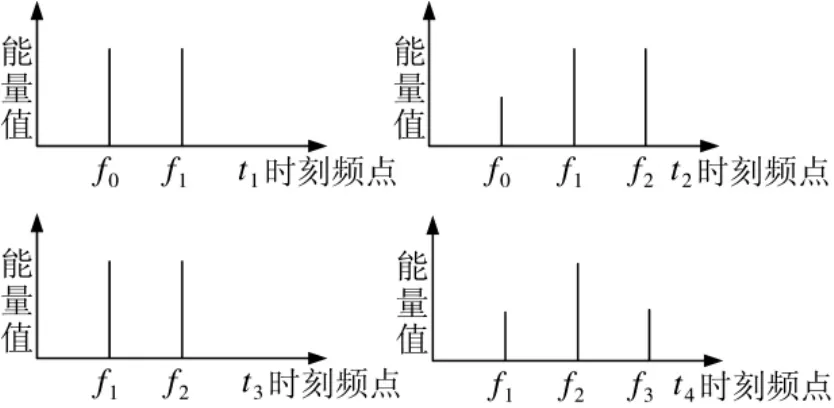

接收端,为了防止频点接收的遗漏,采用基于FFT的宽带接收方法。FFT宽带接收就是在设计的频带内进行数字化宽带扫描,通过FFT分析跳频宽带内的跳频信号特征,进而分析FFT后信号的时频结果,对各采样点序号上FFT后的结果进行阈值判决,得到各频率的频点序号,然后得出当前跳频率序号fn、上一跳频率序号fn-1的关系。差分跳频信号采用FFT宽带接收的时频变换表达式如式(4)所示:

FFT宽带接收采用滑动窗口法,滑动窗口接收机理如图3所示。设定窗口大小为两跳时间,每次滑动半跳时长,随着窗口的滑动,同一频点的能量值先由小到大,再由大到小。

图3 FFT滑动窗口接收机理

2 差分跳频通信关键模块

G函数模块是差分跳频信号产生的核心模块,而频点序列识别模块及G-1函数解析模块是差分跳频信号接收的核心模块。本文主要介绍G函数模块、频点序列识别模块和G-1函数解析模块。

2.1 差分跳频通信发射与接收模块结构

差分跳频信号产生模块如下页图4所示。系统时钟通过FPGA上时钟控制器IP核产生各单元模块所需时钟,输入的数据信息通过串并转换进入G函数运算单元,产生用于选通数字频率合成器输出的控制信号。数字频率合成器经选通输出后,再经过单频数字载波提取单元和数模转换将信号发送出去。

图4 差分跳频信号产生模块

信号接收端,各子模块所需时钟信号由时钟控制器模块提供。接收到的差分跳频信号首先经过模数转换送入FPGA上的FIFO IP核完成数据缓存,然后将缓存后的数据进行FFT变换得到各频点对应的能量值。频点序列识别模块通过对能量值的检测解析出各频点的频率控制字,最后通过G-1函数解析模块和串并转换模块得到发送端所发送的数据信息。差分跳频信号接收模块如图5所示。

图5 差分跳频信号接收模块

2.2 G函数模块设计

G函数模块是对发送的数据信息进行映射编码,产生选通数字频率合成器模块输出的控制信号。本文采用基于同余理论的G函数模型。

定义:差分跳频信号的跳频频点数为M,划分的频率子集数为N(M是N的偶数倍),发送的数据信息序列Xn经过映射后的序列为Yn,当前频率控制字为fn_index,频率控制字偏移量为s,则下一跳的频率控制字fn+1_index可表示为:

2.3 频点序列识别模块设计

频点序列识别模块,是对各频点傅里叶变换后的能量值和设定的阈值进行比较,进而进行频率控制字解析得到各频点的频率控制字序列。

定义:差分跳频信号的跳频点数为n,傅里叶变换的采样点数为m,经过FFT后,各频点对应的能量值为向量:,设定的能量阈值为向量:,输出的采样点序号xk_indek的向量为,频率控制字向量:。

频点序列识别模块的具体设计如下:首先对FFT后输出的采样点序号xk_indek进行搜索。由于频点经过FFT后成镜像对称,所以只需对0到第m/2-1序号进行搜索。当搜索到相应频点对应的序号时,判定该序号下FFT后的能量值是否大于设定的阈值。如果能量值大于设定阈值,则输出频点序号。最后根据所输出的频点序号,解析出相应的频率控制字。频点序列识别模块结构图如图6所示。

图6 频点序列识别模块结构图

2.4 G-1函数解析模块设计

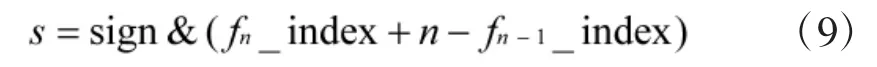

G-1函数解析模块是G函数运算单元的逆运算,由式(6)可知,数据信息被映射成频率控制字偏移量s,因此,只要解析出s,就能正确接收到发送信息。由式(2)可得G-1函数数学表达式可表示为:

定义:前一跳的频率控制字为fn-1_index,当前跳频率控制字为fn_index,频率偏移量为s,sign和n_sign代表符号位,分别表示当前跳和上一跳频率控制字的差值为正数时补0、为负数时补1,bu_0代表补位符号0。

在每跳传输两比特信息的条件下,设计的n跳G-1函数解析模块算法步骤如下:

步骤1:判断fn_index是否大于fn-1_index,如果成立则执行步骤2,否则执行步骤3;

步骤2:判断fn_index≥n-3与fn_index≤2是否同时成立,如果同时成立则s可表示为:

此时称s为下溢出。否则s可表示为:

此时称s未溢出。

步骤3:判断fn-1_index≥n-3与fn_index≤2是否同时成立,如果同时成立则s可表示为:

此时称s上溢出。否则s可表示为:

步骤4:根据解析到的s获得实际发送的数据信息:

3 仿真与测试结果分析

在核心模块设计的基础上,基于软件无线电平台对差分跳频信号的产生和接收进行仿真与平台测试分析。设计的具体参数如下:系统跳速为5000跳/s,工作波段为5 MHz~7.4 MHz,每跳传输信息两比特,跳频频点数为16,频点间隔0.16 MHz,FFT采样点数为1 024,采样频率fs=100 MHz,发送的串行数据为1101001001101000。经过大量的仿真与测试分析,为了保证通信系统的可靠性,对4个频点值进行了替换,具体频点值和频率控制字如表1所示:

表1 16频点跳频频率与频率控制字对照表

3.1 仿真结果分析

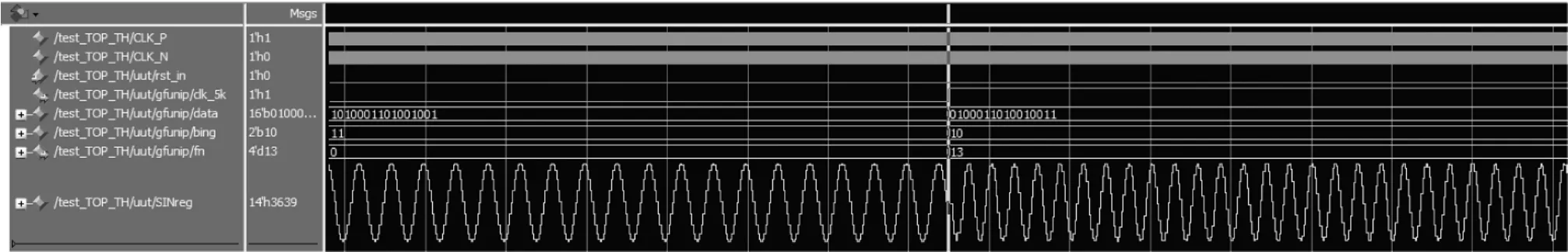

在ISE开发环境下,使用Verilog语言,调用第三方仿真工具Modelsim,对差分跳频信号产生和接收进行仿真分析。16频点差分跳频信号产生和接收仿真图如图7和图8所示:

图7 16频点差分跳频信号相邻两跳仿真图

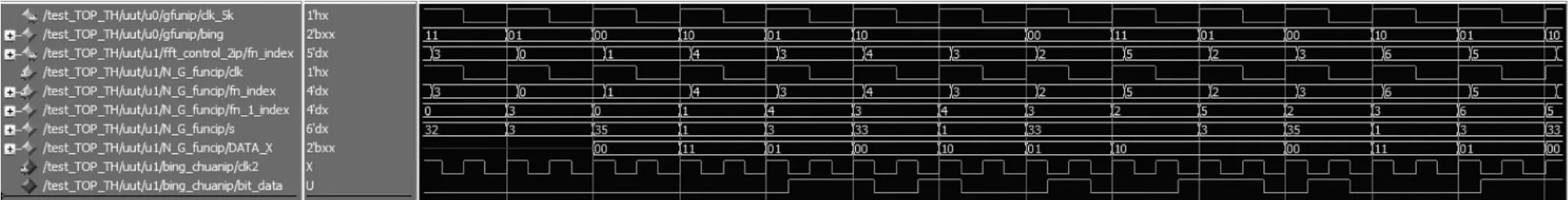

图8 16频点差分跳频信号接收仿真图

由图7可知,相邻信号的频率发生了明显跳变,验证信号产生模块设计的正确性。由图8可知,频点序列识别模块正确解析出频率控制字,G-1函数解析模块正常工作,完成了频率控制字偏移量s的解析。通过对比可以发现,解析出来的数据DATA_X与发送端串并转换后的数据bing是一致的,最终通过并串转换模块得到发送的数据信息bit_data。

3.2 测试结果分析

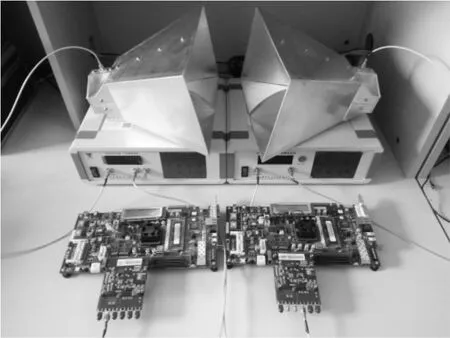

基于软件无线电平台采用XILINX公司的Virtex6系列XC6VLX240T芯片,使用两块ML605开发板、一台上变频发射机、一台下变频接收机、一对天线和两块高速AD/DA子卡,对差分跳频信号产生和接收模块进行无线信道上的测试分析。ML605开发板上变频发射机、下变频接收机、天线和高速AD/DA子卡硬件实物图如图9所示。在无线信道下对16频点差分跳频信号产生和接收测试图如下页图10和图11所示。

图9 硬件实物图

图10 16频点差分跳频信号产生板级测试图

图11 16频点差分跳频信号接收片上分析图

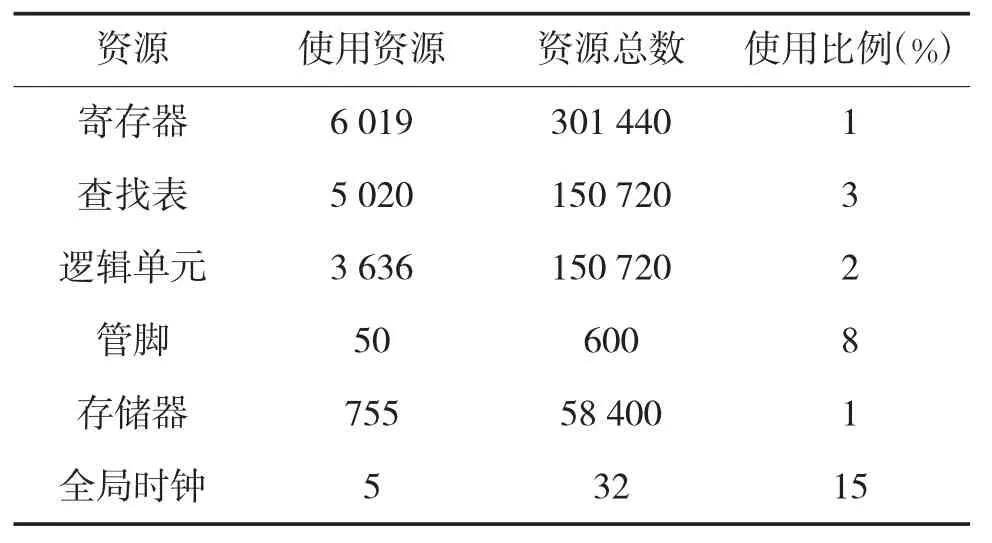

由图10可知,上半部分是差分跳频信号的时域波形,下半部分为频域波形。由于示波器缓冲区限制,因此,无法捕捉到差分跳频信号在时域上相邻两跳频点跳变波形。但通过对频域分析可以发现,所产生信号的频点和设定频点一致,主瓣峰值比旁瓣峰值高出了近20 dB,远远超出了3 dB的最低标准。通过对图10分析,所设计的模块完成了差分跳频信号的产生,且信号产生效果良好。由图11可知,由于片上逻辑分析仪是对片上信号的实时抓取,所以使用Chipscope得到的是某一时刻刷新数据。通过对图11中前一跳频率控制字fn-1_index、后一跳频率控制字fn_index和频点偏移量s分析可知,所接收到的数据是正确的。综合信号产生和接收测试结果,设计的差分跳频通信关键模块能实现差分跳频信号在无线信道上的无线收发,验证了设计模块的可靠性和精确性。基于FPGA的16频点差分跳频通信关键模块所使用的逻辑资源对照表如表2所示。

表2 FPGA逻辑资源使用对照表

3.3 系统整体性能及误码率分析

基于软件无线电平台,将接收到的信号在MATALB仿真环境下对系统的整体性能和误码率进行分析。在所设定参数下,通过大量测试,基于软件无线电平台的单跳时间内信号能量值在420~500之间,设定320为能量判决阈值。得到的单跳时间内不同信噪比(SNR)下信号能量和噪声能量值如下页图12所示,不同SNR下误码率性能如图13所示。

由图12可知,在设定参数下,信噪比不低于4dB时,单跳时间内的噪声能量没有超过所设阈值,因此,所设计的模块能接收到发射端所发送的数据。由图13可知,在100次的测试条件下,误码率随着SNR的增大而减小,在SNR增加到6 dB时,误码率减小到0,系统能准确接收到发送端数据,与文献[11]相比,设计的模块完成了差分跳频信号在无线信道下的收发。验证了设计的模块在无线信道下可靠性和精确性。

图12 单跳时间内不同SNR下信号能量和噪声能量值

图13 单跳时间内不同SNR下误码率

4 结论

本文基于软件无线电平台,利用FPGA设计灵活、处理速度快的优点,设计了差分跳频通信关键模块,仿真和软件无线电平台测试结果表明,所设计的模块在无线信道下可靠性和精度较高,为差分跳频技术在短波电台上模块化和结构化应用需求提供了技术支撑。

[1]钱博,冯永新,潘成胜,等.一种基于多跳自相关的差分跳频信号检测方法[J].航空学报,2011,32(12):2268-2276.

[2]王胜涛,郝二伟,杜广超.CHESS电台抗干扰性能仿真分析[J].兵工自动化,2015,34(1):1-3.

[3]张毅,姚富强.基于混沌映射的差分跳频频率编码[J].电讯技术,2013,53(3):265-268.

[4]王胜涛,黄文晶,张劲心,等.差分跳频信号抗多音干扰性能仿真分析[J].无线电工程,2013,43(12):29-31.

[5]蔡昆宏,赵利,黄昌龙.基于频域预加窗的差分跳频接收机设计与实现[J].计算机工程与设计,2012,33(11):4076-4080.

[6]KUMAR A,SINGH G K,AN R S.An improved closed from design method for the cosine modulated filter banks using windowing technigue[J].Applied Soft Computing,2011,11(3):3209-3217.

[7]YAN L S,YE J,JIANG H Y.A photonic comb filter with independently and digitally tunable bandwidth and frequency spacing [J].Photonics Technology Letters,IEEE,2011,23(13):857-859.

[8]熊俊俏.STFT算法在短波差分跳频信号检测中的应用[J].电讯技术,2010,50(8):52-56.

[9]冯永新,徐美荣,钱博,等.一种差分跳频频率转移函数算法[J].航空学报,2013,34(3):655-661.

[10]王明海,苟彦新,田岩.一种基于小波脊时频分析的差分跳频信号检测方法[J].电讯技术,2008,48(3):86-90.

[11]黄玉.差分跳频通信系统的研究与FPGA实现[D].大连:大连海事大学,2014.

[12]朱秀林,胡用时,于奇.差分跳频系统的G函数算法研究[J].计算机与数字工程,2005,33(8):46-48.

[13]刘海燕,周彬,别玉霞.差分跳频接收机信号抗干扰性能研究[J].计算机仿真,2015,32(10):210-214.

[14]周志强,李少谦,程郁凡.差分跳频噪声归一化接收机性能分析[J].电子技术应用,2011,37(1):87-90.

[15]董彬虹,李少谦,史锋旗.一种差分跳频码发生器的构造方法[J].电子与信息学报,2010,32(4):816-820.

[16]廖连贵,赵利,崔杨.基于FPGA的差分跳频信号处理器的设计与实现[J].计算机工程与设计,2011,32(8):2643-2647.