基于宇航用译码器开关时间特性研究

刘 辉 韩晓东 张皓源 王 喆

(中国航天宇航元器件工程中心,北京 100029)

基于宇航用译码器开关时间特性研究

刘 辉 韩晓东 张皓源 王 喆

(中国航天宇航元器件工程中心,北京 100029)

宇航用译码器在满足其基本译码功能正常的基础上,在复杂电气环境使用中,译码器要保证其开关时间参数传输延迟时间及输出转换时间满足使用要求。在复杂电气环境条件下即不同负载以及不同输入电压情况下,对器件各输出引脚的开关时间参数进行了测试,测试结果表明被测试器件传输延迟时间最大值为2.1214μs,输出高低电平转换时间最大值分别为1.6769μs与8.1214μs,被验证器件的开关时间特性参数随输入电压的增加而减小,随负载电容的变大而延长。该开关时间特性的研究为产品设计在复杂电气环境条件下对器件的使用,提供有效的趋势判断与数据支撑。

译码器 传输 延迟 输出 开关时间

1 引 言

由于卫星产品对于高可靠国产元器件的需求不断增加,国产元器件的功能性能能否满足宇航复杂电气环境使用条件,成为国产元器件是否被宇航卫星产品应用的关键[1,2]。目前随着自主可控国产化元器件应用验证项目的实施,大量国产CMOS逻辑电路只有通过应用验证,才能便于设计师选用,而译码器作为产品大量使用的关键器件,主要用于离散指令的上注与发送,针对该器件在应用时满足其基本译码功能正常的基础上,对于离散指令的传输时间要求同样重要。

针对研制的4-16线译码器在鉴定级试验,只在一种输入电压10V以及50pF的单一试验条件下,进行器件开关时间参数测试的局限,基于器件输入电压范围宽(3V~15V)、容性负载使用多样化的特点,在器件典型输入电压10V的基础上,进一步扩展器件板级试验条件,采用2.7V,10V以及16.5V输入电压,在相应输入电压下,分别采用50pF,220pF,470pF以及1000pF负载电容,对器件各输出引脚的开关时间参数进行了测试,被测试器件开关时间参数随着电压的升高不断减小,随着负载电容的增加不断增大,通过不同负载以及器件不同输入电压复杂电气环境测试条件的组合测试,达到充分检验器件在不同使用条件下开关时间参数(tPLH≤3μs,tTHL≤10μs,tTLH≤10μs)是否符合使用要求的目的,进而避免器件在卫星等产品中的使用风险。

2 器件信息

半导体集成电路XXXX是一款4-16线译码器,器件采用0.5μm三层金属的硅栅高压(18V)CMOS工艺,全定制设计,无SRAM 结构,芯片尺寸2.582mm×2.131mm。DIP24封装器件的外壳内腔体积(60.45±10)mm3。采用银浆导电胶装片,硅铝丝键合,采用熔封封帽工艺,器件盖板面积为157mm2,引线材料和镀涂按GJB597A-1996中3.5.6的规定。引线材料采用柯伐,涂覆采用镀镍镀金,外层镀金层厚度1.27μm~3.5μm,该器件在输入电压10V且外接电容负载50pF情况下,传输延迟时间(tPLH)要求不大于3μs,输出转换器件要求不大于10μs。

该器件是一款防单点失效、带驱动器、无锁存的抗辐照4-16线译码器,主要由双冗余译码和双冗余输出驱动电路组成,双冗余译码器采用通用典型的译码结构形式、输出驱动电路采用2串2并4个PMOS晶体管冗余设计结构,器件最大输入电源电压范围-0.5V~18V,推荐输入电源电压范围3V~15V,具有较宽的电压输入范围,器件功能框图如图1所示。

3 开关时间参数测试方法

译码器的开关时间参数主要包括输入到输出端的传输延迟时间以及输出端从高电平转换到低电平(或低电平到高电平)的转换时间。其中基于传输延迟的测量方法主要有基于网络分析仪、基于矢量信号分析仪、基于相位计以及基于示波器的时延测量方法,通过以上传输延迟方法研究[3~7],采用示波器测试方法对译码器的开关时间参数传输延迟时间以及输出转换时间进行测量。

由于宽带存储示波器具有高速采集并储存的能力,因此可以通过示波器来测试不同通道间的延迟时间以及单一通道的高低电平转换时间。采用示波器测量延迟时间的原理是:将同一激励信号分成两路信号,一路直接连接到示波器通道上,一路经过被测器件连接到示波器的另一通道上,利用示波器测量这两个通道的通道延迟时间,测试原理波形如图2所示,其中延时时间Δt=t1-t2。采用示波器测量输出高低电平转换时间的测试原理是:通过器件输入端的激励信号,采用一路示波器,在被测器件的输出端测量器件的高电平转换到低电平(或低电平到高电平)的转换时间,测量原理波形如图3所示。

在器件延迟时间测试中,以输入信号与输出信号的时间差值Δt=t1-t2作为器件的传输延迟时间,如图2所示延迟时间测量原理波形,在测试中采用双通道示波器,当器件处于使能状态并执行译码切换指令时,对器件的译码指令输入引脚以及输出引脚的响应时间进行测量,给出器件的传输延迟时间;在电平转换时间测试中,以电平变化起始的起始时间到输出电平稳定的时间差值称为被测器件的电平转换时间,如图3所示的输出转换时间测量原理图,在测试中采用一路示波器,当器件执行译码切换指令时,在器件输出端对器件的输出转换时间进行测量。

4 硬件试验系统

针对研制的4-16线译码器硬件系统试验装置通过“上位机”+“被验证器件验证板”+“被验证器件控制板”的形式组成。该被验证器件测试硬件系统装置如图4所示。其中,被验证器件测试板分为测试底板与测试子板,测试底板和子板采用扣卡板的结构形式,底层为底板,为试验验证系统的主体部分;顶层为被验器件板,为实际被测部分。器件验证子板上,分别通过50pF,220pF,470pF以及1 000pF负载电容插槽与被测器件相连,设置不同的负载档验证器件的带负载能力,通过ARM微控制器对器件输入电压进行调整,验证器件在不同输入电压条件下(2.7V,10V,16.5V)以及不同负载条件下,器件的功能性能以及开关时间参数是否满足使用要求。

其中被测器件在整个系统中的结构如图5所示。此系统结构充分依据型号典型译码器设计线路,采用ARM控制器通过串口对100万门FPGA进行发送译码控制指令,FPGA将译码值通过74LVC164245电平变换电路输出至被验证器件的高电压变换电路,此时,被验证器件直接获取译码输入值,在获取译码值后将码值输出至低压变换电路,FPGA以50MHz的采样时钟对译码器输出译码信号进行采样,并将采样值返回上位机。为实现器件不同输入电压下的测试,电路设计中采用ARM控制器,通过串口控制数字电位器,通过数字电位器的电压切换实现不同电压输入的控制,实现电源电压的拉偏,并在不同输入电压条件下,应用高频率数字示波器在器件不同输出负载情况下对开关时间参数(输入到输出端的传输延迟时间、输出端从高电平转换到低电平转换时间、输出端从低电平转换到高电平转换时间)进行测试。采用ARM控制器以及数字电位器的切换方式解决不同输入电压(2.7V,10V,16.5V)以及不同负载情况下(50pF,200pF,470pF,1 000pF)同时分别测试的难题,大大提高了测试效率,解决器件鉴定级单一测试应力不充分等问题。

5 试验数据及结果

针对该4-16线译码器开关时间测试,在器件电源输入端,分别加以2.7V,10V以及16.5V输入电压,在相应输入电压下,分别采用1 000pF,470pF,220pF以及50pF负载电容,测量器件每一个输出引脚的传输延迟时间、输出端从高电平转换到低电平转换时间、输出端从低电平转换到高电平转换时间。

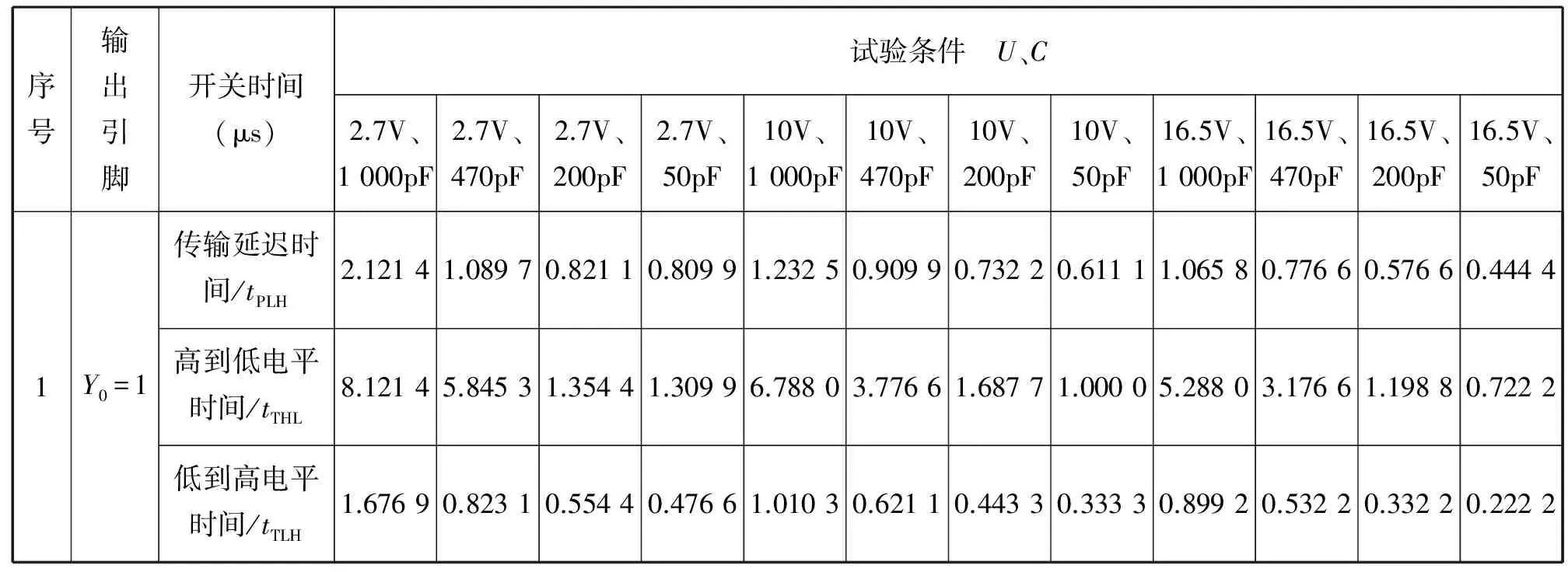

在试验过程中对器件的输入电压2.7V、10V以及16.5V分别进行了校准,使器件输入电压VDD分别为2.700V,10.000V以及16.500V,满足使用要求,对于被验证器件的开关时间测试,采用示波器探头直接与器件引脚根部相连的方式,消除器件因板间长线传输延时产生的误差。测试数据结果如表1所示,表1中以Y0引脚为例给出试验结果。依据表1可以看出,Y0引脚传输延迟时间(tPLH)最大值为2.121 4μs,输出端从高电平转换到低电平转换时间(tTHL)最大值为8.121 4μs,输出端从低电平转换到高电平转换时间(tTLH)最大值为1.676 9μs,测试结果表明被测试器件测试延迟时间、高电平转换到低电平转换时间、低电平转换到高电平转换时间均满足使用手册要求,延迟时间最大值没有超过3μs,高电平转换到低电平转换时间以及低电平转换到高电平转换时间最大值均没有超过10μs。

依据表1测试试验结果,可以发现器件各输出引脚的传输延迟时间、高电平转换到低电平转换时间、低电平转换到高电平转换时间均随着电压的升高而不断减小,随着负载电容的增加不断增大。图6中以Y0引脚在2.7V输入电压下为例,给出开关时间参数随不同负载的变化曲线,从曲线中可以得出各开关时间参数随负载电容的增大不断增大。图7中给出Y0引脚负载电容1 000pF情况下,开关时间参数随输入电压的变化曲线,从曲线中可以得出各开关时间参数随输入电压的增大而不断减小,其余引脚的变换趋势与Y0引脚一致。

序号输出引脚开关时间(μs)试验条件 U、C2.7V、1000pF2.7V、470pF2.7V、200pF2.7V、50pF10V、1000pF10V、470pF10V、200pF10V、50pF16.5V、1000pF16.5V、470pF16.5V、200pF16.5V、50pF1Y0=1传输延迟时间/tPLH2.12141.08970.82110.80991.23250.90990.73220.61111.06580.77660.57660.4444高到低电平时间/tTHL8.12145.84531.35441.30996.78803.77661.68771.00005.28803.17661.19880.7222低到高电平时间/tTLH1.67690.82310.55440.47661.01030.62110.44330.33330.89920.53220.33220.2222

6 结束语

充分依据产品对器件不同电压以及不同负载的使用情况,进一步扩展器件鉴定级单一开关时间测试条件,充分验证器件在不同负载情况下,器件的带负载能力。对研制的4-16线译码器在不同输入电压以及不同负载电容条件下进行了开关时间参数测试,被测试器件开关时间参数随着电压的升高不断减小,随着负载电容的增加不断增大,通过对不同负载以及器件不同输入电压复杂电气环境测试条件的组合测试,验证器件开关时间参数是否符合使用要求,进而避免器件在产品中的使用风险。

[1] 肖虹,蔡少英,刘涌.国外塑封微电路的可靠性研究进展[J].电子产品可靠性与环境试验, 2006,12(7):22~25.

[2] 张安康.微电子器件与电路可靠性[M].北京:电子工业出版社,1994:11~12.

[3] 黄凯冬.利用矢量网络分析仪测量时延特性的方法[J].电讯技术,2007,47(01):193~195.

[4] 李建宇.双通道矢量信号分析仪测试系统延迟特性[J].电子设计应用,2006,1(06):95~97.

[5] 尹仲琪.时延测量方法的分析与比较[J].电讯技术,2006,46(06):213~216.

[6] 李德儒. 群时延测量技术[M]. 北京:电子工业出版社,1990:180~182.

[7] Hyland B.Using time domain reflectometer to measure the transmission delay[J].Electronic Technology Application,2010,23(6):107~110.

ResearchofSwitchingTimeCharacteristicsBasedonAerospace-usedDecoders

LIU Hui HAN Xiao-dong ZHANG Hao-yuan WANG Zhe

(China Aerospace Components Engineering Center, Beijing 100029,China)

Aerospace-used decoders need to guarantee not only the basic decoding function, but also the switching time characteristics including transmission delay and output switching time to meet the application requirement in the complex electrical environment. The the switching time parameters of every output pin in cases of different output loads and input voltages are tested. The test result shows that the max transmission delay of the decoder is 2.1214μs, the max output transmission time from high voltage to low voltage is 1.6769μs and the one from low voltage to high voltage is 8.1214μs. The switching time characteristic parameters decrease with the input voltage increased, and increase with larger load capacitance.This research provided an effective trend judgment and data support for design in a complex electromagnetic environment conditions.

Decoder Transmission Delay Output Switching time

2016-11-18,

2017-03-20

刘辉(1982-),男,博士,工程师,主要研究方向:航天器用元器件应用验证。

1000-7202(2017) 04-0071-05

10.12060/j.issn.1000-7202.2017.04.15

TN764

A