LDO芯片CP通用测试方法研究

唐彩彬,张凯虹

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

LDO芯片CP通用测试方法研究

唐彩彬,张凯虹

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

介绍了LDO(线性稳压器)的通用测试方法。基于长川CTA8280测试系统,通过对芯片CP(圆测试)要求进行分析,设计了某款LDO芯片的测试外围,实现了对该LDO芯片功能与性能的测试。该方案能够作为通用测试方法供LDO芯片测试设计参考。

LDO;CTA8280;CP;熔丝

1 引言

DC/DC变换器已广泛应用于各种移动电子系统中,如便携式电脑、移动通信终端、PDA等。而LDO(Low Drop Out)线性稳压器由于具有结构简单、成本低廉、低噪声、低功耗及占用芯片面积较小等众多优点,广泛应用于便携式电子产品中。

近年来,LDO芯片在晶圆测试环节多需要通过熔丝修调使其达到统一的输出电压,因此,CP测试作为集成电路产业中的必备环节显得格外重要。目前,LDO芯片已经进入了大规模生产阶段,这需要依赖ATE(Automatic TestEquipment)设备进行量产化测试。

本文针对国内某款LDO芯片,基于ATE、全自动探针台、专用探针卡,搭建了一套完整的Wafer测试平台。该测试方案实现了该芯片晶圆基准电压的调整,并为LDO类芯片的功能与性能提供了一种通用的测试方法。

2 LDO的结构与工作原理

LDO稳压器的工作原理是通过一个压控电流源以强制在稳压器输出端上产生一个固定电压,内部控制电路连续检测(监视)输出电压,并根据负载的需求调节电流源以把输出电压保持在期望的数值[1]。电流源的设计极限限定了稳压器在仍然保持电压调节作用的情况下所能供应的最大负载电流。输出电压采用一个反馈环路进行控制,其需要某种类型的补偿以确保环路稳定性。大多数线性稳压器都具有内置补偿功能电路,无需外部组件就能保持完全稳定。某些稳压器(比如低压降型)则需要在输出引脚和地之间连接一些外部电容以确保稳压器的稳定性。

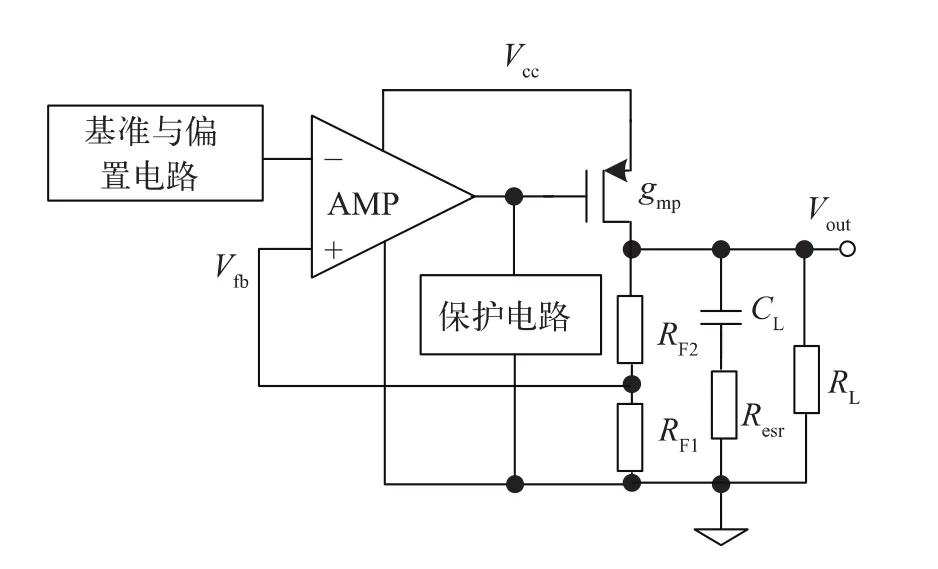

基本的LDO线性稳压器包括误差放大器、调整元件、基准与偏置电路以及反馈比例电阻网络,再加上诸如过温、限流、电池极性反转等保护电路就构成了一个完整的LDO系统[2],图1为PMOS型LDO稳压器结构图。基准偏置模块用来产生一个稳定性很高的参考电压,它为误差放大器、电路内部比较器等提供电压偏置,并且对LDO稳压器输出高精度的直流电压起着十分重要的作用。未调节的输入电压作为供电电源电压,基准电压作为误差放大器的负相输入电压,电阻反馈网络将输出电压进行分压并得到反馈电压,此反馈电压输入到误差比较器的同相端,与负相端的基准电压进行比较。两电压差值通过误差放大器的放大后直接控制功率调整元件的栅极,通过改变调整元件的导通状态来控制LDO的输出端,从而获得稳定的输出电压值。

图1 PMOS型LDO稳压器结构图

3 LDO的基本性能指标

3.1 输出电压与输出精度

输出电压是LDO线性稳压器的重要参数,也是电子设备设计者选用LDO时首先应考虑的参数。按输出电压值可分为固定输出电压和可调输出电压两种类型。一般固定输出电压LDO线性稳压器是经过设计厂商精密调整,输出电压精度也很高。但由于固定输出电压数值均为常用电压值,不可能满足所有的应用要求,因此也可以外接反馈比例电阻,通过调节外接电阻阻值获得需要的输出电压。

3.2 漏失电压与静态电流

漏失电压定义为保证LDO线性稳压器正常工作时对应的输入输出电压间的最小电压差。它是反映调整管调节输出电压能力的一个重要参数。

LDO线性稳压器的静态电流又叫接地电流,定义为芯片不加负载时、电路正常工作时内部消耗的电流,它等于输入电流与输出电流之差。

3.3 功耗与效率

LDO线性稳压器的效率与漏失电压和静态电流有关,低漏失电压、小静态电流则意味着LDO电路具有低功耗、高效率的特点。

3.4 负载调整率与线性调整率

负载调整率表征了LDO输出负载大小变化对输出电压的影响程度,表征了负载变化而稳压器维持输出在标称值上的能力,负载调整率越小越好。

线性调整率表征了LDO输入电压大小变化对输出电压的影响程度,定义为负载一定时稳压电路输出电压相对变化量与其输入电压相对变化量之比。与负载调整率一样,该指标也是越小越好[3]。

4 LDO测试方案设计与实现

4.1 测试外围设计

本文针对某款标准电压为5 V的LDO线性稳压器来设计测试外围,该LDO芯片主要有常规PAD(IN、OUT、GND)与熔丝 PAD(T1、T2、T3、T4、T5、T6)。

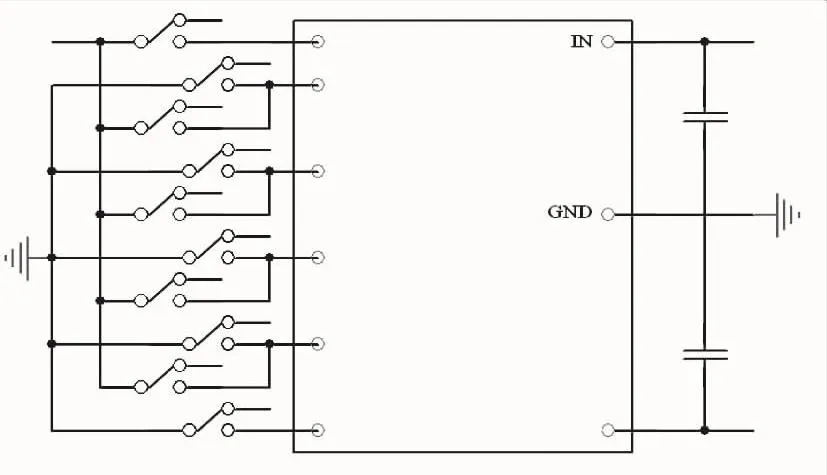

以单芯片测试方案为例,根据datasheet上的相应参数的测试条件设计测试电路,如图2所示。该芯片总计5段PAD之间的熔丝,分别为T1~T2、T2~T3、T3~T4、T4~T5、T5~T6,需 5 个继电器来控制这 5 段熔丝。使用长川科技CTA8280测试系统来实现该设计,单芯片测试方案总计需要3路电流电压源,分别为DVI0(IN 端)、DVI1(Trim)、QVI0(OUT 端),IN 与OUT需要分别加0.1 μF电容用于稳定输入与输出。

图2 测试电路外围

4.2 测试项目实现

4.2.1 输出电压测试与熔丝修调(Trim测试)

当IN输入电压与OUT输出电流保持不变时,在OUT端测得的电压即为输出电压Vref。程序如下:

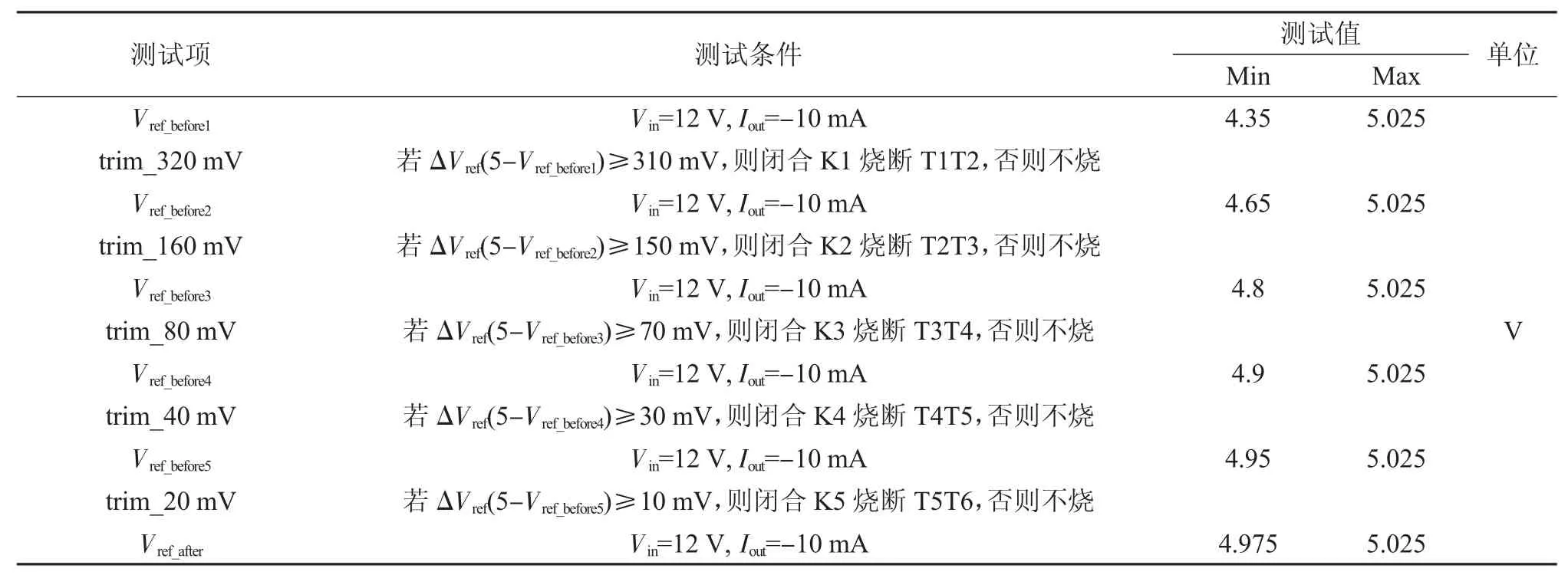

表1 输出电压测试与熔丝修调(修调测试)

DVI_SetMode(CH0,FV,VRang_20 V,IRang_200 mA,200,-200);

QVI_SetMode(CH0,FI,IRang_100 mA,VRang_10 V,10);

DelaymS(3);

DVI_SetOutVal(CH0,12);

QVI_SetOutVal(CH0,-10);

DelaymS(20);

QVI_MeasureV(CH0);

该LDO需要通过熔丝修调使其达到5 V标准,测试要求输出精度为±25 mV。熔丝修调时,根据烧熔丝前输出电压值Vref_bef来选择烧断相应的熔丝以达到期望的变化,烧熔丝Trim power电压设置为5 V。以T5T6段为例,程序如下:

CBIT_SRelayOn(5,-1);

DVI_SetMode (CH1,FV,VRang_10V,IRang_500 mA,500,-500);

DelaymS(3);

DVI_SetOutVal(CH1,Trimpower);DelaymS(10);

4.2.2 静态电流Iq测试

表2 Iq测试

芯片外围不接任何负载的情况下,测试IN与OUT电流之差即为静态电流Iq,以IN端7 V输入电压为例,测试程序如下:

DVI_SetMode(CH0,FV,VRang_50 V,IRang_1 mA,1,-1);

QVI_SetMode(CH0,FI,IRang_1 uA,VRang_10 V,10);

DelaymS(3);

DVI_SetOutVal(CH0,7);QVI_SetOutVal(CH0,0);DelaymS(20);

DVI_MeasureIRS(CH0,0.02,3);4.2.3 LNR与LDR测试

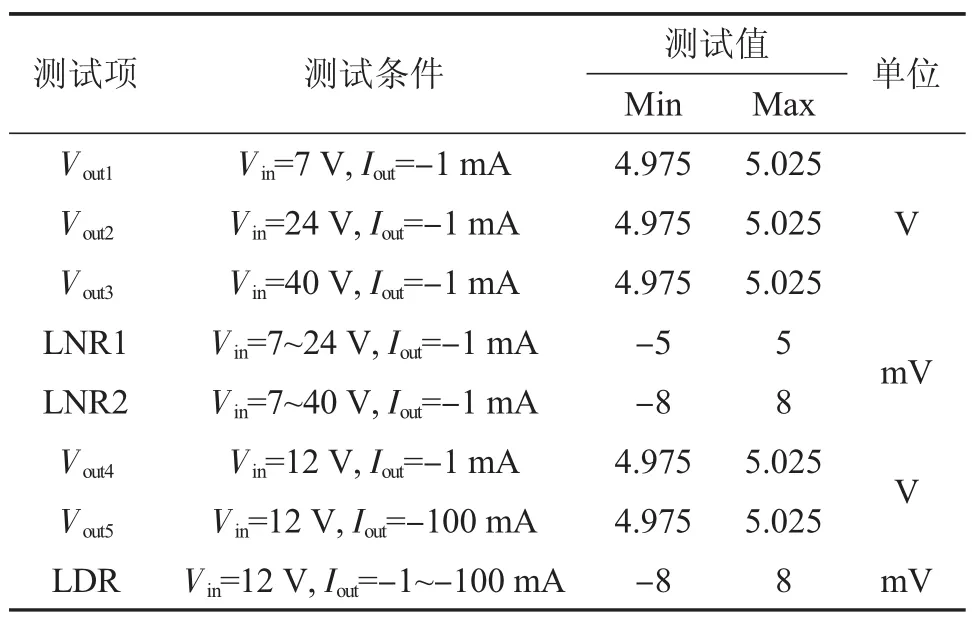

表3 LNR与LDR测试

改变输入电压和负载电流,通过计算对比数据得到线性调整率。输入电压线性调整率LNR1=Vout2-Vout1,负载电流线性调整率LNR2=Vout3-Vout1,测试程序在第一项测试基础上做简单修改。

4.2.4 Vdrop测试

表4 Vdrop测试

正常输入电压、一定的负载下,输出电压为Vout。不断地降低输入电压Vin,直到输出电压等于或接近98%Vout时,记录此时的输入电压,那么此时的Vdropout=Vin-98%Vout;不断地改变负载电流,依次而行,就可得到不同输出电流时的dropout voltage。本例中通过计算Drop1(Vdrop1/Vout4)与Drop2(Vdrop1/Vout5)来得到漏失电压,测试程序参考第一项测试。

4.3 测试结果

4.3.1 熔丝修调结果

熔丝修调前LDO芯片的基准电压分布如图3所示,可见,输出电压Vout值多集中在4.6~4.9 V之间,需要通过修调将该电压上调使其达到5 V的标准。

图3 Vref测试值分布图(修调前)

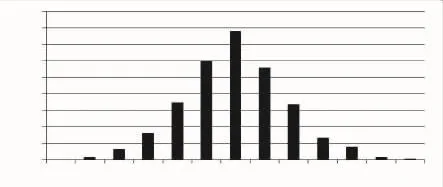

5段熔丝的理论变化值分别为320 mV、160 mV、80 mV、40 mV、20 mV,熔丝均设计成调高电压。修调测试时,根据Vout初始值来判断并烧断相应的熔丝,从最大的一段熔丝开始判断,每烧完一段熔丝后重新测试Vout值并判断是否要烧断下一段熔丝,直到烧完最小的20 mV熔丝。熔丝修调后LDO基准电压值分布如图4所示,以5 V为中心点呈现很好的正态分布。

图4 Vref测试值分布图(修调后)

4.3.2 晶圆测试结果

该LDO芯片晶圆为8寸片,总管芯数32000颗左右,测试map如图5所示。由于流片工艺限制,该晶圆熔丝实际变化值与理论值存在偏差,晶圆测试主要失效项为输出电压失效,测试良率在97%左右。圆片封装后验证成品,良率为99%,良率正常。

图5 晶圆测试Map图

5 结束语

本文从LDO稳压器晶圆测试角度出发进行了测试外围电路的设计。该方案通过Trim模块实现了对LDO芯片输出基准电压的修调,根据LDO的基本性能指标与该款LDO的datasheet进行了输出电压、静态电流、负载调整率、线性调整率、漏失电压等参数的测试,可用作熔丝修调以及LDO芯片测试的参考。

[1]吴晓波,李凯,严晓浪.高性能低压差性稳压器的研究与设计[J].微电子学,2006,36(3):347-351.

[2]陈东坡,何乐年,严晓浪.一种低静态电流、高稳定的LDO线性稳压器[J].电子与信息学报,2004,28(8):1526-1529.

[3]Goodenough F.Low dropout linear regulators[J].Electronic Design,1998,5(13):65-77.

唐彩彬(1990—),男,江苏泰州人,硕士研究生,毕业于江南大学集成电路工程专业,现在中国电子科技集团公司第五十八研究所从事集成电路测试研发工作。

Research on General CP Test Method of LDO Chip

TANG Caibin,ZHANG Kaihong

(China Electronics Technology Corporation No.58 Research Institute,Wuxi 214035,China)

Introduced a general test method of LDO(Low Drop Out)Circuit Probingtest.In the paper,based on the CTA8280 test system,by analyzing the requirements of LDO wafer test,the chip peripheral test circuit is designed,which is able to realize testing the function and performance of the LDO chip.This scheme can be usedasa generaltestmethodfor reference ofLDO chiptestdesign.

LDO;CTA8280;CP;fuse

TN407

A

1681-1070(2017)11-0015-04

2017-06-29