基于SiGe BiCMOS工艺的射频ESD电路设计

吴舒桐,张甘英

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

基于SiGe BiCMOS工艺的射频ESD电路设计

吴舒桐,张甘英

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

随着射频电路工作频率的不断升高,ESD已经成为了影响电路可靠性和射频电路性能的重要因素。针对高速射频电路,设计了高速I/O口ESD防护电路和电源到地的箝位电路,并采用斜边叉指型二极管进行版图和性能优化。采用Jazz 0.18 μm SiGe BiCMOS工艺对该ESD防护电路进行设计和流片。经过测试得到,ESD保护电压最高可达到3000 V。更改二极管叉指数取得更高的ESD防护级别,改进后保护电压最高可达到4500 V。

射频集成电路;静电放电;SiGe BiCMOS工艺

1 引言

在射频应用时,随着电路工作频率的升高,ESD引入的寄生电容对射频行为的影响越来越大,ESD造成的电子产品失效已经占到20%的比例。

射频芯片更多地采用SiGe工艺和GaAs工艺,针对这两种工艺的ESD电路市场上仅有零零散散的模型和仿真结果,未见流片后I/O端口和电源/地ESD各种模型的实际电压的验证[1],依托SiGe超高速时钟缓冲器项目,进行射频ESD端口电路设计流片的验证很有必要。

本文基于Jazz 0.18 μm SiGe BiCMOS工艺设计了ESD保护端口电路,并结合工艺提出了二极管版图优化方案。

2 电路结构设计方案

射频电路所处理的射频信号速度快、摆幅小,对信号边沿要求高且容易受噪声干扰,所以对射频管脚的设计非常严苛,要满足损耗小、噪声低、电路透明度高等要求。一个典型的ESD防护电路拓扑结构如图1所示。ESD防护电路可大致分为I/O口防护电路和电源箝位电路两部分。

图1 射频端口ESD防护电路

2.1 I/O口ESD防护电路设计

基于SiGe工艺的高速I/O端口ESD电路结构如图2所示。射频电路为了更少地引入不必要的元件,减少设计中计算的复杂性,通常采用二极管作为ESD保护元件。其具有结构简单、放电效率高、寄生电容小以及不存在二次热击穿毁伤的危险等众多优点[2]。

当二极管正向偏置时,如式(1)所示,电流随正向偏置电压呈指数增长,放电效率非常高。且在指数式放电过程中,不存在电压电流回滞、负阻以及二次热击穿等工作区,极大简化了设计过程中的考虑维度。所以决定采用如图2(a)所示的结构对高速I/O口进行ESD防护。

在超高频频段,考虑寄生电容和寄生电阻、寄生电感是存在一些折衷的。考虑二极管的寄生电容这种折衷更加明显,由于放电通道的大小是由二极管的面积决定的,所以在设计中要仔细分析权衡和折衷上述各种因素,才可能取得较好的效果。

图2 I/O端口ESD防护电路

对于电压摆幅较高的输入端口,图2(a)所示的电路结构则无法满足设计要求。在电压摆幅较高时,为了对I/O端口实现更好的ESD防护,设计了如图2(b)所示的电路结构。为了使输入信号在输入高摆幅时不会使ESD保护二极管提前导通,在信号输入端增加了一级二极管以降低输入电压,从而可以实现高摆幅电压下的I/O端口ESD防护。

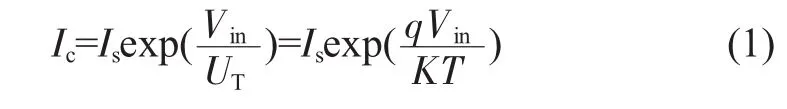

本次使用的二极管结构如图3所示。图3(a)为NWELL 二极管,其中 N+ 长为 8 μm,宽为 1.45 μm;P+ 长为 8 μm,宽为 0.5 μm,P、N 间距为 0.44 μm。图中所示的NWELL_8_4二极管的面积为16.35 μm×19.2 μm。图3(b)为PSUB二极管,其中P+长为8 μm,宽为 1.45 μm;N+ 长为 8 μm,宽为 0.5 μm,P、N 间距为0.4 μm。图中所示的PSUB_8_4二极管的面积为16.35 μm×19 μm。

图3 本次使用的二极管结构

2.2 电源到地的箝位电路设计

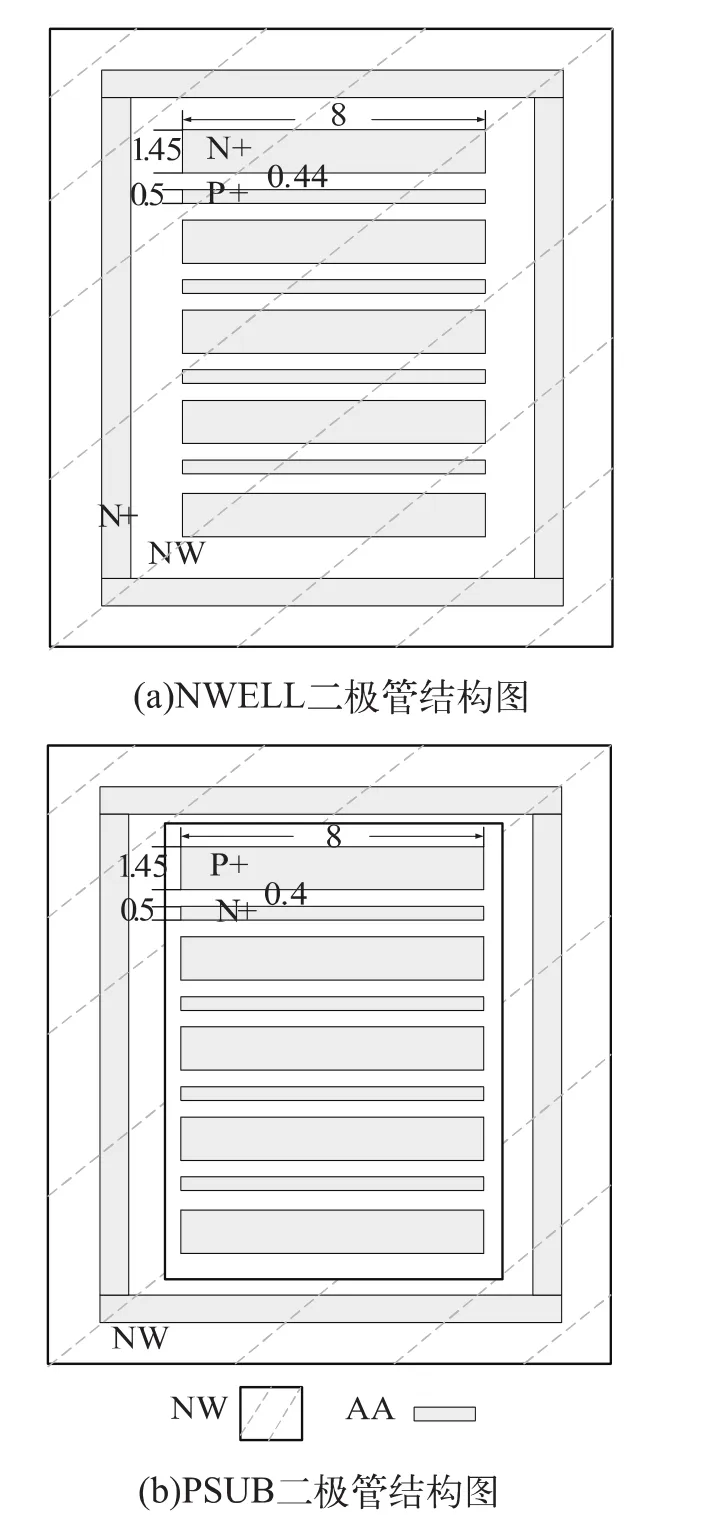

本电路的电源箝位电路其结构如图4(a)所示,该电路主要由三部分组成:RC检测电路、反相器、大尺寸的双极晶体管。

图4 电源箝位电路及wp2子模块内部结构

由MOS管实现的电阻和电容构成RC检测电路,用来检测电源和地之间的瞬态变化,输出的信号控制wp2子模块,子模块内部为先经过一级反相器增加驱动能力,然后用反相器的输出信号控制大尺寸双极管,决定是否泄放电流(设电阻R和电容C设计了合理的值,不会对电源的正常上电和波动起作用,即只对电源到地之间的ESD脉冲触发,而对电源线上的正常变化不会产生误触发),wp2子模块的电路图如图4(b)所示。

2.3 二极管版图优化

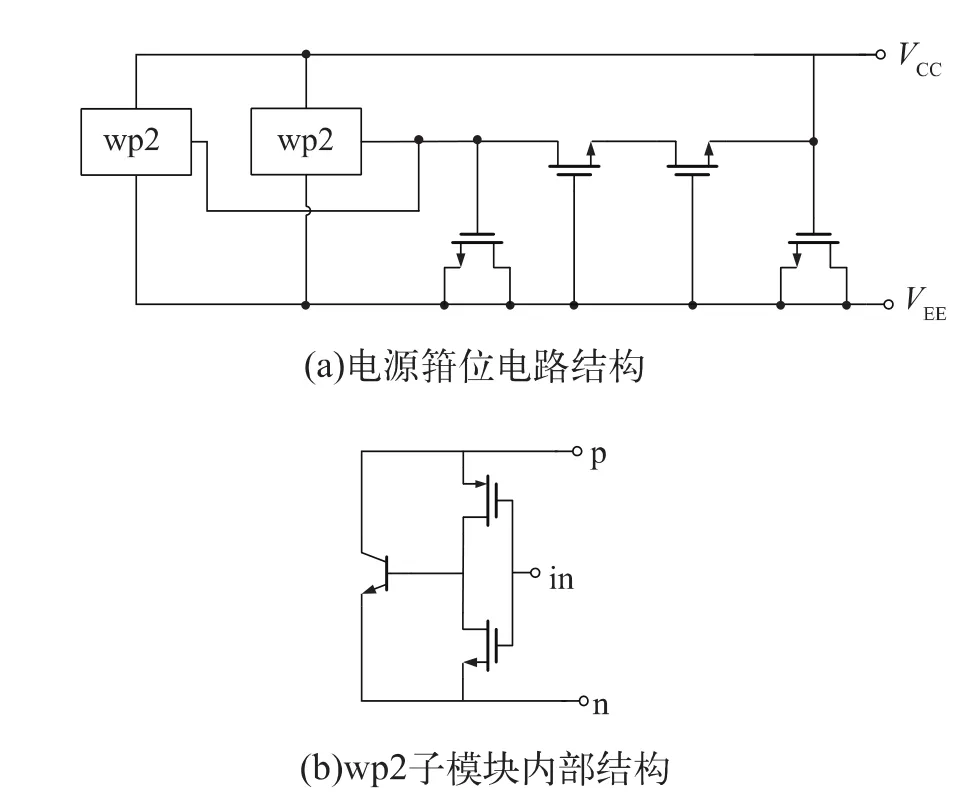

ESD防护二极管常用的是叉指型二极管[3],其版图结构如图5(a)所示。简单的双叉指ESD防护二极管的抗静电级别有限,当需要提高抗静电级别时,可通过加大叉指数进行抗静电级别的提升。通过仿真验证,选取最优的叉指数,得到更优的防护性能。

图5 叉指型与斜边叉指型二极管版图

由于本次设计的ESD保护电路主要应用于超高速时钟缓冲器项目中,对输入输出信号的速率有很高的要求。所以,在普通矩形叉指型二极管的基础上进一步做出优化,采用如图5(b)所示的斜边叉指型二极管[4]的结构,提高边缘面积比。由于叉指条电流密度分布不均,在发射条的根部电流密度更大,而头部电流密度偏小,因此可以设计成根部粗、头部细的斜边叉指型结构,这样的二极管具有寄生电容小、静电泄放效率高、面积小等优点。

2.4 电路结构优化

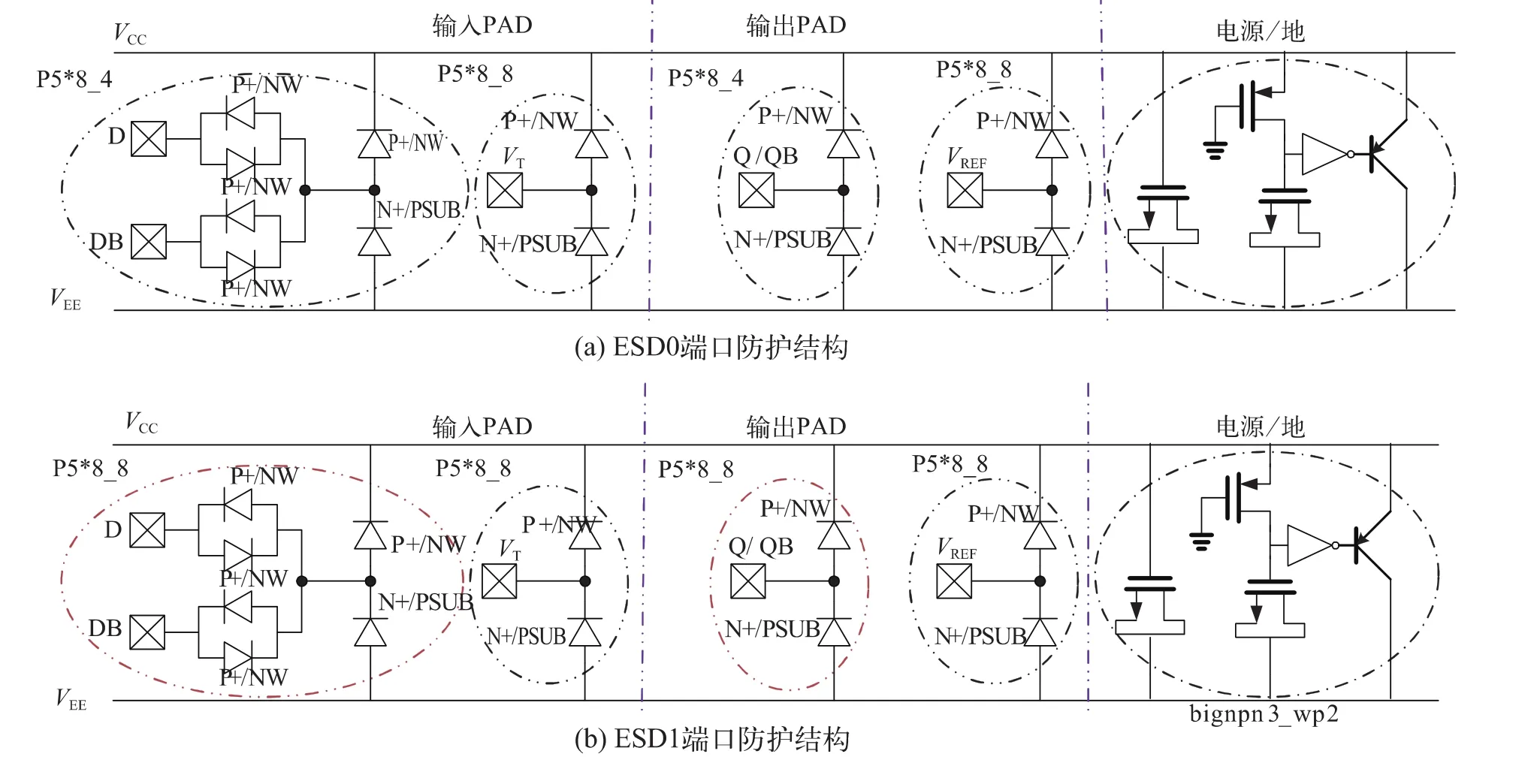

在ESD保护端口设计时,针对SiGeBiCMOS工艺,根据上文所述的设计方式,使用如图6(a)所示结构ESD0。

为了进一步提高ESD端口保护电路的最高保护电压,对图6(a)所示结构进行改进。在本次研究中,设计了一款ESD0的对比结构ESD1,如图6(b)所示。下面具体讲述ESD1端口结构的改进方式。

图6 ESD端口设计优化

ESD二极管的防护级别与寄生电容之间是设计的一个矛盾点。在I/O防护电路中,可以通过加大二极管的叉指数来得到更大的寄生电容,这样就可以承受更大的脉冲电流,从而达到更高的ESD防护级别;但是同时,大的寄生电容会给射频信号带来巨大的影响,会使电路的噪声性能和匹配情况发生很大的偏离。所以,如何选择合适的叉指数来得到更优的ESD防护级别,同时不对内部电路性能产生影响是至关重要的。

由于本次ESD防护电路应用于超高速时钟缓冲器项目,I/O端口信号速率很高。为了高速信号通过ESD电路时不受影响,且能进一步提高ESD防护级别,最终经过仿真分析,在防护级别与寄生电容之间进行折衷后,决定增大高速I/O口电路中二极管的叉指数,将其变为ESD0电路的两倍,得到ESD1端口防护结构,如图6(b)所示。

3 测试结果与分析

经过流片后的测试结果如下。在ESD0端口防护电路中,高速输入端口的TLP测试曲线如图7所示,右侧曲线代表电流-电压(I-V)特性,左侧曲线代表对应的漏电流。测试结果显示,随着脉冲电压逐步增大,一开始漏电流很小且保持一致,当TLP电流达到约2 A时,漏电流值急剧增大,表明电路已经失效。根据测试结果得到,ESD0防护端口能支持的最大保护电压为3000 V。

图7 ESD0输入端口的TLP测试曲线

在ESD1端口防护电路中,高速输入端口的TLP测试曲线如图8所示。当TLP电流达到约3 A时,漏电流值才开始急剧增大,电路开始失效。根据测试结果可得,此ESD1防护电路能支持的最大保护电压为4500 V。ESD1结构的测试结果显示,与ESD0相比其大大提高了电路的ESD防护性能。

图8 ESD1输入端口的TLP测试曲线

4 结束语

基于SiGe BiCMOS工艺,设计了高性能ESD端口防护电路,使用斜边叉指型二极管改进版图和二极管性能,并使用更改二极管叉指数的方式改进结构,提高电路的ESD保护电压值;同时进行了射频ESD端口保护电路的设计流片验证,为后续SiGe射频电路研发积累了技术基础。

[1]谭雅雯.基于SiGe工艺的射频ESD电路研究与设计[D].西安:西安电子科技大学,2013:1.

[2]Gray P R,Hurst P J,Meyer R G,et al.Analysis and design of analog integrated circuits[M].New York:John Wileyamp;Sons,2008.

[3]Yeh C T,Ker M D,Liang Y C.Optimization on layout style of ESD protection diode for radio-frequency front-end and high-speed I/O interface circuits[J].Device and Materials Reliability,IEEE Transactions on,2010,10(2):238-246.

[4]李国华.基于BiCMOS工艺的超宽带ESD电路研究与设计[D].西安:西安电子科技大学,2014:15.

吴舒桐(1993—),女,江苏无锡人,硕士,毕业于日本早稻田大学,现在中国电子科技集团公司第五十八研究所射频组,主要从事射频集成电路设计工作。

Design of RF ESD Circuits Based on SiGe BiCMOS Technology

WU Shutong,ZHANG Ganying

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

With the increase ofthe frequencyof the radio frequencyintegrated circuits(RFIC),ESD has become a serious issue affecting the reliability and RF performance.An I/O ESD protection circuit and a power clamp circuit have been designed for high-speed RF circuit.And the beveled interdigital diode is used to do the layout and performance optimization.The proposed circuit is fabricated in Jazz 0.18 μm SiGe BiCMOS process.After the test,the protection voltage of the circuits is up to 3000 V.A higher protection level can be achieved by changingtheinterdigitalnumberofthediodes.Andtheprotectionvoltageoftheimprovedcircuitisupto4500V.

RFIC;ESD;SiGe BiCMOSTechnology

TN407

A

1681-1070(2017)11-0019-04

2017-09-15