基于ATE的SRAM测试

奚留华

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

基于ATE的SRAM测试

奚留华

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

随着集成电路技术的飞速发展,SRAM的应用越来越广泛,其测试技术也得到了广泛的重视和研究。简要介绍了SRAM的重要组成部分,提出了一种ATE对SRAM测试的方法。SRAM的测试有功能测试、直流参数测试、交流参数测试,功能测试和交流参数测试对存储器来说是至关重要的。以IS61LV51216-10TLI为例,其功能测试是通过UltraEdit软件编辑生成测试码,对被测器件各个不同存储单位进行读写操作,以检查其功能。主要论述了SRAM功能及交流参数的测试关键技术及其注意事项。

ATE;SRAM;测试;功能;交流参数

1 引言

SRAM[1~3]即静态随机存储器,大多是由CMOS管组成的挥发性静态存储器,在掉电后存储器中所存数据就会丢失。随机静态存储器可以对任何地址进行读写操作,通过锁存器的原理对数据进行保存,在无操作状态下,锁存器处于稳态,保持数据稳定,不用进行周期性的电荷刷新。SRAM由基本单元构成的阵列以及外围电路构成,其中阵列的划分和外围电路的优劣对整个SRAM的性能有很大的影响。静态随机存储器是随机存储器中的一种,它由静态挥发性存储单元构成的存储阵列组成,其地址译码集成在片内。SRAM速度很快而且不用刷新就能保存数据不丢失。它以双稳态电路形式存储数据,结构复杂,内部需要使用更多的晶体管构成寄存器以保存数据。SRAM由于靠连续的供电来维持所存数据的完整性,故属于易挥发性存储器。随着集成电路技术的飞速发展,SRAM的应用越来越广泛,其测试技术也得到了广泛的重视和研究,存储器的功能测试和交流参数测试至关重要。本文通过结合ATE的方法,测试功能及其交流参数。

2 测试仪器和电路

采用的测试仪器是Teradyne公司的J750,该系统测试频率为100 MHz,测试通道数多达512个,测试向量深度可达16 M[4]。测试电路为IS61LV51216-10TLI。

3 功能测试

3.1 SRAM功能原理

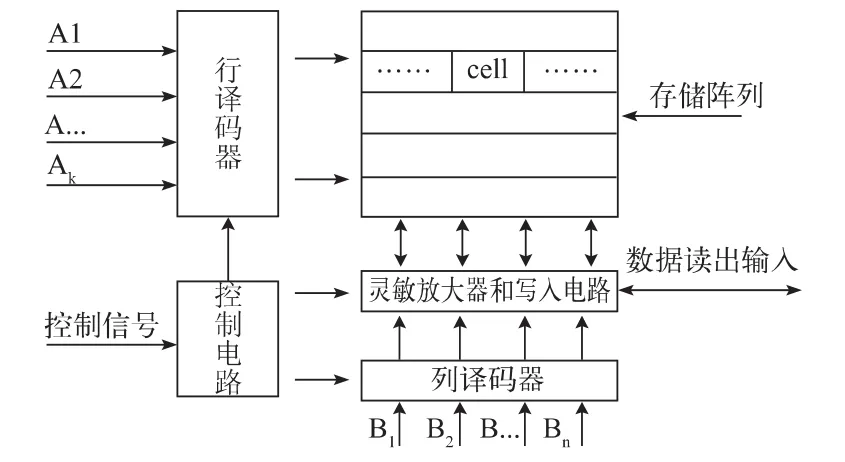

SRAM电路由存储阵列、灵敏放大器、译码器、输入输出电路和时序控制电路五大部分组成。存储单元按行和列排列起来组成SRAM的阵列结构,行和列分别称为“字线”和“位线”。每个存储单元对应于一个唯一的地址,行和列的交叉定义出地址,而且每一个地址和某一特定的数据输入输出端口是相连的。一个存储芯片上的阵列数目是由整个存储器的大小、数据输入输出端口数目、存储速度要求、整个芯片的版图布局和测试要求所决定的。

如图1所示的存储阵列是由存储单元(cell)构成的矩形阵列。每一个单元都有自己独特的地址,通过外围的译码电路选中相应的单元进行读写操作。译码电路包括行译码电路和列译码电路,其中行译码电路用来从2K行中选一行,列译码电路是从2n列中选出一列。这样通过行译码列译码的共同作用来从阵列中选出相应的单元进行读写操作。灵敏放大器和写入电路用来对数据进行读写操作。在数据读出过程中,由于位线过长使得从单元中读出的信号很弱,需要用灵敏放大器来放大信号,加快数据的读出过程。写入电路用来进行数据的输入。控制电路主要用来控制数据的读写以及译码过程。通过相应的控制信号如读使能信号、写使能信号来控制数据的读写操作。

图1 SRAM的整体结构

3.2 SRAM功能码的编写

用ATE对SRAM功能码进行测试的要求是二进制格式。IS61LV51216-10TLI电路总共有三种类型的管脚分类,分别是CE、OE、WE、LB及UB等的控制管脚;A0、A1、A2、A3、A4、…、A16、A17、A18等地址输入管脚;I/O0、I/O1、I/O2、I/O3、I/O4、…、I/O13、I/O14、I/O15等数据输入输出管脚。其中CE是芯片使能输入端,OE是输出使能输入端,WE是写使能输入端,LB是低字节控制端,UB是高字节控制端。当WE、CE、LB、UB分别处于低电平输入的状态时,OE无论处于哪种状态,电路处于数据写入的状态。此时,若LB处于高电平输入的状态,I/O0、I/O1、I/O2、…、I/O6、I/O7处于高阻输入状态,I/O8、I/O9、…、I/O15处于数据写入状态;若 UB 处于高电平输入状态,I/O0、I/O1、I/O2、…、I/O6、I/O7处于数据写入状态,I/O8、I/O9、…、I/O15处于高阻输入状态;若 LB、UB 分别处于高电平输入状态,I/O0、I/O1、I/O2、I/O3、I/O4、…、I/O13、I/O14、I/O15都处于高阻输入状态。当 CE、OE、LB、UB分别处于低电平输入状态时,WE处于高电平输入状态,电路处于数据输出状态。此时,若LB处于高电平输入的状态,I/O0、I/O1、I/O2、…、I/O6、I/O7处于高阻输出状态,I/O8、I/O9、…、I/O15处于数据输出状态;若 UB 处于高电平输入状态,I/O0、I/O1、I/O2、…、I/O6、I/O7处于数据输出状态,I/O8、I/O9、…、I/O15处于高阻输出状态;若LB、UB分别处于高电平输入状态,I/O0、I/O1、I/O2、I/O3、I/O4、…、I/O13、I/O14、I/O15都处于高阻输出状态。

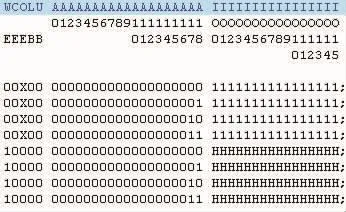

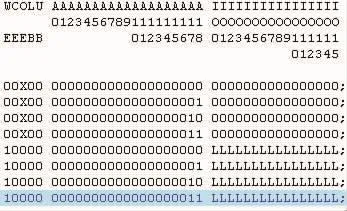

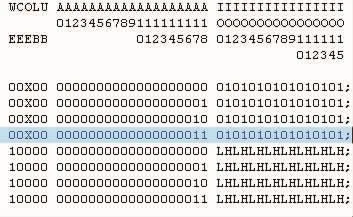

IS61LV51216-10TLI具有 A0、A1、A2、…、A16、A17、A18等19个地址,若要覆盖100%的功能,必须要有219行的写地址以及219行的读地址,每个地址必须要验证其对0和1的读写有效,分四组验证其功能。分别写读0000…、0101…、1010…、1111…等功能,部分地址的功能如图2、图3、图4、图5所示。

3.3 功能测试故障分析及注意事项

写后恢复时间过长,即地址写入一串数据以后,在地址的前几行读的数据不稳定。分析其原因,可能是时序设置的问题,假如控制管脚、地址输入管脚及I/O输入管脚同时进行数据输入,造成了I/O管脚的数据输入延迟,与此同时,I/O管脚进行数据输出时,也延迟了一定的时间,刚开始读数据时,读的并不是所写的数据,而是存储器里面的原始数据,使得功能不能Pass。解决这种问题的方法是重新设置时序,使得控制管脚先输入数据,使得电路处于受控制状态,此时I/O端口再输入数据时,就不会发生延迟,功能也就正常了。解决此类问题的另外一种方法是在数据输出功能码的起始行重复repeat功能码,使其能够抵消I/O端口在数据输入阶段所产生的延迟误差。产生这种问题的另外一种原因可能是因为存储器在原始状态下并不是一个清空的存储器,里面具有原始的数据,初始读的数据和存储器里面的原始数据有关,为了避免这种因素,可以使得原来低电平有效的管脚设置成高电平,使得数据的输出端口变成高阻态,这一步操作可以使得原来存在的数据清空,可以读出所写的数据。

图2 写读1的功能码

图3 写读0的功能码

图4 写读10的功能码

图5 写读01的功能码

4 SRAM直流参数测试

直流参数测试项目包括开/短路测试(O/S)、输出高/低电平测试(VOH/VOL)、输入高/低电流测试(IIH/IIL)、输入/输出漏电流测试(ILI/ILO)、电源电流测试(ICC)等等。

开短路测试主要用于测试电子器件的连接情况;输出高低电平测试的目的是检查器件在指定电压输出电流的能力;输入端在输入规定电压值的时候,测量到流入输入端的高/低电流,目的是检查DUT的输入负载特性。这个参数主要是验证器件接受逻辑值1和0的能力。所谓漏电流是指在没有故障施加电压的情况下,电气中相互绝缘的金属零件之间或带电零件与接地零件之间通过周围介质或绝缘表面所形成的电流。电源电流测试用于检查器件的功耗。

5 SRAM交流参数测试

5.1 交流参数简介与测试原理

交流参数测试是测量器件晶体管转换的时序关系的,交流测试的目的是保证器件在正确的时间发生状态转换。

交流参数包括数据读取的周期时间tRC,地址访问时间tAA,输出保持时间tOHA,CE管脚的访问时间tACE,OE管脚的访问时间tDOE,OE管脚从高电平到输出高阻态的时间tHZOE,OE管脚从低电平到输出高阻态的时间tLZOE,CE管脚从高电平到输出高阻态的时间tHZCE,CE管脚从低电平到输出高阻态的时间tLZCE,LB、UB的访问时间tBA,LB、UB从高电平到输出高阻态的时间tHZB,LB、UB从低电平到输出高阻态的时间tLZB,电源上电时间tPU,电源下电时间tPD,数据输入的周期时间tWC,CE管脚到数据输入结束时间tSCE,地址建立到数据输入结束时间tAW,从数据输入结束的地址保持时间tHA,地址建立时间tSA,LB、UB有效到数据输入结束时间tPWB,WE脉冲宽度tPWE,数据建立到数据输入结束的时间tSD,从数据输入结束到数据保持的时间tHD,WE从低电平到输出高阻态的时间tHZWE,WE从高电平到输出高阻态的时间tLZWE。

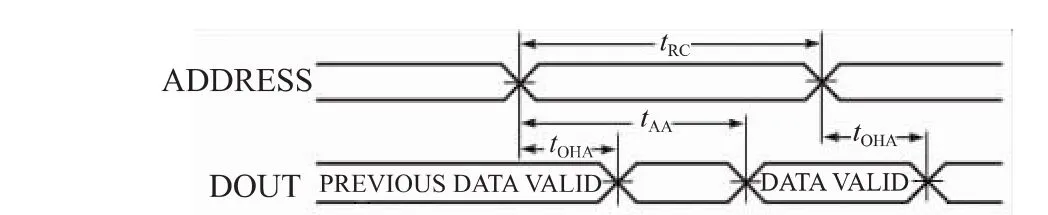

由于tAA、tLZOE、tLZCE等交流参数的测试原理和测试方法基本相同,因此,仅以测试tAA为例来说明交流测试。

tAA是指地址输入端在施加规定的电平和脉冲电压时,地址输入端某一个地址的上升沿到输出数据有效的延迟时间。在常温下,将被测器件接入测试系统中,电源电压调到器件详细规范规定的电压值,其余输入端施加器件详细规范规定的电平,在一个地址的初始端到数据输出有效的延迟时间即tAA,图6列出了测试tAA的波形图。

图6 tAA波形图

5.2 交流参数的测试方法

在半导体集成电路的研制和生产中器件的交流参数测试是由测试机来实现的。不同的测试系统其测试的基本原理与方法基本上是一致的[5],一般而言,我们使用搜索法来测试交流参数,下面以在测试机J750系统上测试tAA参数为例来介绍测试机如何进行交流参数的测试。

Search即二进制搜索,通过重复测试来搜索不断变化的参数。利用搜索法测试交流参数的基本思想是给出确定的测试条件,在一定的选通范围内对选通时间进行搜索。基本方法是先将器件用转接卡接到测试机上,在J750系统上,在pinmap中定义管脚名,在channel map上定义转接卡与J750系统连接的通道号,这样就实现了器件与测试机的连接。在Pin level中为各输入端的电平赋值,电源电压赋值,在Time set(Basic)中输入波形,使其与规范中要求的输入波形一致。以上就完成了交流测试前的设置工作。Characterization editor是进行交流测试设置的,设置模式为measure模式,设置搜寻边沿的范围、步距、算法,然后通过跑功能的形式,测出电平转换边沿的具体时间。测地址访问时间tAA,在一个Charcterization editor中设置搜寻边沿范围为0~10 ns,步距设为0.1 ns,算法为Pos liner,功能名设为tAA,测得地址访问时间tAA。

5.3 交流参数测试注意事项

如图7所示,我们所要测试的地址访问时间是第3行pattern从地址输入到输出有效的延迟时间,第二个地址中写入了01的数据,但是没有读的操作,原因是假如前面几行一直是X,读出的数据也是X,一瞬间从X到二进制数据的转变可能会出现数据的延迟,而导致功能的Fail,所以当我们测试第3行的数据时,在第2个地址中写入二进制的数据作为缓冲,消除数据的输出延迟。

图7 交流参数测试码

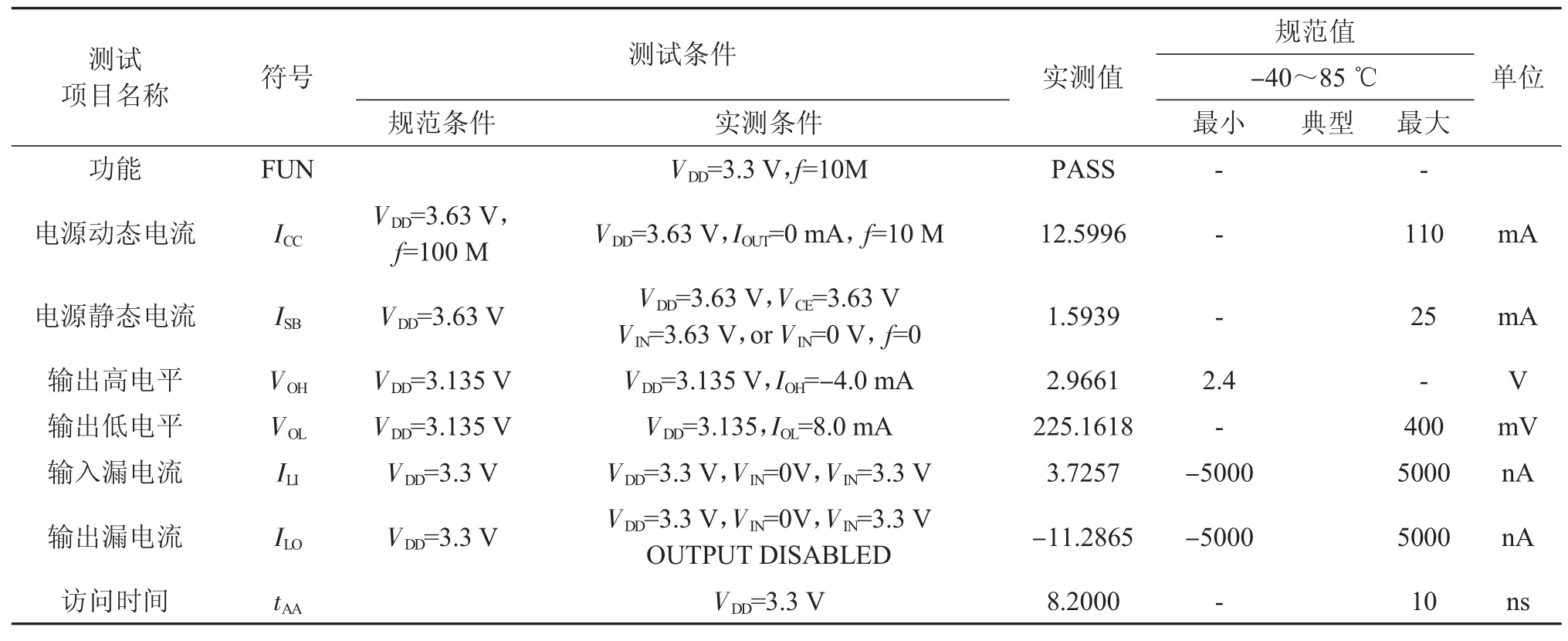

6 测试方法与标准验证

表1所示为SRAM测试的直流参数规范标准。从表2所示可见在规范测试条件下的测试值在标准范围内,验证了测试方法的正确性。

表1 直流参数测试规范标准

7 结论

文章简要介绍了SRAM的重要组成部分,提出了一种ATE对SRAM测试的方法。主要介绍了电路的功能测试和交流参数测试的关键技术。通过UltraEdit软件编辑生成测试码,对被测器件各个不同存储单位进行读写操作以检查其功能,与此同时,结合部分功能码在ATE软件中设置相关参数,测试了SRAM的交流参数。

[1]王红,彭亮,于宗光.FPGA现状与发展趋势[J].电子与封装,2007,7(7):32-35.

[2]张吉,罗喜明,王军,等.SRAM存储器动态参数测试向量分析[J].电子与封装,2015,15(5):4-7.

表2 测试实际值与标准验证

[3]孙立波,雷加.基于SRAM型FPGA测试技术的研究[J].研究与开发,2011,30(5):36-41.

[4]解维坤.基于ATE的FPGA测试[J].电子与封装,2009,9(2):17-19.

[5]张静,祥苓,李海泉.浅谈集成电路交流参数的测试[J].微处理机,2008,(3):28-30.

奚留华(1991—),男,江苏常州人,硕士学历,助理工程师,现从事集成电路测试技术研究。

SRAM Testing Based on ATE

XI Liuhua

(China Electronics Technology Corporation No.58 Research Institute,Wuxi 214035,China)

With the rapid development of integrated circuit technology,the application of SRAM is becoming more and more extensive.Testing technology of integrated circuit has been paid more and more attention.The paper briefly introduces the important components of SRAM,and puts forward the way of testing SRAM by ATE.SRAM testing includes functional testing,DC parameter testing,AC parameter testing.Functional testing and AC parametertesting are essentialformemory.Forexample,functionalcode testing of IS61LV51216-10TLI is edited by UltraEdit software.Functional code is read and written in the different memory units of the device to check its function.The key technology and precations of function and AC parameterstestingofSRAMare mainlystated.

ATE;SRAM;testing;function;ACparameter

TN307

A

1681-1070(2017)11-0010-05

2017-06-29