一种用于MEMS加速度传感器的低功耗低噪声全差分电路

张 航,金湘亮,杨 柳

一种用于MEMS加速度传感器的低功耗低噪声全差分电路

张 航,金湘亮,杨 柳

(湘潭大学 微电子科学与工程系,湖南 湘潭 411105)

设计了一种用于MEMS加速度传感器的低功耗低噪声的全差分电路,采用套筒式电路结构,增加了输出阻抗,减少了功耗和噪声。适当的共模反馈,提高了环路足够的补偿,避免了输出信号的失真,确保获得好的相位裕度以及一个快速的反应。在0.5 μm CMOS工艺模型下,Cadence Spectre电路仿真的结果表明,电源电压为5 V,频率的范围是0.1 Hz到100 MHz时,得到电路的噪声大小是5.777 891 μV·Hz–1/2,功耗大小为41.768 mW,版图的面积为1834.18 μm×1446.87 μm。这一电路可以用于地震监测以及石油勘探等领域。

低功耗;低噪声;全差分电路;套筒式;共模反馈;版图

在过去的几十年里,MEMS(Microelectro Mechanical System)加速度传感器在模拟电路设计研究领域已经变得越来越具有挑战性和吸引力。在日常生活领域中[1-3],应用于移动电话上的触摸屏,也是MEMS加速度传感器的一个常见示例。带有高精度特性的模拟技术帮助科研人员实现了低功耗以及扩充了输出电压摆幅(动态范围)的性能。此外,在适当的电源电压下,为了实现宽的输出电压摆幅,全差分电路是非常适合被采用的电路之一。另一方面,绝大多数模拟电路前置运放中,全差分电路都被用于降低闪烁噪声、提高增益以及降低功耗。但是,全差分电路应用的必不可少的条件之一是需要电路具有相对高的环路增益[4]。

在传统的电路里,比较常见的运算放大器主要有两级运算放大器、增益提高运算放大器、折叠式共源共栅电路以及套筒式共源共栅电路[5-7]。虽然两级运放和增益提高运放电路的增益高,电压输出摆幅较大,但是相较于折叠式共源共栅电路以及套筒式共源共栅电路来说,前者的速度较慢,一般不宜作为前置运算放大器。而折叠式共源共栅电路相较于套筒式共源共栅电路而言,它的功耗较高,并且电路中的噪声也很大。因此,选择套筒式共源共栅结构作为本文的研究对象。

本文设计的全差分套筒式共源共栅运放CMOS结构相对于单端信号来说,可以有效地抑制电压失真,增大最大的输出电压摆幅。通过全差分电路结构,共模电平被干扰,抑制共模噪声,对环境有更强的抗干扰能力。同时,差动电路的偏置更加简单和有更高的线性度[8]。本设计电路相对简单,易于实现,通过共模反馈电路,使输出更加平稳。

图1表示为MEMS加速度传感器系统框图。在地震监测和石油勘探等领域,检测到振动的加速度信号被传感器接收,通过内部的物理关系转换,得到相应的输出电压。在控制系统的调控下,输出电压负反馈作用于传感器,使得传感器调整上下极板的电容差,最终使输出趋于稳定。而本文研究的主要部分是检测电路(全差分电路),具有承上启下的作用。

图1 MEMS加速度计系统框图

1 传统的差分电路

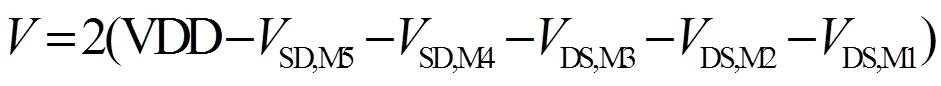

在传统的差分电路里,输出电压摆幅是全差分电路输出摆幅的一半[9-10]。传统的差分电路如图2所示,它的输出电压摆幅表达式如方程式(1)所示。

图2 基本的套筒式共源共栅电路

相对于折叠式电路,套筒式电路具有低噪声、低功耗以及更加精确的偏置电压VBIAS的优势,因此在本文中更倾向于选择套筒式结构作为主结构[11-12]。输出电压表达式可以写为:

一般来说,共模反馈分为如下几个步骤:首先电路可以检测到输出的共模电平,然后将得到的电平与设定的参考电压作比较。通过比较之后,最后误差反馈到运算放大器的偏置网络。对比基本的差分电路,本文采用的是带共模反馈的全差分结构。这种情况下,MOS管的输出和输入电阻增加,就会有效地提高电路的差分增益,同时避免了镜像极点。相对于折叠式结构,在套筒式结构中选用的MOS管数量更少,这就可以充分实现低功耗以及低噪声。此外,在相同的情况下,折叠式电路结构产生的功耗是套筒式电路结构功耗的2到3倍。电路应用了电阻共模反馈,此结构可以使得整个电路更加稳定。

从图2可以看出,电路中的电流从其他两纵路支路汇集到MOS管M1,MOS管M1的漏极,MOS管M2以及MOS管M9相连。因此,M1中的电流大小是M2与M9中的电流值之和。为了改善输出的情况,保证电路稳定性而用CMFB(Common Mode Feedback)。在下一部分,会详细地描述CMFB,它能克服工艺的变化。简单来说,展现了一个新的全差分电路分析[13-14]。

2 全差分电路设计与分析

表1是电路设计参数表。工艺是0.5 μm,电源电压是5 V,环路增益不低于120 dB,噪声大小不超过15 μV·Hz–1/2,功耗小于50 mW。

表1 设计参数表

Tab.1 The table of design parameters

电路的整体结构如图3所示,电路中的电容与电阻对称分布,起到匹配以及滤波的作用。其后的减法器和缓冲器扩展了电路的带宽。全差分电路核心结构如图4所示。电路的输入对管是PMOS,可以有效地减少闪烁噪声。同时,两级的电路结构最大化实现了增益的增加。此外,第二级用级联结构提高了电路的输出阻抗,这就是说,这一结构可以改善第二级的增益。另外,双端输出的电路结构提升了输出电压摆幅。

图3 整体电路结构

现分析CMFB检测理论。当R1与R2的阻值相等的时候,输出的共模电压可以表示为:

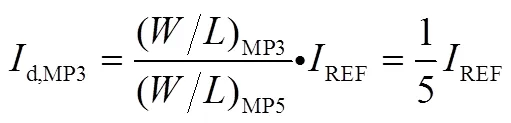

对比Vref,它能够控制第一级的尾电流。从负反馈角度来看,当Vout,CM增加,也就是VSG,M5降低。产生的结果是,MOS管MN5中的电流变小,这就导致VG,MN5变小以及VG,MN1变小。利用MOS管之间的宽长比例关系,可以得到不同支路的直流电流的大小。

当PD是低电平的时候(即电路正常工作),MOS管MN3,MN3’,MN4和MN6关断。这时候M7开启,从而使得M7工作在饱和区。假设此时通过M7的电流大小为REF,考虑到此时MOS管宽长比的比例关系,d,M1的大小为5REF。电流可以用下面的表达式描述:

式中,和分别指的是MOS管的宽和长。

对于第二级的情况,d,MP2的大小为2REF。

此外,d,MP3的大小为1/5REF,流过M5的电流d,M5大小为1/10REF。具体的电流分配关系如下:

饱和区电流的表达式可以描述如下:

式中,TH代表的是MOS管的阈值电压。

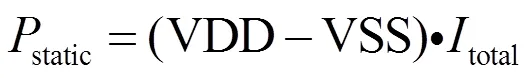

CMFB产生电压01和02,经过电阻R1和R2之后得到电压0。正是因为CMFB,可以得到更好的输出电压。通过方程(7)和(8),能够很清楚地看到电流的大小依赖于/的比值,迁移率以及阈值电压TH。一般说来,可以通过改变MOS管的/比值和个数,从而改变电流值。另外,MN1和MN1’也限制了MOSFET的电流大小[15]。电路中总的静态功耗大小可以用方程(9)描述:

式中:VDD和VSS的大小分别是5 V和–5 V;total是连接VDD与VSS所有支路的电流之和。

3 仿真结果与分析

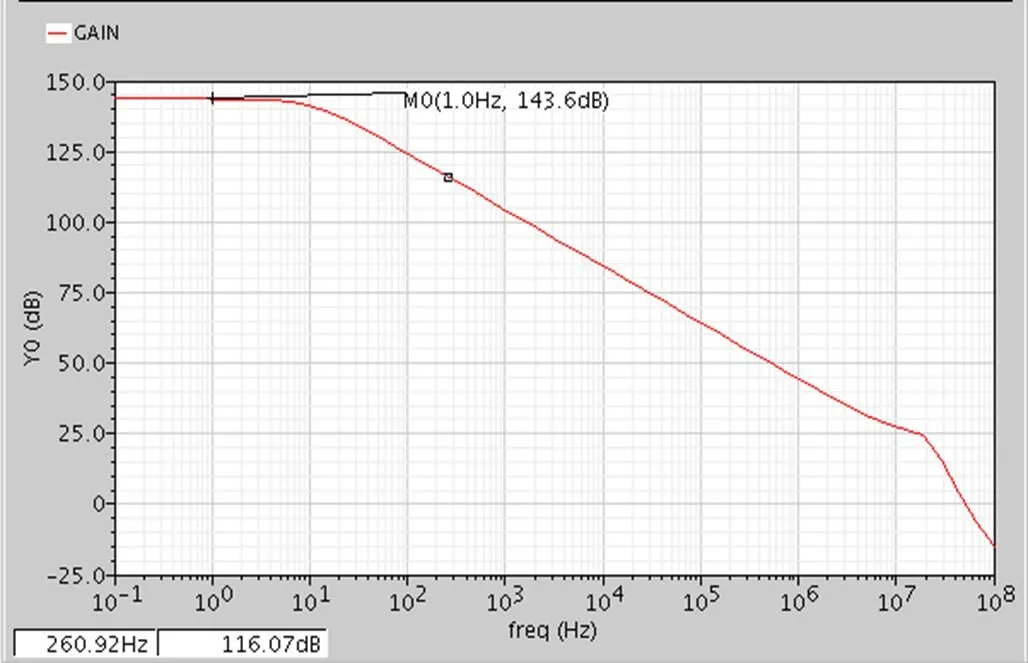

基于0.5 μm CMOS工艺模型下,采用Cadence Spectre软件对本文所设计电路进行仿真。如图6所示,电路的环路增益达到了143.6 dB(在27 ℃室温下,频率的范围从0.1 Hz到100 MHz),电路的噪声达到了5.777 891 μV·Hz–1/2。总的电流包含所有的电流之和。在此基础上,电路的总功耗大小为41.768 mW。

在这种情况下,计算d,M6和d,MN2,能够得到两者的数值大小分别是REF和5REF。环路增益的仿真模型如图5所示,输入的直流电压大小为0 V,同相输入端和反相输入端的交流电压大小分别为0.5 V 和–0.5 V。假定输入信号均为理想信号,PD = –5 V以及REF=200 μA。通过图6的仿真曲线可以得到环路增益大小为143.6 dB,仿真的结果符合设计的指标。

图5 环路增益的仿真模型

图6 环路增益与频率的关系曲线

图7分析的是电路的稳定性,输出端的电阻和电容串联起到一定的滤波作用。电路中使用了理想的探针,使得输出更加趋于稳定。图8的结果表明:环路增益带宽是4.327 MHz以及相位裕度的大小为72.66°。

图7 稳定性仿真模型

本文与其他文献的噪声和功耗性能参数比较如表2所示。本电路设计简单,易于实现,增加了共模反馈,使得输出更加平稳,并且显示出了更好的噪声和更低的功耗。

图8 全差分电路稳定性曲线

表2 与其他发表电路性能比较

Tab.2 The performance comparison of published circuits

对于低功耗和低噪声仿真的结果列在表2中。基于表中的数据,可以得到噪声的大小是5.777 891 μV·Hz–1/2,功耗的值为41.768 mW。

本论文中的电路前仿和后仿如表3所示。由表3可见,前仿和后仿的结果也十分接近,这说明本电路设计比较合理。

表3 本设计前仿与后仿结果

Tab.3 Pre-simulation and post-simulation results

通过用四方交叉的设计技术来实现版图高度匹配性和复杂性,从而改善了输出的精确性。电路的版图如图9所示,版图的面积大小是1834.18 μm ×1446.87 μm。

图9 全差分电路版图

4 结论

本文是在传统的差分电路的基础上增加了共模反馈结构,设计了一种低噪声低功耗的全差分运算放大器。该电路简单,易于调试,极好地优化了电路的功耗和噪声。在0.5 μm CMOS工艺模型下,采用Cadence Spectre软件对本文所设计电路进行仿真。室温27℃,电源电压给5 V,设计出的全差分运算放大器电路的版图面积为1834.18 μm×1446.87 μm。电路的噪声大小仅为5.777 891 μV·Hz–1/2,功耗仅为41.768 mW。

[1] YU C L, MAO L H, XIAO X D, et al. A standard CMOS fully differential transimpedance amplifier with an integrated differential photodetector for optical communication and interconnection [J]. Sci Chin: Inf Sci, 2010, 40(9): 1281-1292.

[2] XIAO Y C. The condition and application of MEMS sensor [J]. Chin High-Tech Enterp, 2016, 35(6): 46-47.

[3] XU H, CHANG B, HAO X L. The development and application of MEMS sensor [J]. Wireless Internet Technol, 2016, 36(3): 95-96.

[4] LI Y P, HE C D, ZHANG J T. Design and analysis of capacitive MEMS ultrasonic sensor [J]. Transducer Microsyst Technol, 2014, 33(11): 73-74.

[5] SHI Z F, WANG W D. A design of fully differential gain-boosted operational amplifier [J]. Chin J Electron Devices, 2015, 38(1): 78-82.

[6] WANG D Z, REN Z X, GU Q B. Design of a novel fully differential on-chip inductor [J]. Microelectronics, 2016, 46(6): 818-820.

[7] SONG Q W, ZHANG Z P. Design of a novel high-speed fully-differential CMOS operational amplifier [J]. Modern Electron Tech, 2012, 35(4): 166-169.

[8] MA L, YANG Z F, HUANG W K. A pre-fully differential operational amplifier with lower high-frequency noise [J]. Microelectron Comput, 2012, 29(8): 102-106.

[9] ZHU J N, YANG B, JIANG Y F. Analysis and design of a high gain fully differential operational amplifier [J]. Microelectronics, 2015, 45(6): 714-716.

[10] TANG X L, LIU K Z, WANG L F. Design of high-performance fully differential operational amplifier [J]. J Hebei Univ Sci Technol, 2012, 33(1): 50-55.

[11] LUO P, PANG Y. Analysis and design of a low noise high CMRR operational amplifier [J]. Digit Commun, 2014, 41(2): 77-80.

[12] CHEN C Y, HEI Y, HU X Y. A chopper-stabilized operational amplifier for sensor signal detection [J]. Microelectronics, 2012, 42(1): 17-19.

[13] RAZAVI B. 模拟CMOS集成电路设计[M]. 陈贵灿, 程军, 译. 西安: 西安交通大学出版社, 2002: 123-125.

[14] NGUYEN T K, KIN C H, IHM G J, et al. CMOS low-noise amplifier design optimization technique [J]. IEEE Trans Microwave Theory Tech, 2004, 52(5): 1433-1442.

[15] MA H, HUANG Q, QIN M, et al. Modeling and simulation of a novel capacitive temperature sensor [C]//IEEE 9th International Conference on Solid-State and Integrated Circuit Technology, Beijing. NY, USA: IEEE, 2008.

[16] LUO Z Y, LI W, LI N, et al. Design and simulation of a low power amplifier [J]. Res Prog Solid State Electron, 2008, 28(4): 554-558.

[17] WANG W, WU W, FENG Q, et al. Design of low-power CMOS RF lower noise amplifier [J]. Infrared Laser Eng, 2009, 44(5): 1587-1592.

(编辑:陈丰)

A low power, low noise fully differential circuit for MEMS acceleration sensor

ZHANG Hang, JIN Xiangliang, YANG Liu

(Department of Microelectronic Science and Engineering, Xiangtan University, Xiangtan 411105, Hunan Province, China)

A low power and low noise with fully differential circuit for MEMS acceleration sensor was described. Folded cascode structure was adopted for the sake of increasing output impedance, decreasing power and reducing noise. In this way, proper common mode feedback structure compensates the loop circuit, avoids the output signal’s distortion, ensures that phase margin is better and gets a quicker response. Based on 0.5 μm CMOS process, the results of Cadence Spectre circuit simulation show that when supply voltage is 5 V, the noise of circuit is 5.777 891 μV·Hz–1/2and the power reaches 41.768 mW in the frequency range from 0.1 Hz to 100 MHz. In addition, the area of layout is 1834.18 μm×1446.87 μm. For the specific performance, it can be used in earthquake forecast, oil detection and so on.

low power; low noise; fully differential circuit; folded cascode; common mode feedback; layout

10.14106/j.cnki.1001-2028.2017.11.007

TN43

A

1001-2028(2017)11-0038-05

2017-09-26

金湘亮

国家自然科学基金资助项目(No. 61274043; No. 61233010)

金湘亮(1972-),男,湖南邵阳人,教授,主要从事传感器、集成电路电路研究与设计,E-mail: jinxl@xtu.edu.cn ;

张航(1993-),男,湖北仙桃人,研究生,研究方向为模拟集成电路设计,E-mail: zhanghang_jiayou@163.com 。

2017-11-02 15:46

网络出版地址: http://kns.cnki.net/kcms/detail/51.1241.TN.20171102.1546.006.html