平面螺旋电感优化设计方法

吴 迪,杨格亮,李 斌

(中国电子科技集团公司 第五十四研究所,河北 石家庄 050081)

平面螺旋电感优化设计方法

吴 迪,杨格亮,李 斌

(中国电子科技集团公司 第五十四研究所,河北 石家庄 050081)

平面螺旋电感是射频集成电路中广泛应用的重要器件,它决定着一些组成关键电路的主要性能指标,因此对于平面螺旋电感进行优化设计显得极为重要.文章主要介绍通过对比研究片上螺旋电感参考地的布图方式、参考地的宽度和参考地距离中心线圈的距离等3个方面的不同配置对片上螺旋电感的影响来研究参考地的优化设计.电磁场仿真结果显示,参考地的引入会降低电感的感值L、恶化电感的品质因子Q,参考地越窄或者参考地越远,电感的感值越大,Q值越高,因此,可以通过配置参考地实现片上螺旋电感的优化设计.

集成电路;平面螺旋电感;感值;品质因子;参考地

0 引言

在集成电路设计领域,由于半导体集成电路的高速发展,高度集成的射频芯片正在逐渐代替以往用分立元件实现的射频电子电路,因为电路中有源器件本来就容易集成,所以无源器件能否高度集成自然成为了实现射频芯片高度集成的主要重难点,无源器件实现高集成度主要有以下几个优点,从成本上来说,通常情况下在PCB板上有源晶体管、无源电阻、电容和电感之间的成本依次相差10倍,而射频电路的重要组成部分恰恰是在射频电路中占比例小而成本较低的无源器件如电感、电容和电阻,更为关键的一点是当电容和电感可以实现片上集成时,那么射频电路中就很容易在片内实现电路的输入输出匹配以降低信号的反射,从而减少了片外设计,降低了设计和制造成本;功耗方面,当无源器件实现高集成度时,芯片的管脚引线和PCB板上的连线会大大减少,也因此降低了因为这些连线而导致的信号损耗,从而降低了功耗;芯片面积方面,PCB板上电路被分立无源器件占用了大部分的面积,因此整合板上的分立无源器件,仅用一块IC实现他们的功能便成了实现电子产品小型化的一种可行性方法;可靠性方面,高集成度的射频芯片将本应该焊接在PCB板上的元器件全都实现了芯片内部集成,从而减少了PCB板上的焊接点,进而使得由于焊接点虚焊而产生较大寄生效应的几率降低,增强了系统可靠性;电路设计方面,当芯片高度集成时,就可以实现无源器件的片内匹配,从而设计人员可以更加灵活的设计芯片内部电路和片外电路.总之,无源器件实现高集成度既可以降低PCB板的电路成本,还可以减少由于片外连线而引起的功耗,有利于实现电路的灵活设计、产品小型化并增强系统的可靠性等.而电感的集成又是无源器件实现高度集成化的一个重要方面,因此,集成片上电感的设计与优化成为了射频集成电路设计的一个重要课题.

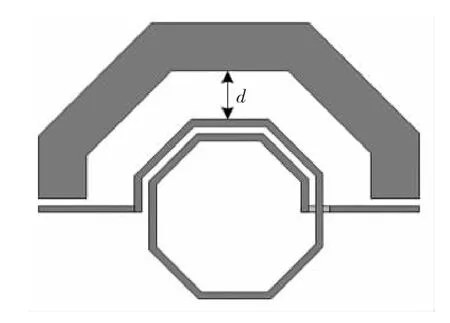

应用场合的不同对电感器感值的要求也不尽相同,为了满足电路对感值的要求和节省芯片面积,通常会采用平面螺旋结构来设计电感器件.而这种结构又根据采用工艺的不同可以通过如下3种方式实现,即:四边形、八边行形和圆形,如图1所示.

目前,国内外研究平面螺旋电感优化设计的基础在于对硅基无源器件损耗机理的认识,这种损耗主要有3个来源[1]:介质的极化损耗、金属的欧姆损耗和半导体硅衬底与金属电磁耦合形成的损耗.据此,可以采用几种方法来优化电感的感值L和品质因子Q,如降低金属的欧姆损耗以优化电感的Q值,如:增加线宽[2]、导线使用高电导率金属[3]、多层金属并联[4]等;或通过设置屏蔽层在电感的下方来降低电感由于金属和衬底之间耦合而带来的损耗[5];抑或改变元件的形状[6],这种方案利用的是在面积一定的情况下,形状越接近圆形的正多边形周长越小的原理.然而,在这种情况下,虽然器件的Q值得到了提升,L值却下降了.近几年,国内外对于平面螺旋电感的研究从未停下脚步,也取得了较为显著的进展.2014年北京理工大学地卢冲赢等人通过采用铜金属悬浮线圈结构减小了片上螺旋电感损耗因素,显著提高了片上螺旋电感地品质因子Q值[12].2015年,印度的Vasu Pulijala等人提出了将Permalloy合金与螺旋电感相结合,通过调节Permalloy合金的厚度,形状和面积来调节电感的感值和品质因子,可以将感值的峰值提升200%,品质因子的峰值提升700%,但这种结构的缺点是成本过高[14].2016年天津大学的徐艳萌等人提出了基于低成本塑料基体制作地柔性螺旋电感,相比于传统的地硅基平面螺旋电感,在高频时柔性螺旋电感的品质因子要更高,这是由于柔性衬底属于绝缘性衬底,大大减小了衬底损耗[13].同年,马来西亚大学地Chee-Cheow Lim等人提出了一种基于硅基螺旋电感地双层模式屏蔽技术,通过最优地利用2个最底层地金属层,使电感屏蔽了基板的影响,电感的品质因子提升了40%[15].与前人的研究相比,本文则研究电感线圈周围铺放的“参考地”对电感的L值和Q值产生的影响,通过配置参考地达到平面螺旋电感优化设计的目的,不加入其他结构与材料,研究更为直接,简单,应用更为广泛.

图1 平面螺旋电感的3种实现方式Fig.1 Three implementations of Plate Spiral Inductor

1 参考地的“顺置”与“逆置”

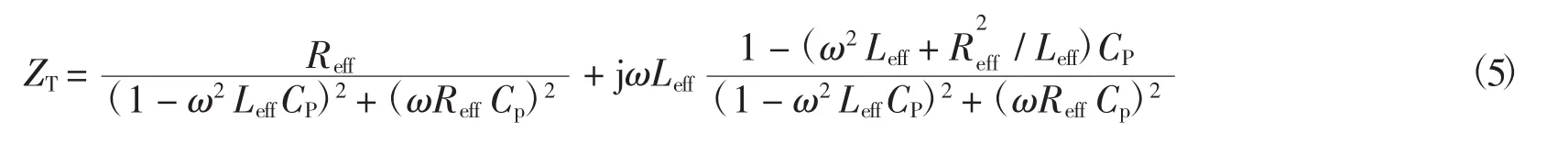

图2所示为电感参考地“顺置”和“逆置”的版图.版图中的箭头指向为电流的流动方向.将“顺置”简单地等效为互感增强变压器,将“逆置”等效为互感削弱型变压器.由空心变压器原理[7]可知,无论“顺置”还是“逆置”,电感的输入阻抗Zin都可以用式(1)表达.图3为2种情况下的仿真结果.

通过整理可以得到电感的等效输入电阻Reff和电感值Leff:

图2 参考地“顺置”和“逆置”的版图Fig.2 Territory of co-phase and anti-phase reference ground

其中:M为电感L1,L2的互感;M1,M2分别为参考地顺置和逆置时的互感;ω为电感的工作角频率,R1,R2为电感的寄生电阻.由式(2) 可知不管参考地“顺置”还是“逆置”,其等效电阻相比与原来的电阻都是增加的,而电感的感值相比于原来的感值都是减小的.在图3中之所以2种情况下的L值和Q值有区别,是因为2种情况下的互感M1和M2并不相同.其中,可以将“逆置”看作是3股线的耦合,而将“顺置”看作是2股线的耦合,因此,“逆置”的互感M2大于“顺置”的互感M1.由式(2)可知,“逆置”时电感的等效电阻大于“顺置”时电感的等效电阻,而其等效电感则小于“顺置”的等效电感.由于电感值的减小引起了自谐振频率的上升,因此在高频时,参考地“逆置”电感的Q值要高于“顺置”电感的Q值.由此可知,参考地的存在尤其是接地环的存在会降低片上电感的感值、恶化电感的品质因子.

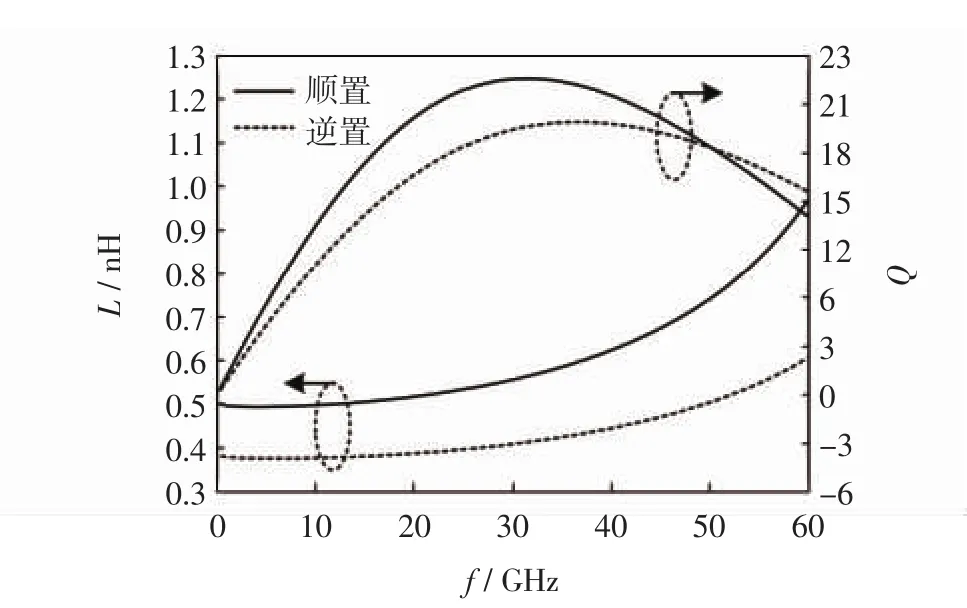

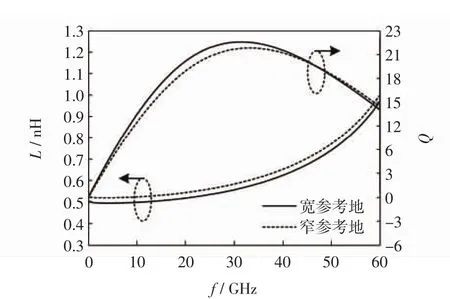

2 参考地的宽度对电感的影响

参考地的宽窄之分就是指当参考地自感不变时自身电阻大小发生的变化.当参考地较窄时,式(2)中的R2较大;而当参考地较宽时,R2较小.因此,可以证明,当ωL2<R2时,R2小,因此Reff小,Leff小,也就是说参考地越宽,L值越小;而参考地越窄,L值越大.但根据定义可以知道,Q值的大小的变化并不会表现出一个固定的趋势.图4和图5给出了宽参考地和窄参考地情况下的版图和仿真结果.由仿真结果可以看出,参考地宽窄对电感L值产生的影响与本文上面的分析相吻合,而Q值在频率的升高时呈现出不固定的规律,这依然与之前的分析相吻合.

3 参考地的距离对电感的影响

参考地与电感的主线圈之间同时有磁场之间的相互作用以及电场之间的相互作用,而电场的相互作用主要通过参考地和主线圈的耦合电容来表现.为了让本文的研究更具针对性,此处暂时忽略衬底和介质的影响.图6所示为包含CP时的螺旋电感的简单等效电路,Reff和Leff分别为等效电阻和电感.

根据图6,得出该电路的阻抗为

将式(4) 整理后得

图3 “顺置”和“逆置”电感的仿真结果Fig.3 Simulation results of inductor with co-phase and anti-phase reference ground

图4 宽参考地和窄参考地对应的电感Fig.4 Inductor with wide and narrow reference ground

图5 宽参考地和窄参考地对应的电感仿真结果Fig.5 Simulation results of inductor with wide and narrow reference ground

图6 平面螺旋电感的简单等效电路Fig.6 Simple equivalent circuit of Plate Spiral Inductor

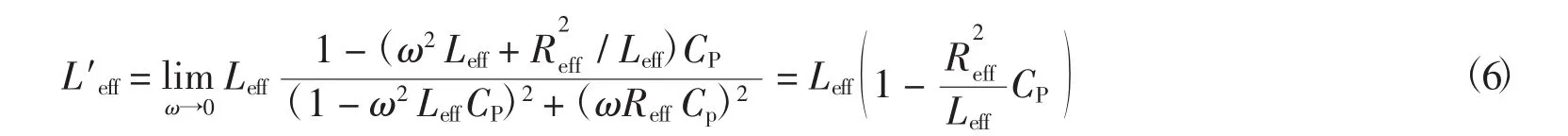

式中,CP为电感线圈与参考地之间的耦合电容.由式(5)可知网络因为耦合电容CP的引入而有了谐振点,其自谐振角频率ωsr=1/(Leff×CP)-1/2.此外,从式(5)的虚部可以看出电路的等效电感也发生了一些变化.为了可以更加直观的观察这种变化,可以观察一下处于自谐振频率以内的较低频率所对应的等效电感的感值L′eff

式(6) 说明电感在低频时的感值L′eff因为耦合电容CP的存在而有所降低,并且CP越大这种下降表现的越明显.同时,电路的Q值也由式(5)决定,即

其中,Q0=ωLeff/Reff由式(2) 和式(3) 决定.从式(7) 可以看出由于CP的存在也使得电路总的Q值下降.为了验证上述得出的结论的是否准确,设计如图7所示的电感并仿真在线圈与参考地之间的间距d不同时所对应的L值和Q值.仿真结果分别如图8和图9所示.

在图7中,可以明显的通过感值的仿真结果观察到自谐振频率fsr随线圈与参考地之间的间距d变化时的变化,即:d越小fsr越低,而d越大fsr越高.通过对低频时电感感值的放大可以看出,当d增大时电感感值也会随之变大.而观察Q值的仿真结果则可以得出随着d的增大Q值也会随之升高.由于d的变化与CP的大小成反比,因此可以得出这些仿真结果与前文的结论是吻合的.

图7~图9所示为当参考地“逆置”时的一系列电感样本.其实在参考地“顺置”的情况下电感也会表现出相同的规律,但比不上“逆置”时的规律明显.但是当考察因子的实际大小时,会发现它的数量级在10-4~10-3之间,这就说明CP的变化不会对电感的L值和Q值产生较大的影响.因此,应当将图8和图9所示L值和Q值的变化归于互感的变化.根据式(2) 和式(3),可以得知当d变大时M变小,所以Leff变大Reff变小从而导致Q值变大;当d变小时则呈现相反的规律.

因此,通过对之前的讨论进行总结可以得出:电感性能受参考地远近的影响主要有两个方面的原因,分别是电场相互作用和磁场的相互作用.电场相互作用主要影响电感的自谐振频率,参考地越远自谐振频率越高,参考地越近自谐振频率越低;磁场相互作用主要影响电感的L值和Q值,参考地越远,L值越大、Q值越高,而参考地越近,L值越小、Q值越低.

图7 参考地与线圈间距为dFig.7 Distance between reference ground and coil d

图8 d取不同值时感值随频率的变化Fig.8 Changes in inductance with frequency of different d

图9 d取不同值时Q值随频率的变化Fig.9 Changes in quality with frequency of different d

4 小结

本文主要研究了电感在平面螺旋参考地在分别以不同布图方式、宽度和距离主线圈远近的情况下产生的变化,通过分析和仿真总结了参考地在不同配置情况下对电感性能的影响,即:参考地的引入会降低电感的感值、恶化电感的品质因子;参考地越窄,电感的L值越大,而参考地越宽,电感的L值越小;参考地越近,电感的L值越小、Q值越低,而参考地越远,电感的L值越大,Q值越高.利用这些规律可以实现射频集成电路中片上平面螺旋电感的优化设计.

[1] Arcioni P,Castello R,Perregrini L,et al.An innovative modelization of loss mechanism in silicon integrated inductors[J].IEEE Transactions on Circuits and Systems—II:Analog and Digital Signal Processing,1999,46(12):1453-1460.

[2] Sia C B,Ong B H,Chan K W,et al.Physical layout design optimization of integrated spiral inductors for silicon-based RFIC applications[J].IEEE Transactions on Electron Devices,2005,52(12):2559-2567.

[3] Burghartz J N,Edelstein D C,Jenkins K A,et al.Monolithic spiral inductors fabricated using a VLSI Cu damascene interconnect technology and lowloss substrates[C]//International of Electron Devices Meeting,San Francisco:IEDM Press,1996:99-102.

[4] Burghartz J N,Soyuer M,Jenkins K A,et al.High-Q inductors in standard silicon interconnect technology and its application to an integrated RF power amplifier[C]//International of Electron Devices Meeting,Washington:IEDM Press,1995:1015-1018.

[5] Yue C P,Wong S S.On-chip spiral inductors with patterned ground shields for Si-based RF IC’s[J].IEEE Journal of Solid-State Circuits,1998,33(5):743-752.

[6] Rasidah S,Siti Maisurah M H,Nazif E F,et al.The design of ground shield spiral inductor using 0.13um CMOS technology for millimeter-wave radio over fiber applications[C]//IEEE Regional Symposium on Micro and Nanoelectronics(RSM),2015:1-4.

[7]Ito H,Masuy K.Simple through-only de-embedding method for no-wafer S-parameter measurements up to 110 GHz[C]//IEEE Microwave Symposium Digest,2008:383-386.

[8] Shilimkar V S,Kabir H,Zhang L,et al.Equivalent Circuit Modeling of On-Chip Inductors using Feature-based Optimization[C]//IEEE 16th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems,2016:27-30.

[9] 王惠娟,潘杰,任晓黎,等.用于射频集成的高Q硅基电感的优化设计[J].现代电子技术,2015,38(18):106-109.

[10]Yim S M,Chen T,Kennth K O.The effects of a ground shield on the characteristics and performance of spiral inductors[J].IEEE Journal of Solid-State Circuits,2002,37(2):237-244.

[11]Yook J M,Kim D and Kim J C.High-performance RF inductors and capacitors using the reverse trench structure of silicon[J].IEEE Microwave and Wireless Components Letters,2015,25(11):709-711.

[12]卢冲赢,徐立新,等.CMOS兼容高Q值微机电系统悬浮片上螺旋电感[J].兵工学报,2014,35(5):634-639.

[13]徐艳蒙,秦国轩;柔性螺旋电感的射频特征分析及建模表征[J].电子测量与技术,2016,39(6):5-8.

[14]Vasu P,Azedmuddin S.Performance boost of spiral inductors with thickness-controlled domin-patterned permalloy[J].Magnetics,IEEE Transactions on,2015:DOI 10.1109/TMAG.2015.2388678.

[15]Lim C C,Ramiah H.A high-Q sprial inductor with dual-layer patterned floating shied in a class-B VCO achieving a 190.65dBc/HZ FOM[C]//2016 IEEE International Symposium on Circuits and Systems(ISCAS),2016:2759-2762.

[16]Ronadl L H,Shoba K.Sprial inductors with floating low-loss RF shields for LC resonator applications[J].Components,Packaging and Manufacturing Technology,IEEE Transactions on,2015,5(9):1300-1312.

Plate spiral inductor optimization design method

WU Di,YANG Geliang,LI Bin

(The 54thResearch Institute of China Electronics Technology Group Corp,Hebei Shijiazhuang 050081,China)

Planar spiral inductors are critical components widely used in radio-frequency integrated circuits(RFICs).They determine the main performance indicator of many key constituent circuits,so it is very important to optimize the design of planar spiral inductors.The paper illustrates the optimization techniques of the planar spiral inductor design by comparing the different configuration of the following three aspects,the layout of the on-chip spiral inductance reference ground,the width of the reference ground and the distance from the reference center to the center coil.The electro-magnetic simulation results show that the reference ground willreduce the inductance and deterioratethe inductor quality of factor Q.If reference ground is narrower or farther away from the central coil,the inductance and quality factor Q of the inductor will increase.Therefore,the optimal design of the on-chip spiral inductors can be achieved by configuring the reference ground.

integrated circuit(IC);plate spiral inductor;inductance;quality factor;reference ground

TN432

A

1007-2373(2017) 05-0023-05

10.14081/j.cnki.hgdxb.2017.05.004

2017-06-01

“十三五”预研项目(31513030301-6)

吴迪(1994-),男,硕士研究生.

[责任编辑 代俊秋]