叶尖间隙微波测量系统中数字下变频设计

查祥胜,吴娅辉

(中国航空工业集团公司北京长城计量测试技术研究所 计量与校准技术重点实验室,北京 100095)

叶尖间隙微波测量系统中数字下变频设计

查祥胜,吴娅辉

(中国航空工业集团公司北京长城计量测试技术研究所 计量与校准技术重点实验室,北京 100095)

叶尖间隙微波测量法是基于相位差原理的微距测量方法,通过测量微波传感器到叶片尖端的发射信号与回波信号的相位差,计算叶尖间隙。为了测量发射信号与回波信号间的相位差,设计了一种数字下变频(DDC)模块,该模块用于解调叶尖间隙微波测量系统中接收机输出的中频回波信号和回波补偿信号以及系统中的中频参考信号。测量系统根据解调后的I/Q信号计算信号的相位和相位差。DDC模块采用低通滤波法实现,并在System Generator开发环境中完成了设计和仿真验证。仿真结果证明DDC模块能够完成输入中频信号的解调,并对解调后的I/Q信号进行10倍抽取,该模块在微波叶尖间隙测量系统中有较大的工程实用价值。

叶尖间隙;微波测量;中频信号;数字下变频

0 引言

目前叶尖间隙的测量方法主要有:放电探针测量法、电涡流测量法、电容测量法、超声波测量法、激光测量法、光纤测量法、X射线测量法和微波测量法等[2-3]。由于发动机工作时工况条件复杂,要求测量叶尖间隙的传感器不受发动机工作时的高温、燃烧产物等不利因素影响,以确保测量结果稳定可靠。针对发动机叶尖间隙测量设计的微波传感器不易受发动机内部高温和燃烧产物的影响,比较适合发动机叶尖间隙测量[4]。使用微波传感器测量叶尖间隙是叶尖间隙测量领域的新尝试。在叶尖间隙微波测量系统中,微波传感器发出24 GHz的连续波,由于叶片振动、多普勒效应等因素的影响,使得接收的回波信号有一定的带宽。为了补偿回波信号在接收线路上的相位变化,在测量系统中引入了回波补偿信号。回波信号和回波补偿信号在接收机中经过模拟下变频处理后得到了中频回波信号和中频回波补偿信号。可通过解调中频回波信号、中频补偿回波信号以及携带初相位信息的参考信号,计算发射信号和回波信号的相位和相位差,求取发动机的叶尖间隙值。

数字下变频[5-7](Digital Down-Converter,DDC)是一种降低数据率的有效方法[8-10]。它将数字化的中频信号转换到基带,并进行信号抽取,在保证信号携带信息不损失的前提下降低了数据率,提高了系统实时处理能力[11]。目前,数字下变频技术广泛应用于无线通信及雷达信号处理等领域。微波叶尖间隙测量系统类似于小型的测距雷达[12],系统中接收机输出的中频信号采样后数据量较大,接近2 GB/s,为了满足系统实时处理的要求,在系统设计中引入了数字下变频技术。

根据叶尖间隙微波测量系统的特点,设计了一种三通道的数字下变频模块,有效地完成了中频数字信号的降采样和相位解调。最后通过System Generator开发环境完成了仿真验证[13-17]。

1 数字下变频结构

低通滤波法是一种典型的数字下变频方法,结构如图1所示。该结构主要由3部分组成:信号采样部分、混频部分和抽取滤波部分。

图1 数字下变频结构

图1中的数控振荡器(Numeric Control Oscillator,NCO)产生正交的正弦和余弦信号,与采样后的中频信号混频。抽取滤波部分用于抽取混频后的信号,降低采样速率;同时滤出带外信号,防止抽取后信号的频谱发生混叠。抽取滤波本质上是使用低通滤波器实现信号的下采样。

在微波叶尖间隙测量系统中,接收机输出的中频信号带宽为6 MHz,中心频率为300 MHz,信号的载波频率是信号带宽的50倍,根据香农采样定律,要求中频信号的采样频率不低于606 MHz。如果采用带通采样,中频信号的采样频率只需要大于信号带宽的2倍即可。假设带通信号x(t)的频率范围是[fL,fH],带宽B=(fH-fL),其中fL和fH分别为带通信号的频率下限和频率上限,为了保证带通采样后频谱不发生混叠,带通采样频率fS需要满足式(1):

(1)

式中,N表示带通信号的频谱和它的镜像频谱之间在无混叠情况下最多能容纳的带通信号的频谱个数,其中N取整数,取值范围从0~[fH/B],[]为取整符号。根据中频信号带宽和式(1),在叶尖间隙微波测量系统中选取中频信号的采样频率为240 MHz。采样后的信号分别与数控振荡器产生的正弦和余弦信号混频,可将中频信号的频谱搬移到零中频。最后在低通滤波器中完成信号抽取,达到信号速率降低的目的。

2 数字下变频模块设计

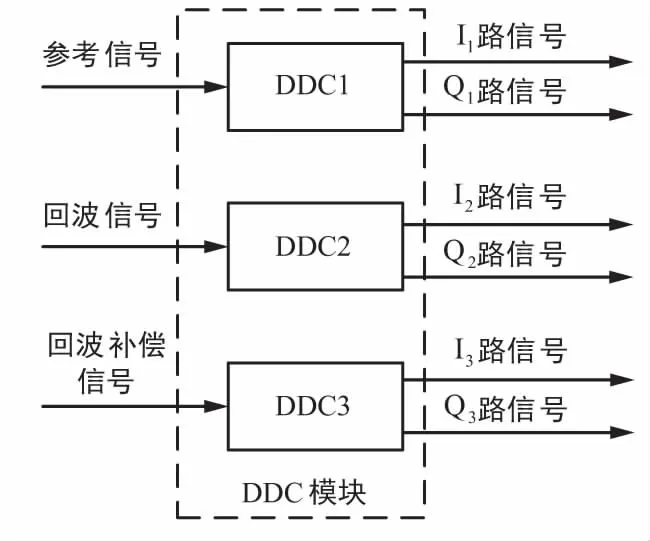

叶尖间隙微波测量系统中的数字下变频模块要求完成三路中频信号的解调,并对解调后的I/Q信号进行10倍抽取,如图2所示。

图2 叶尖间隙微波测量系统中的DDC模块

图中输入的参考信号、回波信号以及回波补偿信号带宽均为6 MHz,中心频率为300 MHz。由于三路中频信号的中心频率和带宽相同,抽取倍数相同,下面将以回波信号为例,具体说明数字下变频模块的设计过程。

低通滤波法解调中频信号时,由于产生正交的正弦、余弦信号和混频的过程都是通过数学运算完成,并且使用的抽取滤波器相同,因此I/Q信号有很好的一致性和正交性。设计中采用低通滤波法设计数字下变频模块。参照图1中的数字下变频结构,在System Generator开发环境中分别实现数控振荡器、信号混频和抽取滤波器。

2.1 数控振荡器设计

NCO通常采用频率合成(Direct Digital Synthesizer,DDS)技术实现。使用DDS生成正弦和余弦信号时,可选用查表法和坐标旋转数字算法(Coordinate Rotation Digital Computer,CORDIC),这2种方法各有优缺点。其中查表法设计简单、输出信号延时小,但会消耗更多的存储资源。而使用CORDIC算法设计具有相同频率分辨率的NCO时,存储资源消耗较少,但是信号生成过程中运算复杂,增加了输出信号的延时。由于合成的正弦和余弦信号波形具有对称性,设计中使用对称性压缩存储波形算法优化传统的查表法结构,在保证NCO生成信号快速性的同时减小波形存储器的容量。压缩波形存储后的NCO结构如图3所示,由相位累加器、相位转换器、波形存储器、幅值转换器和幅值极性控制器组成。

图3 基于压缩波形存储算法的NCO结构

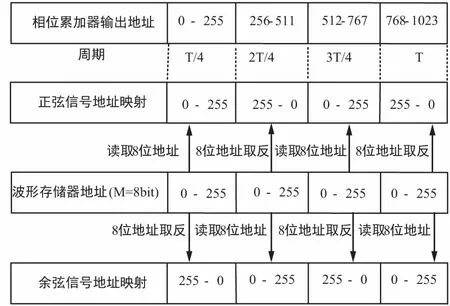

图3中,μ为频率控制字,M为波形存储器的地址数据位宽,fc为参考时钟,通常是一个高稳定度的时钟源,在NCO中作为同步时钟。文中设计的NCO模块需要合成的本振信号频率为fo=60 MHz。相位累加器输出的数据位宽为10 bit,由于波形存储器只存储0~1/4周期正弦信号的波形,因此波形存储器输入地址的数据位宽M=8 bit。在相位转换器中取相位累加器输出数据的低8位作为波形存储器地址。与传统的查表法结构相比波形存储器的容量降低为原来的1/4,压缩波形存储算法的实现过程可由图4说明。

图4 正弦和余弦信号地址映射

图4中相位累加器输出地址范围是[0,1 023],分别对应着一个周期内正弦波上不同的幅值和相位。对于生成周期为T的正弦信号,当相位累加器输出位于区间[0,255],即[0,T/4]时,相位转换器取相位累加器输出地址的低8位作为波形存储器的地址;当相位累加器输出位于区间[256,511],即(T/4,2T/4]时,相位转换器先将相位累加器输出的低8位地址取反后,再作为波形存储器的地址输出;当相位累加器输出位于区间[512,767],即(2T/4,3T/4]时,相位转换器也是直接取相位累加器输出地址的低8位,作为波形存储器地址;当相位累加器输出位于区间[768,1023],即(3T/4,T]时,相位转换器先将相位累加器输出地址的低8位取反后,再作为波形存储器的地址输出。上述过程将波形存储器中存储的波形经过变换后,分别平移到[0,T/4]、(T/4,2T/4]、(2T/4,3T/4]和(3T/4,T]的区间上。余弦信号也按照类似过程产生。在相位累加器输出的10 bit数据中,高2位决定了输出的正弦和余弦波幅值的极性。当最高位为0时,输出的正弦信号幅值为正,反之为负。当最高位与次高位作异或运算,输出值为0时,输出的余弦信号幅值为正,反之为负。

文中基于对称性压缩存储波形算法设计的NCO模块,使用System Generator软件仿真后,合成的正弦和余弦信号的中心频率误差为0.02 MHz。

2.2 抽取滤波器组设计

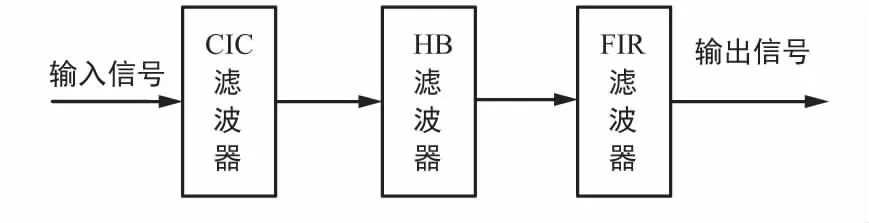

混频后中频信号频谱搬移到了零中频,抽取滤波器组分别对I/Q信号进行降采样和抗混叠滤波。由于输入的中频数字信号采样频率为240 MHz,信号带宽为6 MHz,为了保证抽取后的I/Q信号不失真,根据带通采样定理,抽取后的I/Q信号采样率必须大于2倍的信号带宽。设计中抽取滤波器组的抽取率为10,抽取后的I/Q信号采样率为24 MHz,是信号带宽的4倍。由于中频信号的采样率很高,如果使用单个低通滤波器完成10倍抽取,当设计的滤波器过渡带较窄、阻带衰减较大时,需要滤波器的阶数很高,实现难度大。而使用多级低通滤波器分级抽取可避免这些问题。

级联积分梳状(Cascaded Integrator Comb,CIC)滤波器具有低通滤波器的特性,且滤波器系数均为1,设计时不需要使用乘法器。通常将CIC滤波器用于抽取滤波器组的第一级。因为第一级抽取时,被抽取信号的采样率高,而CIC滤波器的带宽比例因子与信号采样频率成反比关系,而带宽比例因子越小,CIC滤波器的通带纹波越小,阻带衰减越大,即通带和阻带特性越好。半带(Half-Band,HB)滤波器用于实现抽取倍数为2N的抽取。HB滤波器有近一半的滤波器系数为0,因此具有很高的计算效率,适合于信号实时处理。为了减小滤波器组的通带纹波,增大阻带衰减,通常将FIR滤波器作为滤波器组的最后一级。图5为抽取滤波器组的结构。

图5 抽取滤波器组结构

滤波器组中,HB滤波器用于2倍抽取,因此CIC滤波器需要完成5倍抽取。设计中要求CIC滤波器的通带纹波不大于0.01 dB,旁瓣抑制不小于55 dB。理论上单级CIC滤波器的旁瓣抑制为13.46 dB,而N级级联的CIC滤波器旁瓣抑制为(13.46N) dB 。因此,设计中CIC滤波器采用5级级联结构。但多个CIC滤波器级联导致滤波器的通带衰减较大,难以满足通带纹波的要求。为了减少通带衰减,可在CIC滤波器后增加了一级CIC补偿滤波器。采用内插二阶多项式(Interpolated Second-Order Polynomials,ISOP)滤波器作为CIC滤波器的补偿滤波器。ISOP滤波器的频率响应为:

p(ejω)=(1+2cosIω)/c+2,

(2)

式中,c为实数;I表示插值率,其值为正整数。p(ejω)的周期为0,2π/I,在0,π/I内单调递增,正好可以补偿CIC滤波器的通带衰减。假设5阶CIC滤波器的频率响应为H(ejω),抽取倍数为D,通带截止频率为fa, 根据CIC滤波器的通带纹波δ,由关系式(3)优化计算出c和I的值。

(3)

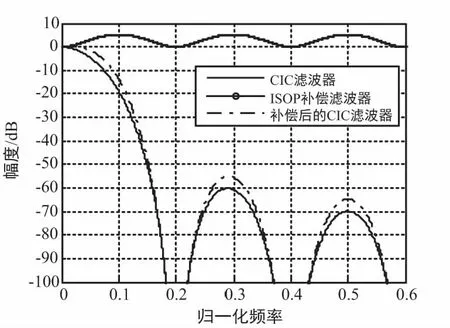

文中设计的ISOP滤波器取(c,I)=(-6.9,5),图6为CIC滤波器、ISOP滤波器以及加入补偿滤波器后的CIC滤波器的幅频特性。比较补偿前后CIC滤波器的幅频响应,其通带衰减由1.1 dB降低到0.01 dB,但旁瓣抑制从60 dB降低到了56 dB。

图6 补偿前后CIC滤波器幅频特性对比

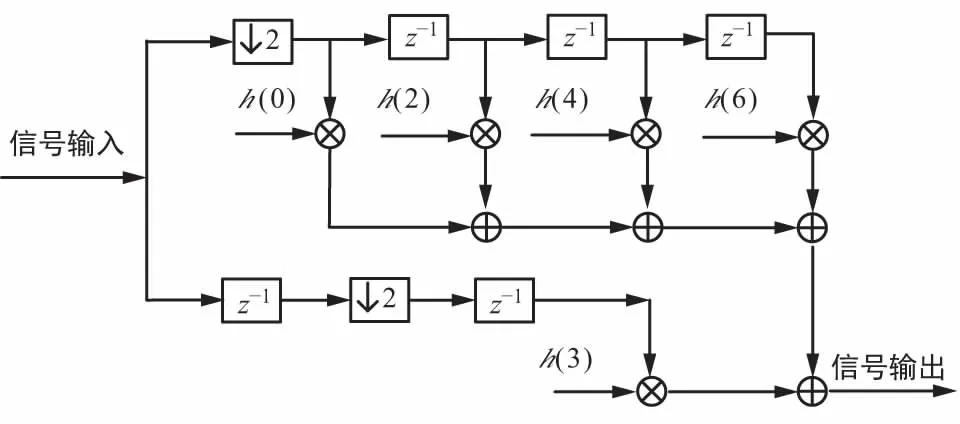

HB滤波器作为抽取滤波器组的第二级,要求完成了2倍的信号抽取。为了提高计算速度,文中将传统的HB滤波器直接型结构优化为多项滤波结构,如图7所示。输入HB滤波器的信号采样频率为48 MHz,信号带宽为6 MHz,通过HB滤波器处理后,信号的采样率下降到24 MHz。设计中根据输入信号的采样频率、滤波器通带截止频率和通带纹波,借助System Generator工具箱 FDA Tool计算HB滤波器系数和最小阶数。

图7 基于多项滤波的HB滤波器结构

滤波器组中的最后一级FIR滤波器,用于信号整形,提高滤波器组的通带和阻带特性,不做信号抽取。设计中要求FIR滤波器通带截止频率为3 MHz,通带纹波不大于0.01 dB,阻带衰减不小于65 dB。借助FDA Tool工具箱,采用窗口函数实现。由于中频信号通过CIC滤波器和HB滤波器抽取后,采样率由原来的240 MHz降到了24 MHz。因此,更容易实现通带纹波小,过渡带窄,阻带衰减大的FIR滤波器。综合整个抽取滤波器组,其脉冲响应的幅频特性如图8所示。图中滤波器组的通带截止频率为3 MHz,通带纹波约为0.01 dB,阻带衰减约为68 dB。

图8 抽取滤波器组幅频特性

3 数字下变频模块仿真验证

System Generator是针对FPGA硬件设计开发的系统级仿真工具,它以工具包的形式嵌入到Simulink仿真环境中,非常适合于数字信号处理系统的仿真验证。

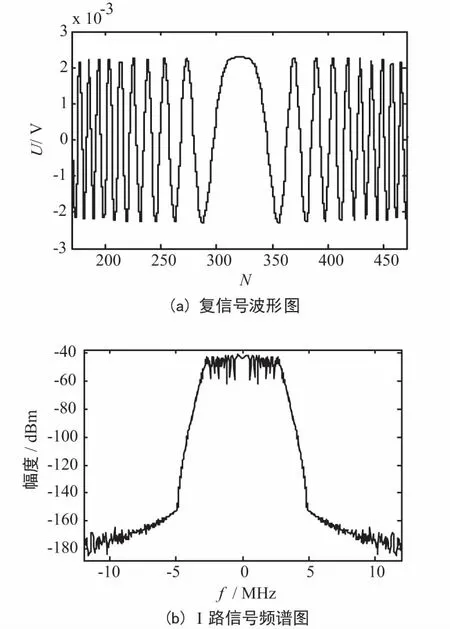

为了验证DDC模块的性能,借助System Generator开发环境,利用仿真工具中的线性调频模块模拟带宽为6 MHz的基带信号。再将基带信号加载到频率为300 MHz正弦和余弦信号上,模拟载波中心频率为300 MHz,带宽为6 MHz,采样频率为240 MHz的中频回波信号。图9为模拟的基带信号波形和频谱。

图9 基带信号波形和频谱

模拟的中频回波信号输入DDC模块,将处理后得到的正交的I/Q信号合并为复信号,复信号波形以及I路信号的频谱如图10所示。

图10(b)中,I路信号的频谱表明,中频回波信号经过DDC模块处理后输出信号带宽仍保持为6 MHz,采样率由240 MHz降低到24 MHz。说明设计的DDC模块实现了中频回波信号解调和10倍抽取。将I/Q信号合成的复信号与最初给定的基带信号相比,解调出来的基带信号保持着原始基带信号的特征,虽然存在能量的损失,但并不影响求取信号的相位。中频参考信号和中频回波补偿信号使用文中设计的DDC模块也可以完成信号解调和抽取。最终,三路中频信号经DDC模块处理后,将输出结果传送到上位机中求取每一路中频信号的相位,并计算发射信号与回波信号的相位差以及叶尖间隙值。由于上位机中信号的处理过程不是本文研究的重点,在此不做过多说明。

图10 复信号波形和I路信号频谱

4 结束语

本文以叶尖间隙微波测量为背景,参考低通滤波法的下变频结构,设计了用于解调中频回波信号、回波补偿信号和参考信号的多通道数字下变频模块。采用了对称性压缩存储波形算法设计数控振荡器,既发挥了查表法快速性的优点,又将波形存储器的容量降低为原来的1/4。并使用低通滤波器组完成了信号抽取,同时为了提高HB滤波器的运算速度将HB滤波器的结构优化为多项滤波结构。最后使用System Generator开发环境实现了DDC模块,并通过模拟叶尖间隙微波测量系统中接收机下变频至中频后的回波信号验证了DDC模块的性能,仿真结果证明DDC模块符合设计要求。

[1] 熊宇飞.转子叶尖间隙测量在风扇和压气机性能试验中的应用[J].航空发动机,2002(1):20-25.

[2] 马玉真.旋转叶片叶尖间隙测量的关键技术研究[D].天津:天津大学,2006.

[3] 黄春峰,侯敏杰.航空发动机叶尖间隙测量技术研究[J].测控技术,2008,27(增刊):27-32.

[4] 谢兴娟,吴娅辉,朱振宇.航空发动机叶尖间隙测试微波传感器设计与计算[J].传感器与微系统,2015,34(5):63-65.

[5] 杨小牛,楼才义,许建良,等.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[6] Liu H M,Li G J,Yan B,et al.A 100 MHz Digital Down Converter with Modified FIR Filter for Wideband Software-Defined Radios[C]∥2010 International Conference on Electronics and Information Engineering (ICEIE 2010).IEEE,2010:V2-540-V2-544.

[7] Zhao K R,Zhang C.A Polyphase Digital Down Converter Method for GHz High Speed Sampling Signal[C]∥2015 12th International Conference on Electronic Measurement & Instruments (ICEMI 2015).IEEE,2015:907-910.

[8] Liu L,Liu G S,Zhang Q.IF Echo Signal Processing Technic in Pulse Compression Radar[C]∥2015 12th International Conference on Electronic Measurement & Instruments (ICEMI 2015).IEEE,2015:1242-1245.

[9] Liu t,Han J Y,Li Z G.Broadband DDC Based on Polyphase Filter and Its FPGA Implementation[C]∥2016 International Conference on Electronic Information and Communication Technology (ICEICT 2016).IEEE,2016:170-173.

[10] 王俊,张玉玺,杨彬.DSP/FPGA嵌入式实时处理技术及应用[M].北京:电子工业出版社,2015.

[11] 王超,谢憬,封成冬.一种高性能数字下变频硬件计算结构[J].信息技术,2014(7):94-97.

[12] Woike M R,Roeder J W,Hughes C E,et al.Testing of a Microwave Blade Tip Clearance Sensor at the NASA GLENN Research Center[C]∥47thAerospace Sciences Meeting.Florida:AIAA,2009:1-14.

[13] 高亚军.基于FPGA的数字信号处理(第2版)[M].北京:电子工业出版社,2015.

[14] 高展宏,王强.多媒体处理FPGA实现System Generator篇[M].北京:电子工业出版社,2010.

[15] 纪志成,高春能.FPGA数字信号处理教程:System Generator入门与提高[M].西安:西安电子科技大学出版社,2008.

[16] 戈弋,黄华,王建忠,等.高功率微波脉冲的相位测量方法初探[J].微波学报,2014(6):494-497.

[17] 薛宸. 基于FPGA的无线移动通信系统多普勒补偿算法[J]. 现代雷达, 2015, 37(7):30-33.

DesignofDigitalDownConverterinMicrowaveMeasurementSystemofTipClearance

ZHA Xiang-sheng,WU Ya-hui

(Key Laboratory of Science and Technology on Metrology and Calibration,Changcheng Institute of Metrology and Measurement, Aviation Industry Corporation of China,Beijing 100095,China)

The method of microwave measurement of tip clearance,based on phase difference principle,is used to measure minute distances.The tip clearance is calculated by measuring the phase difference between the transmitting signal and the echo signal from a microwave sensor to a blade tip.In order to measure the phase difference between the transmitted signal and the echo signal,a digital down converter (DDC) module is designed in this paper.The module is applied to demodulate intermediate frequency (IF) signals including an IF echo signal and an IF echo compensation signal,both coming from the receiver,and an IF reference signal in system.The measurement system calculates the phase and phase difference of these IF signals according to the demodulated I/Q signals.The DDC module is implemented by low-pass filtering method and verified in System Generator development environment.The simulation results show that the DDC module can perform the demodulation of intermediate frequency signals and ten times down sampling of I/Q signals.The module is of great practical value for microwave measurement system of tip clearance.

tip clearance;microwave measurement;intermediate frequency signal;digital down converter

TN911.7

A

1003-3114(2017)06-71-6

10.3969/j.issn.1003-3114.2017.06.18

查祥胜,吴娅辉.叶尖间隙微波测量系统中数字下变频设计[J].无线电通信技术,2017,43(6):71-76.

[ZHA Xiangsheng,WU Yahui.Design of Digital Down Converter in Microwave Measurement System of Tip Clearance[J].Radio Communications Technology,2017,43(6):71-76.]

2017-07-18

查祥胜(1990―),男,硕士研究生,主要研究方向:数字信号处理。吴娅辉(1980―),女,高级工程师,博士,主要研究方向:微波间隙测量技术。