一种具有鲁棒启动行为的自偏置电流模式带隙基准

李政达,黄 鲁

(中国科学技术大学 电子科学与技术系,安徽 合肥 230027)

一种具有鲁棒启动行为的自偏置电流模式带隙基准

李政达,黄 鲁

(中国科学技术大学 电子科学与技术系,安徽 合肥 230027)

在很多应用中,带隙基准需要在很宽的电源电压范围内都能正常工作,而启动电路注入带隙基准的电流大小往往会因为电源电压的变化而受到影响。因此,对带隙基准的启动行为研究变得很重要,尤其对于自偏置电流模式带隙基准,该结构在启动过程中有一段非正常工作区。文章详细分析了影响自偏置电流模式带隙基准正常启动的原因,进而提出一种具有鲁棒启动行为的自偏置电流模式带隙基准,增强了自偏置电流模式带隙基准的启动鲁棒性,同时也简化了启动电路的设计。带隙基准的设计采用65 nm CMOS工艺,温度系数为17.2 ppm/℃,总电流消耗为35 μA。

带隙基准;鲁棒启动;CMOS集成电路

0 引言

带隙基准非常广泛地应用于多种系统和子系统中,例如LDO、DC/DC、ADC和DAC。随着CMOS工艺的尺寸越来越小,低压带隙基准的研究变得越来越重要。一种应用很广泛的低压带隙基准结构由Banba[1]提出,称为电流模式带隙基准,它能工作在接近1 V的电源电压。而且通过曲率补偿,电流模式带隙基准能得到很小的温度系数[2]。但它的缺点是有一段稳定的非正常工作区,启动电路可使该电流模式带隙基准达到正常的工作点。文献[3-4]中对启动电路进行了详细的设计,以确保电流模式带隙基准的正常工作。文献[5]详细分析了电流模式带隙基准具有一段非正常工作区的原因,为了克服这种潜在的启动问题,提出了非平衡电流模式带隙基准。非平衡电流模式带隙基准仅需采用简单的脉冲发生器启动电路便能达到正常的工作点,同时它在很宽的电源电压范围内都能正常工作,但此结构的带隙基准温度系数较差。另外带隙基准中的运放有多种不同结构,文献[6]中为伪差分结构,文献[7]中为外部提供偏置,文献[1,4,8]中则采用自偏置结构,自偏置结构会在运放内部构成一个正反馈环路,但文献[1,4,8]中并未分析自偏置运放对带隙基准启动行为的影响。本文对自偏置电流模式带隙基准进行了详细的理论分析,分析了自偏置运放对带隙基准环路稳定性和启动行为的影响,同时针对电流模式带隙基准潜在的启动问题,提出一种具有鲁棒启动行为的带隙基准。该结构不会额外消耗过多的面积和功耗,也不会如非平衡电流模式带隙基准那样增加带隙基准的温度系数。

1 自偏置电流模式带隙基准

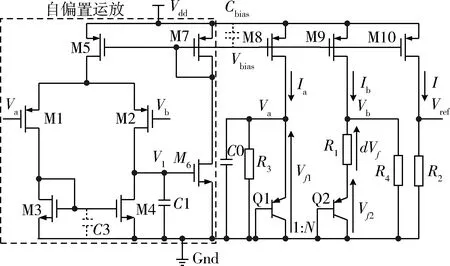

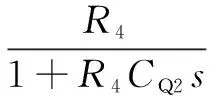

自偏置电流模式带隙基准[1,3]如图1所示。图中,PMOS管M8、M9和M10是完全相同的,同时,电阻R3与R4也是相同的,运算放大器通过反馈回路使得Va点的电压与Vb点的电压相等,这样就使得通过电阻R3和R4的电流相等,通过进一步分析不难得到,带隙基准的参考电压Vref为:

(1)

图1 自偏置电流模式带隙基准

由于带隙基准中运放的偏置电压由自己提供,而且该带隙基准可以得到与温度无关的电流,故将该结构称为自偏置电流模式带隙基准。由于无需额外的偏置电路,该结构的面积更小,功耗更低,而且自偏置运放结构会使带隙基准有更高的低频电源抑制。同时该带隙基准可以得到低于1.2 V的输出电压。

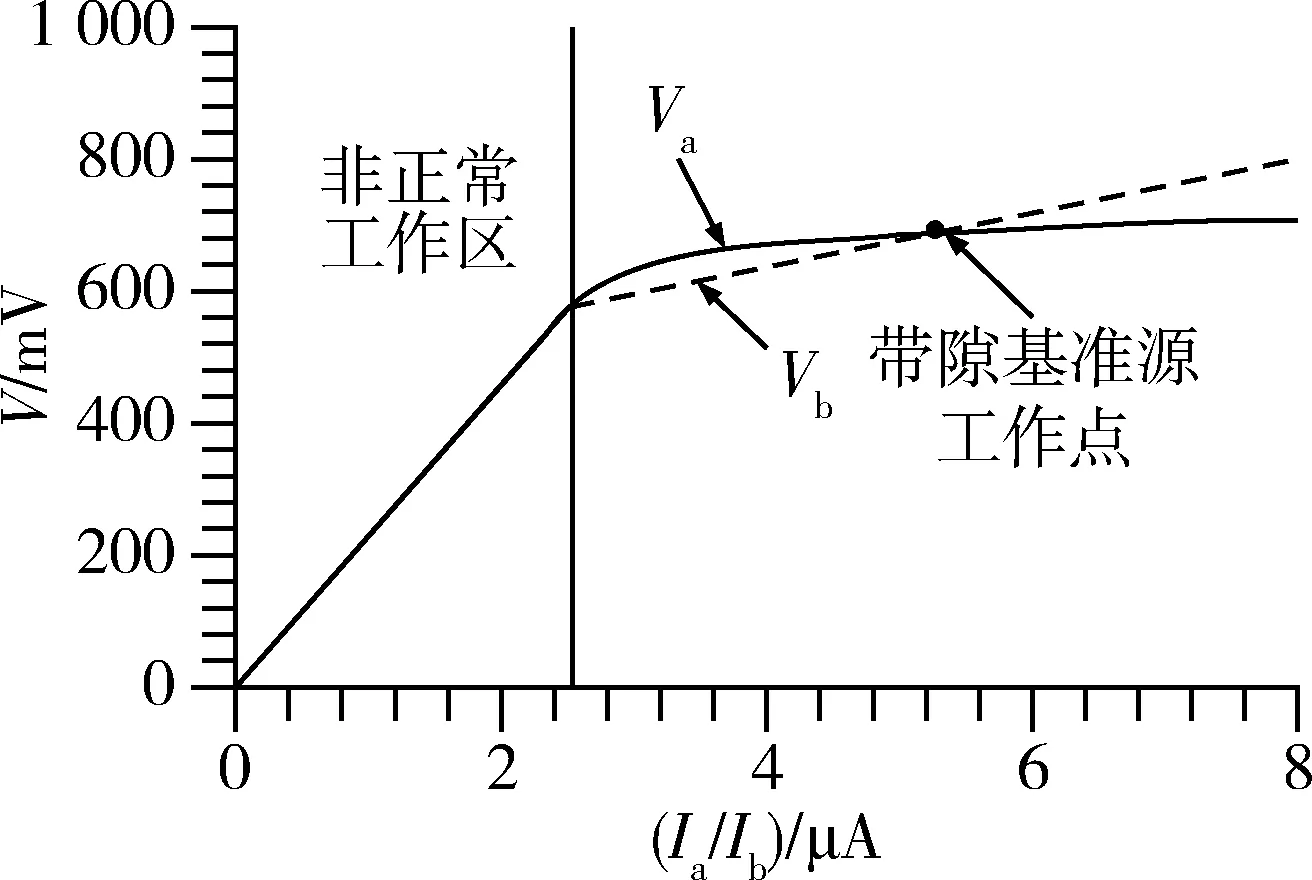

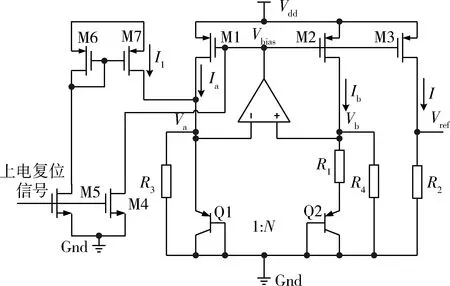

但此结构的问题在于增加了带隙基准的简并点,如图2所示,在该带隙基准启动过程中,当Va和Vb较低时,三极管Q1和Q2处于截止区,M8和M9的电流全流过电阻R3和R4,此时的带隙基准处于非正常的工作状态。这一段非正常工作区将增加带隙基准的启动难度,因为在非正常工作区,Va与Vb相等,此时运放无法帮助带隙基准启动到正常的工作点,完全需要依靠启动电路来使带隙基准脱离这一段非正常工作区。但是在很多应用中,带隙基准需要在很宽的电源电压范围内都能正常工作,而启动电路注入电流的大小会因为电源电压的变化而受到影响,若注入电流过大,带隙基准的输出会产生较大的过冲,若注入电流过小,则无法确保带隙基准脱离非正常工作区。在此情况下,为了确保带隙基准正常工作,在文献[3]中,用一个迟滞比较器来提升启动电路的判断精度和带隙基准的启动鲁棒性,但是此设计增加了启动电路的复杂度和面积功耗。

图2 两条电流支路的电压随注入电流的变化曲线

图3 非平衡自偏置电流模式带隙基准

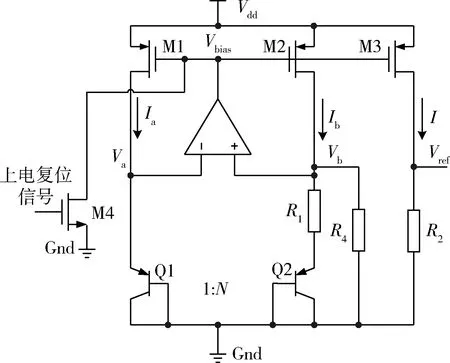

在文献[5]中提出了非平衡电流模式带隙基准,如图3所示,该结构拿掉了带隙基准的电阻R3,消除了低压电流模式带隙基准的非正常工作区,使得此结构的带隙基准仅剩一个电流为0的简并点,大大简化了启动电路的设计,优化了面积和功耗;但由于缺少电阻R3,导致该结构温度系数较差,有41.5 ppm/℃。而且除此之外,以上文献中都并未考虑到自偏置运放中的正反馈对电流模式带隙基准启动行为的影响。

2 一种具有鲁棒启动行为的自偏置电流模式带隙基准

2.1 自偏置运放对电流模式带隙基准启动行为的影响

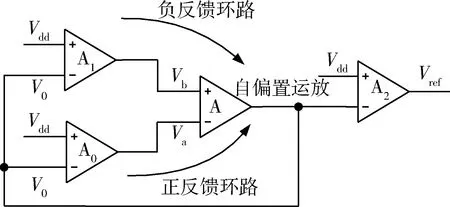

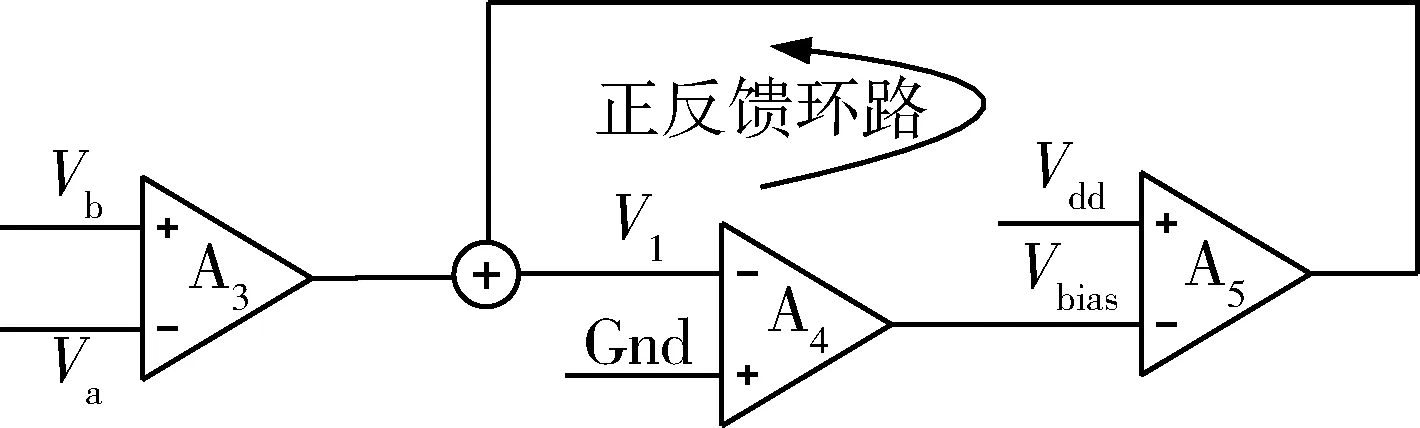

图1为自偏置电流模式带隙基准,该带隙基准的小信号等效框图如图4所示。

图4 自偏置电流模式带隙基准等效框图

图4中:

(2)

(3)

A2(s)=gm10R2

(4)

其中gm8、gm9和gm10指M8、M9和M10的跨导,RQ1和RQ2指三极管Q1和Q2线性区的小信号等效电阻,RQ1=RQ2,CQ1和CQ2指三极管Q1和Q2发射极对地的寄生电容,CQ2≈NCQ1,C0为额外加入的电容,C0≈CQ2-CQ1用于补偿CQ2对环路稳定性的影响。R3=R4,一般都远大于R1、RQ1和RQ2。

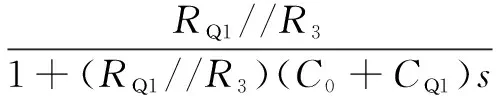

自偏置运放内部还存在一个正反馈环路,为M6→M7→M5→M3,M4→M6,自偏置运放内部电路小信号等效框架如图5所示。

图5 自偏置运放内部电路等效框架

图5中:

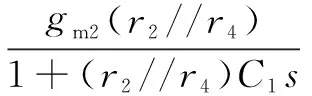

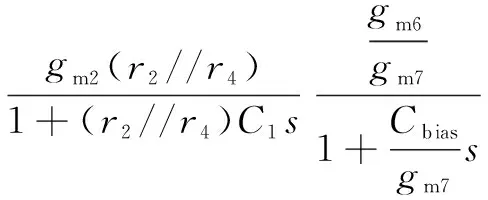

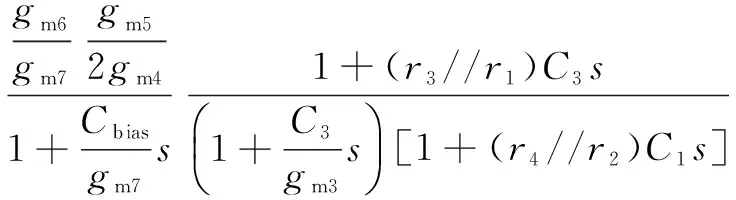

(5)

(6)

(7)

其中gm1~gm7为M1~M7的跨导,gm1=gm2,gm3=gm4,r1~r4指M1~M4的漏源小信号电阻,Cbias指Vbias点对Vdd的总寄生电容,C3指M3管栅极点对Gnd的总寄生电容,C1为额外加入的电容,其作用是为保证带隙基准的环路稳定。

自偏置电流模式带隙基准的负反馈环路增益为:

T负(s)=A3(s)A4(s)[A1(s)-A0(s)]

(8)

自偏置运放内部的正反馈环路增益为:

T正(s)=A4(s)A5(s)

(9)

将式(2)、(3)、(5)、(6)、(7)带入到式(8)、(9)中,可得到:

(10)

(11)

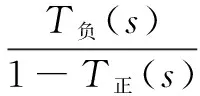

此时,不难得到自偏置电流模式带隙基准的总环路增益:

(12)

(13)

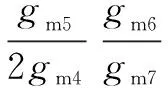

从式(13)中可以看出,当自偏置电流模式带隙基准正常工作时,由于负反馈的强度远大于正反馈的强度,所以即使正反馈的环路增益大于1,该结构仍然稳定。但是,当电流模带隙基准处于非正常工作区时,此时三极管Q1和Q2工作在截止区,可得到:

(14)

(15)

由于三极管Q1和Q2工作在截止区,CQ1和CQ2的值会减小,但C0一般为MOS电容,三极管截止时,MOS电容也处于截止区,电容同样会减小,而R3=R4,故A1(s)-A0(s)≈0。最终将导致T负(s)≈0,此时自偏置运放内部的正反馈将可能会阻止自偏置电流模式带隙基准的正常启动,使得自偏置电流模式带隙基准的启动变得更加困难。

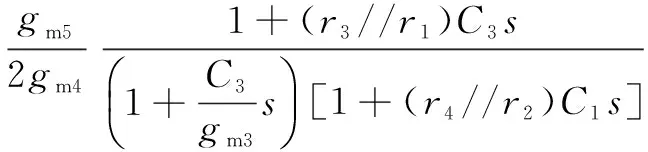

2.2 具有鲁棒启动行为的自偏置电流模式带隙基准设计

自偏置电流模式带隙基准难启动的主要原因是在其启动过程中,Va和Vb相等所产生的一段非正常工作区,而Va和Vb相等的原因是由于R3=R4,文献[3]中将R3拿掉,使得带隙基准启动过程中Va一直大于Vb,消除了电流模式带隙基准的非正常工作区,但缺少R3后使得带隙基准稳态时温度系数变得很差。通过分析可知,只需在此带隙基准启动过程中让Va电压一直大于Vb即可,本文通过在带隙基准启动过程中额外注入电流I1来消除这一段非正常工作区,如图6所示,额外注入的电流I1起到了类似于拿掉R3的作用,但是当带隙基准正常工作时,便不再额外注入电流,此时便不会影响到温度系数。需注意的是,此带隙基准启动过程中,下拉Vbias是必须的,因为运放为自偏置结构,若不下拉Vbias而仅仅往Va中注入电流,运放则无法工作在正常的工作点。

图6 本文提出的具有鲁棒启动行为的自偏置电流模式带隙基准

如图7所示,此时电流模式带隙基准的非正常工作点仅剩下电流为0的简并点,启动电路只需让电流模式带隙基准脱离电流为0的简并点即可,之后运放便会帮助此带隙基准达到正常的工作点,这将大大降低对启动电路判断精度和注入电流精度的要求,提升带隙基准的启动鲁棒性。而且由于额外注入的电流,Q1进入线性区,A1(s)≠A0(s),自偏置运放内部的正反馈对电流模式带隙基准启动影响的问题也得到了解决。此外,额外注入电流I1的方法并非一定需要上电复位信号,其他的启动电路同样也可以达到此目的。

图7 两条电流支路的电压随注入电流的变化曲线

3 电路仿真结果和比较

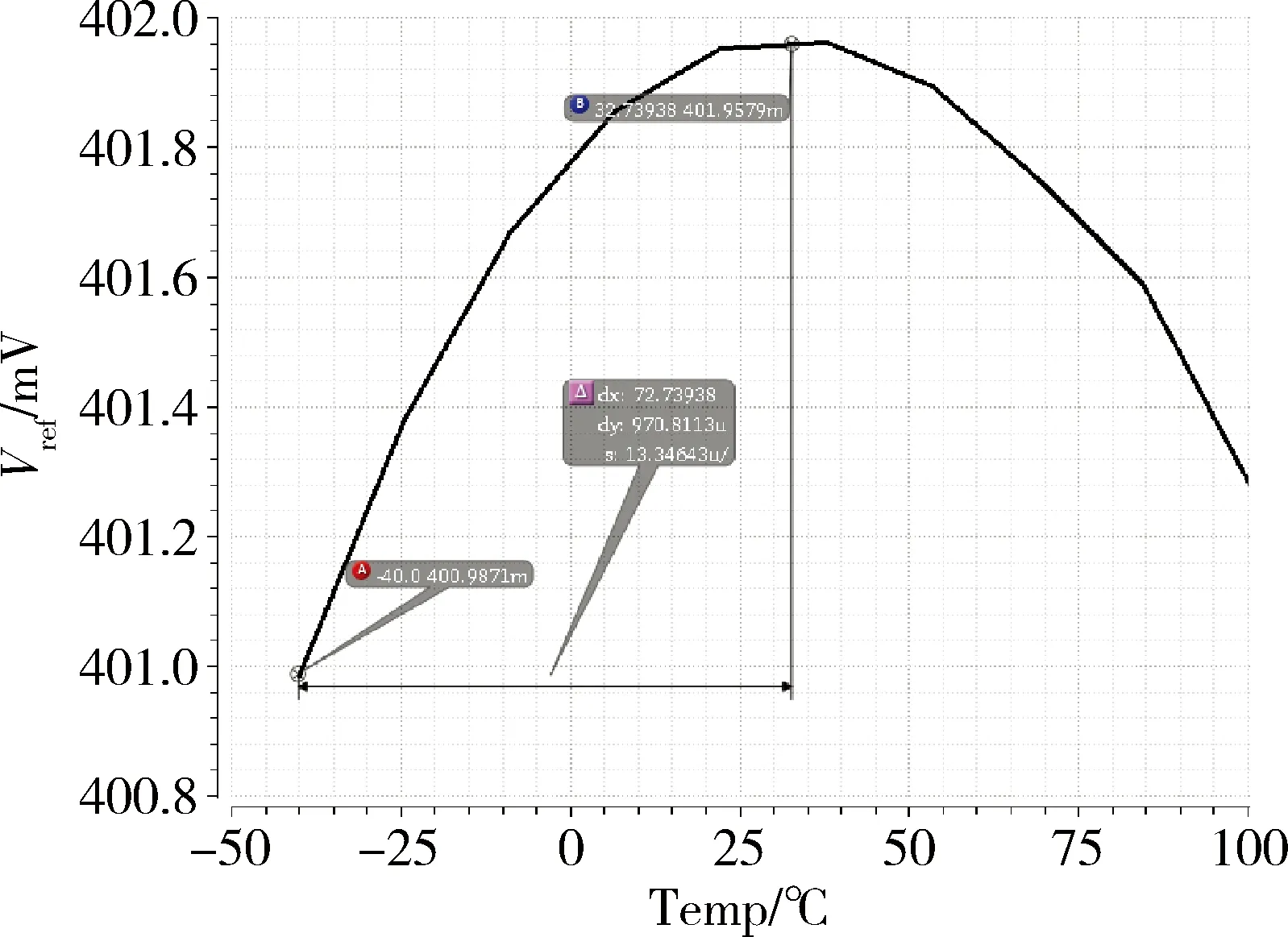

基于SMIC65 CMOS工艺,使用Cadence Spectre工具对电路进行仿真,当电源电压为1.4 V时,基准电压在-40℃~+100℃下温度系数为17.2 ppm/℃。如图8所示。

图8 带隙基准的温度特性

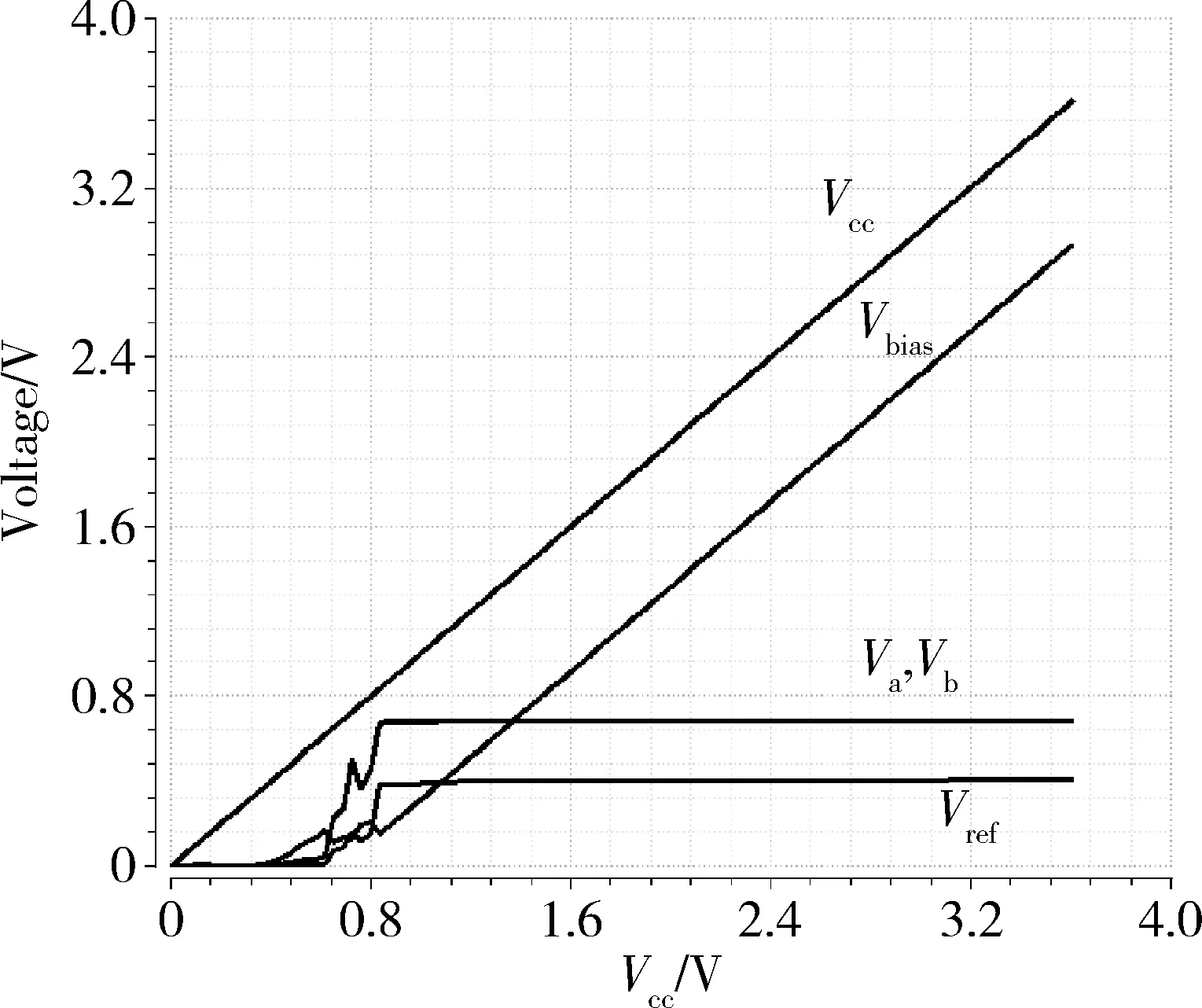

图9为电源电压从0 V~3.6 V时带隙基准的仿真。从图中可以看出,当电源电压为1.4 V~3.6 V时,带隙基准输出电压Vref=400 mV。

图9 宽电源电压下的带隙基准仿真

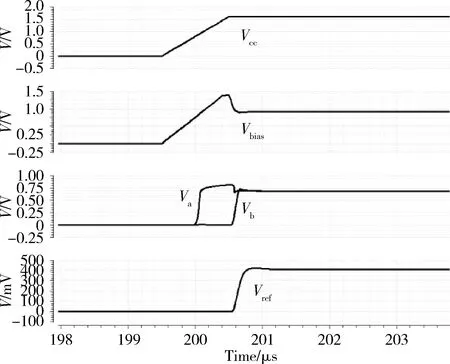

图10 带隙基准启动的瞬态仿真

为了验证此电流模式带隙基准具有鲁棒启动行为,图10给出了带隙基准启动的瞬态仿真,可以看出,在带隙基准启动过程中,Va一直大于Vb,说明此时非正常工作区已经被消除。

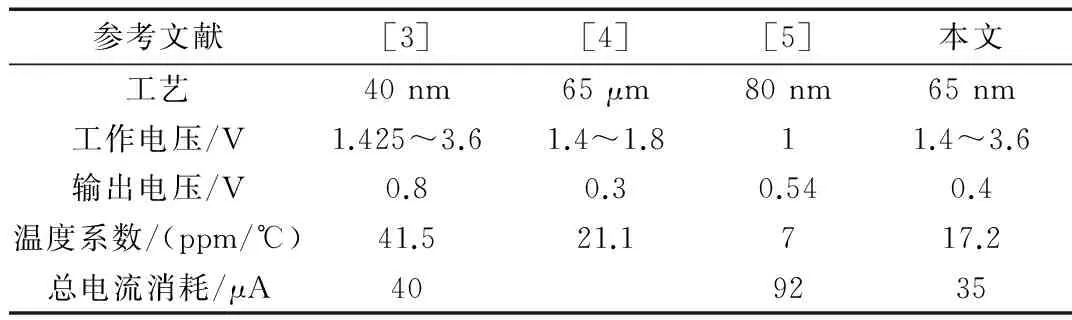

表1给出了本设计和其他设计的比较,文献[5]为非平衡电流模式带隙基准,本文与文献[5]都能在很宽的电源电压范围内正常工作,但文献[5]的温度系数较差,为41.5 ppm/℃,而本文的带隙基准温度系数为17.2 ppm/℃。

表1 本设计与其他设计比较

4 结论

本文基于SMIC 65nm工艺提出了一种具有鲁棒启动行为的自偏置电流模式带隙基准。提升了自偏置电流模式带隙基准的启动鲁棒性,减小了启动电路的设计复杂度,降低了对启动电路判断精度和注入电流精度的要求,使得此带隙基准可以在很宽的电源电压下正常工作,并且也不会影响到带隙基准的温度系数。

[1] BANBA H, SHIGA H, UMEZAWA A, et al. A CMOS bandgap reference circuit with sub-1-V operation[J]. IEEE Journal of Solid-State Circuits, 1999, 34(5): 670-674.

[2] MALCOVATI P, MALOBERTI F, FIOCCHI C, et al. Curvature-compensated BiCMOS bandgap with 1-V supply voltage[J]. IEEE Journal of Solid-State Circuits, 2001, 36(7): 1076-1081.

[3] BONI A. Op-amps and startup circuits for CMOS bandgap references with near 1-V supply[J]. IEEE Journal of Solid-State Circuits, 2002, 37(10): 1339-1343.

[4] CAO T V, WISLAND D T, LANDE T S, et al. Novel start-up circuit with enhanced power-up characteristic for bandgap references[C]. 2008 IEEE International SOC Conference. IEEE, 2008: 123-126.

[5] YU C, SIEK L. An area-efficient current-mode bandgap reference with intrinsic robust start-up behavior[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2015, 62(10): 937-941.

[6] 高云华. 一种发动机高温差环境下的基准电压源电路[J]. 微型机与应用, 2011, 30(15):25-28.

[7] 李睿, 冯全源. 一种低功耗高精度带隙基准的设计[J]. 电子技术应用, 2015, 41(3):51-54.

[8] PERRY R T, LEWIS S H, BROKAW A P, et al. A 1.4 V supply CMOS fractional bandgap reference[J]. IEEE Journal of Solid-State Circuits, 2007, 42(10): 2180-2186.

A self-bias current-mode bandgap reference with robust start-up behavior

Li Zhengda, Huang Lu

(Department of Electronic Science and Technology, University of Science and Technology of China, Hefei 230027, China)

In many applications, the bandgap reference needs to operate over a wide range of supply voltages, the amount of current injected into the bandgap reference by the start-up circuit can be affected by variations in the supply voltage. Therefore, it is important to study the startup behavior of bandgap reference, especially for the low-voltage self-bias current-mode bandgap reference, which has a non-normal operating region. In this paper, the reasons that affect the self-bias current-mode bandgap reference normal startup are analyzed in detail. Then, a self-biased current-mode bandgap reference with robust start-up behavior is proposed, the start-up robustness of the self-biased current-mode bandgap reference is enhanced, and the design of the start-up circuit is simplified. A bandgap reference in 65 nm CMOS process is presented, the temperature coefficient is 17.2 ppm / °C and the total current consumption is 35 μA.

bandgap reference; robust start-up; CMOS integrated circuits

TN492

A

10.19358/j.issn.1674- 7720.2017.13.011

李政达,黄鲁.一种具有鲁棒启动行为的自偏置电流模式带隙基准[J].微型机与应用,2017,36(13):34-37,41.

2017-02-10)

李政达 (1992-),男,硕士研究生,主要研究方向:模拟集成电路设计。

黄鲁(1961-),通信作者,男,副教授,硕士生导师,主要研究方向:混合信号IC芯片设计。

E-mail: luhuang@ustc.edu.cn。