基于O-QPSK传输调制两点合成低功耗ZigBee收发器

蒋惠萍

(青岛理工大学(临沂) 总务部,山东 临沂 273400)

基于O-QPSK传输调制两点合成低功耗ZigBee收发器

蒋惠萍

(青岛理工大学(临沂) 总务部,山东 临沂 273400)

为降低ZigBee收发技术传输能耗,提出基于O-QPSK传输调制两点合成低功耗ZigBee收发器设计方法。首先,针对ZigBee收发器进行架构设计研究,在TX部件内的MAC中根据先入先出(FIFO)方式对传输数据进行选择,提高有效载荷和帧起始符(SFD)字段的长度,并使用O-QPSK调制对传输字符进行处理;其次,重新设计ZigBee收发器关键部件,设计了频率合成器的两点调制方法,并设计了低噪声和功率放大器;最后,通过实验仿真对所设计ZigBee收发器进行了性能验证,显示所提方法在数据传输节能性能以及共存性能上优势明显。

CMOS集成;低能耗;ZigBee收发器;两点合成;O-QPSK调制

0 引言

目前,ZigBee技术因其高效低功耗连接和单一网络的大量设备容纳能力,已广泛应用在各种场合,可实现基于传感器的监测和控制[1-2]。ZigBee与其他无线个人区域网(WPAN)标准相比,具有更低的延迟,同时,因它不需要任何网络同步,可通过自身的加密提供一个高度安全的网络。由于这些特点,可在许多生物医学和医疗领域使用ZigBee技术,如健康监测方面[3]。

由于CMOS原型的ZigBee首先被提出,许多学者对其进行了改进,以实现更高的集成度、更好的性能和较低的功耗[4]。然而,ZigBee需要与其他现有的无线电收发器和蓝牙共享一个2.4 GHz的工业、科学和医疗(ISM)波段。因此,ZigBee与WLAN和蓝牙的共存成为一个日益重要的问题。最近,为了满足各种短距离数据传输标准,有研究实现了多标准的无线电数据传输技术,实现了协议级共存的医疗应用研究[5]。

本文给出了完整的ZigBee实现硬件设计,包括物理(PHY)和媒体访问控制(MAC),并专注于低功耗和共存性能改进,提出了一种低功耗集成CMOS两点调制高共存ZigBee收发器设计方法,并进行了实验验证。

1 ZigBee收发器架构

1.1 ZigBee描述

IEEE 802.15.4定义了无线电传输中的PHY层和MAC层,而ZigBee则定义了网络、安全和IEEE 802.15.4系统应用框架。这些功能使网络有能力配备大量的设备,例如,在单一协调器和单一无线网络下可配置高达64 000个节点[6]。

2.4 GHz的IEEE 802.15.4标准物理层采用直接序列扩频(DSSS)和偏移正交相移键控(O-QPSK)调制,实现了250 kb/s的数据传输速率。长度为4 bit的数据映射为一个符号,每个符号将映射为16个不同的32芯片的PN码序列。最后,该2 Mchip/s芯片速率产生2 MHz的射频带宽TX光谱。共有16个频道,频率范围从2 405~2 480 MHz,间距为5 MHz。

在IEEE 802.15.4中定义的物理层和MAC层通过ZigBee收发器实现[7]。由于ZigBee收发器运行在外部微控制器(MCU)中,框架的上层如网络、安全层和应用程序配置文件,必须通过外部MCU实现。换言之,ZigBee收发器只提供MCU的无线接口。在收发器的顶部,ZigBee SoC通过集成单片机、闪存和外设进行系统构建。

1.2 整体架构设计

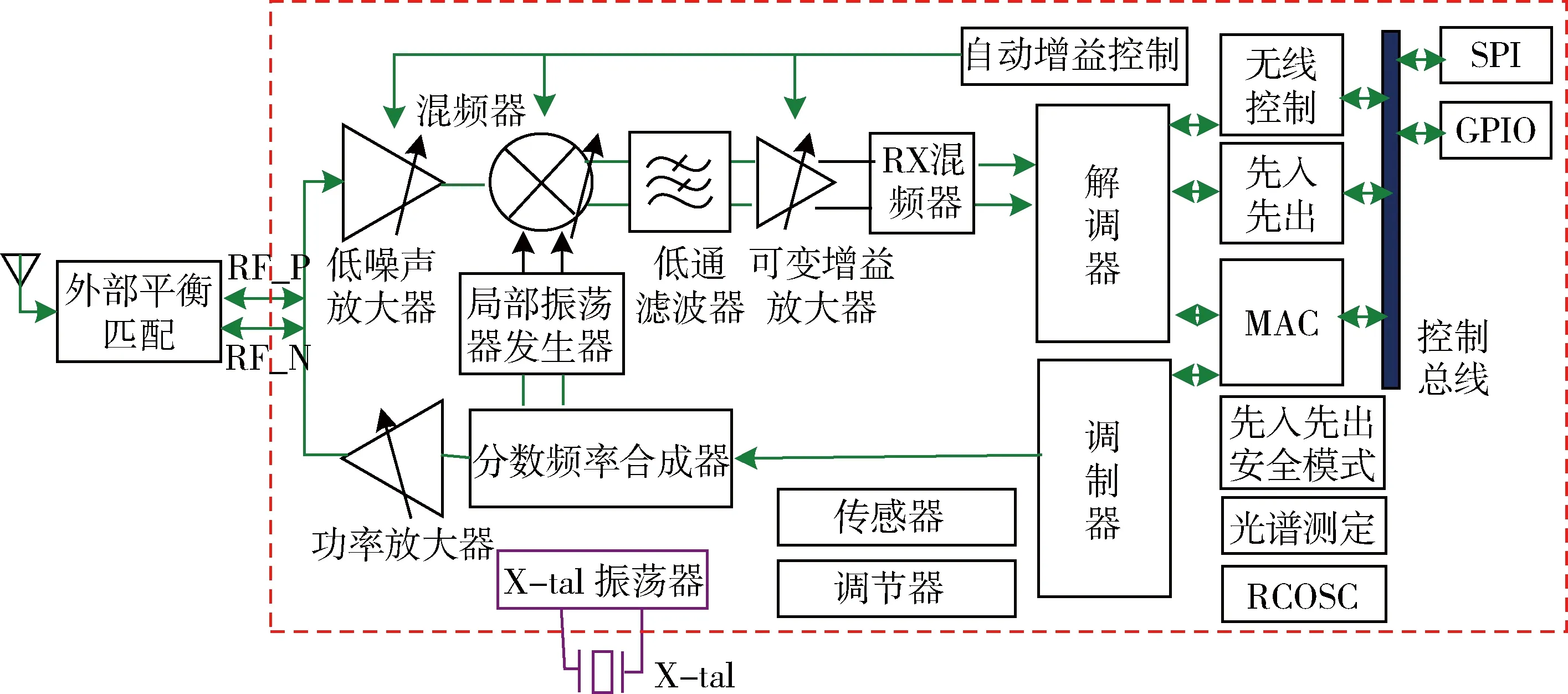

图1所示为本文设计的2.4 GHz ZigBee收发器的简化结构示意图。

图1中,从TX的MAC中按照先入先出(FIFO)的原则进行数据选取,并进行TX调制。在增加了帧定界起始符(SFD)和有效载荷的字段长度之后,根据PHY控制器的数据速率控制构造框架映射到指定的符号。如前所述,传输的字符是通过O-QPSK进行调制的。

2 关键结构设计

2.1 系统设计描述

接收器的灵敏度指标可定义如下[8]:

sensit=-74 dBm/Hz+10·log(BW)+NF+SNRout

(1)

图1 ZigBee收发器架构

式(1)中,BW、NF和SNRout分别表示信道带宽、噪声系数和所需的解调器信噪比(SNR)。为了满足IEEE 802.15.4标准定义的-85 dBm的灵敏度,在信道带宽BW的取值为2 MHz情况下,噪声系数NF的取值应该小于20.5 dB,解调器信噪比SNRout的取值应该小于5.5 dB。然而,需要增加链路预算,因为商业上需要的灵敏度要低得多。例如,本文中的设计目标是灵敏度低于-97 dBm。根据灵敏度指标定义(1)可知,与外部的平衡和匹配电路的噪声系数NF的取值应低于8.5 dB。

虽然IEEE 802.15.4标准规定输出功率至少为3 dBm,但是发射功率可通过提高链路预算进行提高。同时,芯片的高输出功率可弥补在许多应用中对外部功率放大器(PA)的需求,从而获得与外部PA相比更少的功率消耗和更具成本效益的解决方案。因此,本文中选取9 dBm的输出功率。假设可获得0-dBi天线增益,以及106 dB的链路预算。基于远场近似的路径损耗,及其与链路预算的关系可定义如下[9]:

Ploss=27.6-20·log(F)-n·log(D)

(2)

(3)

式中,F、D和n分别表示频率、距离和路径损耗因子。路径损耗因子取决于场本身,并考虑到不同的情况下的多路径传输问题。在一般情况下,应考虑到链路的可靠性和宽裕度(Margin),利用式(2)和式(3)进行通信范围计算,所计算的通信范围设定链路预算为106 dB,具体如表1所示。

表1 通信范围估计

假设链路可靠性超过99%,并采用开放式办公场,通信距离计算约为33 m,可覆盖多数的室内短距离应用。在实践中,尽管会增加传输延迟,仍可通过IEEE 802.15.4 MAC标准进行重传,从而实现链路质量的提升。

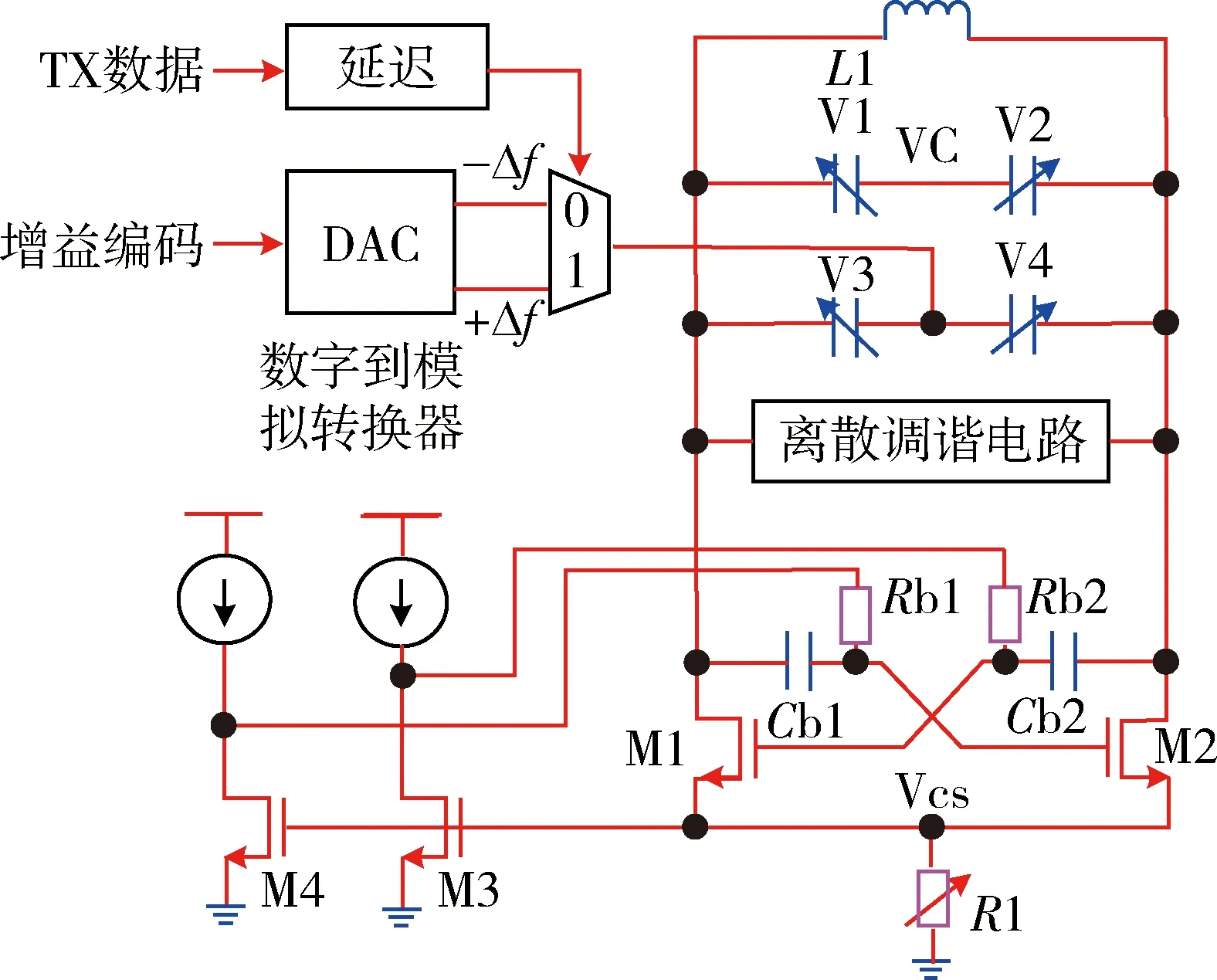

2.2 频率合成器

一种用于产生信道频率的分数合成器,如图2(a)所示,其包含相位频率检测器(PFD)、电荷泵、环路滤波器、三阶调制器(SDM)、双模8/9分频器、可编程分频器和一个压控振荡器(VCO)。使用一个32 MHz的晶体作为参考时钟。VCO的输出频率可通过合成获得。锁相环(PLL)的带宽为100 kHz ,用于优化相位噪声性能。通过调整电荷泵电流和环路滤波器组件值,锁相环的环路带宽可以控制在约200 kHz左右。利用2 Mchip/s的O-QPSK可实现频率偏差为500 kHz的频移键控(FSK)。由于与信号相比,锁相环具有较窄的带宽,则将信号同时施加到SDM和VCO中,称之为两点调制。由于SDM路径和VCO路径所具有的低通和高通特性,则从每个信号路径内的锁相环的复合输出可以实现带宽调制,如图2(a)和图2(b)。

图2 基于频率合成器的两点调制

在实践中,两个路径之间的相位和增益不匹配,会降低发射频谱质量,例如EVM。为解决相位和增益不匹配,实现延迟线和可变调制VCO的增益校准,设计了如图3所示的压控振荡器。

图3 压控振荡器

如图3所示,通过在TX过程中使用大环路带宽实现EVM的进一步优化,而在RX过程中使用小环路带宽实现局部振荡器(LO)的噪声抑制。一个对称差分6.1 nH感应器用来降低电流,并增加并联电阻Rp的有效性。为减少低频相位噪声,对低频相位噪声的主要来源尾电流源进行删除。图中,M1和M2通过负反馈控制逐渐趋向M3和M4。负反馈使节点Vcs对于外部扰动不敏感,如M3和M4电流噪声。因此,液晶振荡器的相位噪声对低频噪声的影响要小得多。

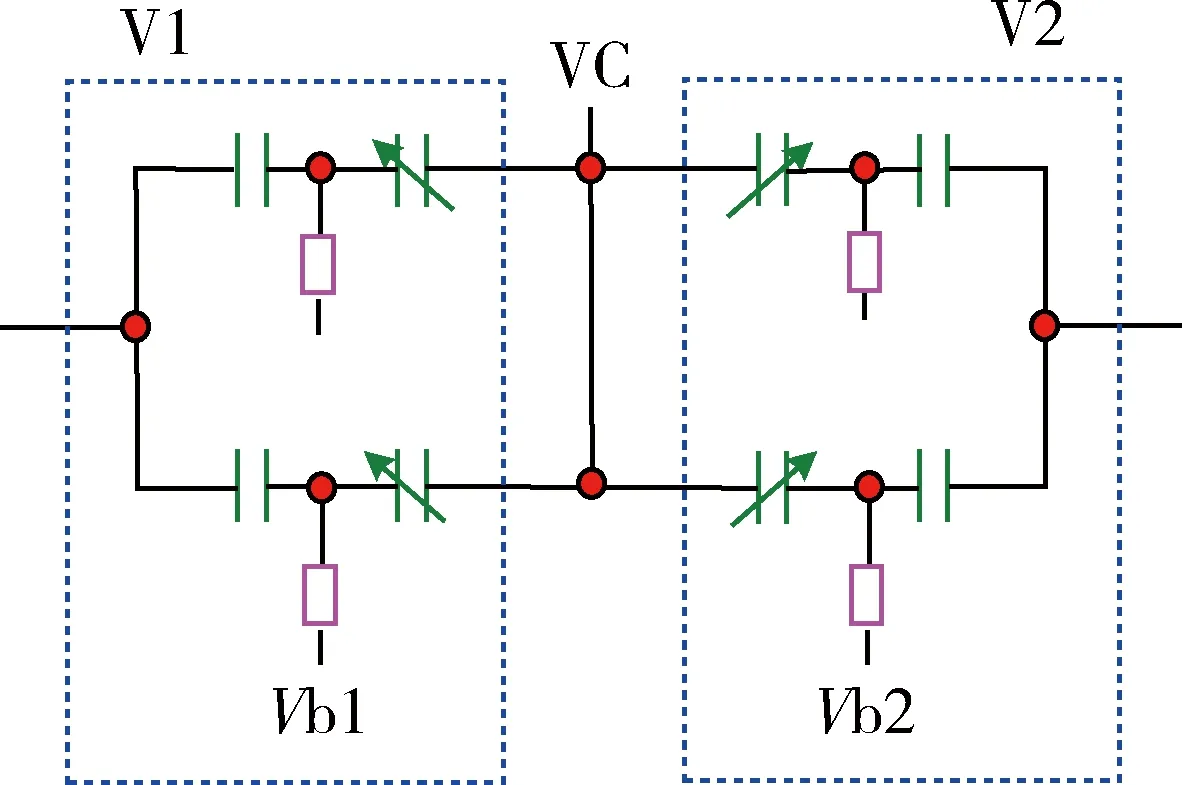

图3中,V1和V2组成MOS变容二极管,V1和V2是由频率和相位锁定的连续环路滤波器驱动。由于MOS变容二极管的电容-电压曲线不是线性的,压控振荡器的增益(KVCO)变化剧烈,会导致锁相环的相位噪声和发射机EVM恶化。为提高KVCO的线性度,V1和V2的设计为具有不同偏差的变容二极管,如图4所示。

图4 具有不同偏差变容二极管

离散调谐电路被设计为一个具有4位控制的二进制加权电容器开关阵列。在PLL解决了信道频率后,TX调制数据应用于其他由V3和V4组成的MOS变容二极管,如图3所示。采用6位数字模拟转换器(DAC)为V3和V4组成的变容二极管调制提供所需的电压等级,其频率偏差为500 kHz。

2.3 低噪声放大器和功率放大器

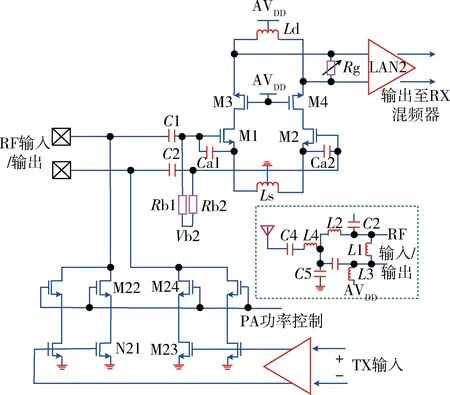

图5所示为简化的低噪声放大器(LNA)和功率放大器(PA)示意图。采用差分电路,以尽量减少从电源线和基板产生的噪声影响。由于时分双工(TDD)特性,LNA的输入与PA的输出是端口共享的。电感L1作为射频电路匹配,同时作为PA的输出负载。组件的L2、L3、C2和C3构成平衡,其将差分射频信号转换为单端射频信号。L4、C4和C5构成LC谐波滤波器来抑制TX的谐波输出。此外,C4用于直流阻断。

图5 低噪声放大器和功率放大器

利用共源共栅的退化电感结构,进行LNA设计。额外的电容器Ca1和Ca2用于优化噪声匹配。通过调节电阻输出可实现AGC的增益控制。第二阶段,LNA2作为Gm阶段的电流驱动无源混频器。在利用低通滤波器进行通道滤波后(LPF),具有47 dB的动态范围的可变增益,放大器(VGA)为4位闪存ADC设置足够的电平信号。

利用信号接收强度指示(RSSI)进行AGC的增益控制。NF的模拟值和LNA的增益分别为3.5 dB和21 dB。由于后续的无源混频器有25 dB的NF,相应的级联噪声系数计算为约6.7 dB。对来自频率合成器和输出功率天线的调制信号进行PA放大。PA的输出阶段由可编程级联阶段构成,控制输出功率为9~50 dBm。

为了提高混频器的性能,采用无源混频器的电流驱动而不是有源混频器,如图6所示。

图6 RX混频器原理

因为射频前端包括低噪声放大器,混频器的设计应该覆盖整个ISM频段,其不能执行信道滤波。混频器的输出电流携带一个小信号和一个大的阻挡器,因此图6中的运算放大器的输出电流偏差应足够大。如果图6中,从电流到电压的转换过程中电流的线性度可以保证,则可实现对接收器电源电压摆动的线性度限制,进而实现噪声的抑制。

3 实验分析

利用90 nm的单聚和6层金属层CMOS技术设计实现完整的收发器,整体实验模型采用MATLAB/Simulink仿真平台进行实现。实验硬件配备:CPU i7-4790K 3.6 GHz,物理内存为ddr4-2400 GHz,存储大小为1 TB,系统为Win7旗舰版。

压控振荡器输入使用到了TX数据,图7所示为通过O-QPSK调制的TX输出频谱实验数据。

图7 TX输出功率频谱

根据图7可知,测得的输出功率为+9 dB,输出功率频谱符合上述IEEE 802.15.4传输要求。TX谐波量小于45 dBm,这符合美国联邦通信委员会(FCC)的规定以及欧洲电信标准协会(ETSI)的要求。

根据功率放大器的输出所得到的合成器的相位噪声测量值如图8所示。

图8 信道频率2.45 GHz合成器的相位噪声

根据图8可知,在2.45 GHz信道频率上,10 kHz和1MHz的偏移量分别为83.6和111.5 dBc/Hz。一般来说,直接调制发射机具有更好的相位噪声,可提供更好的矢量幅度误差。锁相环测得的参考杂散低于70 dBc。测得的锁相环锁定时间小于80 μs。

为验证所提方法的干扰抑制能力,图9所示为ZigBee干扰测量抑制比。

根据图9可知,该比率是11、15和25三个信道数据包长度为25 bytes的测量值。所需的信号功率最低灵敏度被设置为3 dB以上。在不同的干扰功率和信道频率上,测量超过1%的干扰水平。同信道,相邻和相间信道在±0、±5和±10 MHz的抑制分别约为-6.4、31和52 dB。可见抑制比大于65.6 dB的干扰位于距离超过15 MHz,因此获得了优秀的信道干扰抑制能力。

4 结束语

本文提出一种低功耗集成CMOS两点调制高共存ZigBee收发器技术,可进一步降低ZigBee技术的数据传输功耗,并提高其共存和干扰抑制性能,通过仿真实验,验证了所提ZigBee收发器在数据传输功耗、共存性以及干扰抑制能力上的优势。通过这项工作,ZigBee可为生物医学和医疗应用提供一个可行的解决方案。

以上设计方案在实现过程中首先在实验室环境下,通过MATLAB仿真软件进行了实现,但是未涉及到硬件的具体开发,今后将在ZigBee硬件设计与实现上做深入研究,并积极进行实际应用推广。

[1] 钱志鸿, 朱爽, 王雪. 基于分簇机制的ZigBee混合路由能量优化算法[J]. 计算机学报, 2013, 36(3): 485-493.

[2] 任智, 李鹏翔, 姚玉坤, 等. 基于分段的ZigBee网络按需可扩展地址分配算法[J]. 通信学报, 2012, 33(5): 131-137.

[3] 何海平, 郭杭, 方爽. 基于模糊聚类的ZigBee室内定位系统设计[J]. 电子技术应用, 2016, 42(5): 71-73, 77.

[4] 赵博, 吴静. 基于ZigBee无线网络的Cluster-Tree路由算法研究[J]. 电子技术应用, 2016, 42(4): 116-119, 123.

[5] Cao Xianghui, SHILA D M, Cheng Yu, et al. Ghost-in-ZigBee: energy depletion attack on ZigBee-based wireless networks[J]. IEEE Internet of Things Journal, 2016, 3(5): 816-829.

[6] Tao Dan, Yang Guangwei, Chen Houjin, et al. Efficient image transmission schemes over ZigBee-based image sensor networks[J]. Chinese Journal of Electronics, 2016, 25(2): 284-289.

[7] 千承辉, 张希明, 徐丹琳, 等. 基于ZigBee无线传感网络的人员定位系统设计与实现[J]. 微型机与应用, 2016, 35(21): 72-74, 78.

[8] BIHL T J, BAUER K W, TEMPLE M A. Feature selection for RF fingerprinting with multiple discriminant analysis and using ZigBee device emissions[J]. IEEE Transactions on Information Forensics and Security, 2016, 11(8): 862-874.

[9] 游张华. 基于ZigBee和H.264的无线视频传输系统的设计与实现[J]. 微型机与应用,2016,35(24):54-56,60.

Low power ZigBee transceiver based on O-QPSK transmissionmodulation two point synthesis

Jiang Huiping

(General Affairs Department, Qingdao University of Technology (Linyi), Linyi 273400, China)

In order to reduce the power consumption of data transmission, a low power integrated CMOS ZigBee transceiver with two points modulation was proposed. Firstly, the ZigBee transceiver architecture was designed, and the data was selected with the principle of the first in first out (FIFO) from TX MAC, then the frame bound start (SFD) field length and payload was increased, and it carried on the transmission character with the O-QPSK modulation; Secondly, the key components of the ZigBee transceiver architecture were designed, and the design method of the frequency synthesizer, low noise amplifier and power amplifier based on two points modulation were presented. Finally, the simulation results show that the proposed ZigBee transceiver has advantages in the power consumption and coexistence performance of the data transmission.

CMOS integration; low power consumption; ZigBee transceiver; two point synthesis; O-QPSK modulation

TN832

A

10.19358/j.issn.1674- 7720.2017.13.010

蒋惠萍.基于O-QPSK传输调制两点合成低功耗ZigBee收发器[J].微型机与应用,2017,36(13):29-33.

2017-02-13)

蒋惠萍(1986-),女,硕士,助教,主要研究方向:嵌入式硬件设计,通信技术应用。