低功耗基准电压源的设计与实现

杨金亮,李天生

(1.赣州师范高等专科学校 计算机系,江西 赣州 341000;2.电子科技大学 微电子与固体电子学院,成都 610054)

低功耗基准电压源的设计与实现

杨金亮1,李天生2

(1.赣州师范高等专科学校 计算机系,江西 赣州 341000;2.电子科技大学 微电子与固体电子学院,成都 610054)

为实现低压低功耗的要求,利用E/D NMOS阈值电压皆为负温度系数的特点,设计一种参考电压为增强型、耗尽型NMOS阈值差的低功耗基准电压源。通过电路参数的设计,使参考电压的温度系数趋近于0,采用2个串联的电阻作为输出级,使参考电压方便可调,并在电路中加入负反馈环路,使参考电压更加稳定。仿真实验表明,低功耗基准电压源具有高响应速度和高稳定性等优点。

低功耗;基准电压源;阈值电压差

0 引 言

随着集成电路尺寸的不断减小和半导体制造工艺的迅速发展,高精度和高电源抑制比的基准电压源几乎成了所有模拟和混合电路系统中不可缺少的基本模块。然而,传统的带隙基准电压源的面积和功耗都比较大,其基准电压一般都大于带隙电压,很难实现低压低功耗的要求[1]。目前,非CMOS工艺的基准电压在实际应用时取得了较高的精度和稳定性。本文提出基于NMOS工艺的基准电压源,其参考电压基于增强型、耗尽型NMOS阈值差。同时采用阈值电压构成基准电压,结构所需的供电电压大幅减小,易于实现低功耗设计。

1 基于NMOS工艺的低功耗基准电压源整体电路设计

基于E/D NMOS阈值差的基准电压源具有较高的精度、较低的温度系数及较低的功耗。本文提出改进后的电路结构,不但输出参考电压具有较高的温度稳定性,电源电压抑制比较高,且输出电压可通过修改参数易于实现自由设定。基于NMOS工艺的低功耗基准电压源整体电路结构如图1所示。

图1 基于NMOS工艺的低功耗基准电压源整体电路结构

由图1可知,其整体电路结构由5个MOS晶体管和2个电阻组成。M1为耗尽型NMOS管,M2, M5为增强型NMOS管,M3, M4为PMOS管。由M3, M4组成电流镜,通过调节M3, M4的宽长比,使ID3与ID4保持相等或整数关系。M1, M2, M 3, M 4组成基准电压源的主体部分,产生对温度不敏感的基准电压VGS2。R1, R2串联组成输出端,调节R1与R2的比例,使输出的参考电压在一定范围内可调。R1, R2, M5组成负反馈电路,使输出参考电压稳定。

2 基于NMOS阈值差的低功耗基准电压源的设计与实现

本文提出改进后的电路结构,由于简化了第一级参考电压生成电路,即无法通过电路参数的设定完全消除E/D NMOS沟道表面迁移率不同带来的温度系数,因而在电路中加入有电阻R1, R2及晶体管M5组成的负反馈电路,以稳定输出电压VREF。

2.1 迁移率对掺杂浓度的依赖关系

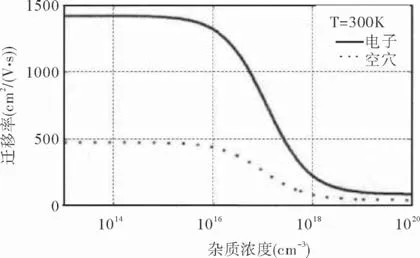

硅晶格中杂质原子的浓度水平对迁移率有很大的影响。特别是由于库仑散射机制,杂质原子的存在降低了自由载流子的迁移率。最低的迁移率出现在较低的温度情况下,而非较高的温度情况下,因为前者的声子散射效应不显著[2-4]。此外,电离杂质浓度的正向温度系数的存在,减小了迁移率温度系数。在室温T下,电子迁移率随掺杂水平变化的经验公式为:

其中NA为受主杂质掺杂浓度。

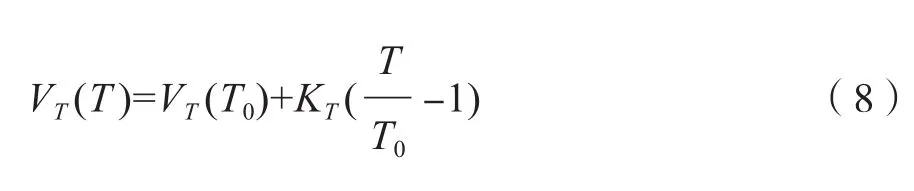

当掺杂浓度NA较小时(<1018cm-3),电离杂质的影响很小,μ基本由晶格散射决定,随着温度升高,整个散射几率在升高,迁移率下降。当掺杂浓度NA较大时,在温度较低的范围内,晶格散射的影响较弱,电离杂质影响比较显著,μ由晶格散射和电离杂质散射决定;在温度较高的范围内,晶格散射增加,其影响增强使得μ随温度的升高而下降。可见,迁移率μ随着杂质浓度的升高而下降,随着温度的升高而下降。实际硅中迁移率与掺杂浓度的关系如图2所示。

图2 实际硅中迁移率与掺杂浓度的关系

由图2可知,在掺杂浓度较低的范围内(<1016cm-3),载流子迁移率几乎不变;在高掺杂的硅中,载流子迁移率随着掺杂浓度的升高而迅速降低。

2.2 低功耗基准电压源的主体电路设计

低功耗基准电压源利用MOS阈值电压对温度的线性关系,通过对电路参数的设计,达到基准电压的零温度系数。同时通过输出端的设计,使基准电压输出方便可调(见图1)。

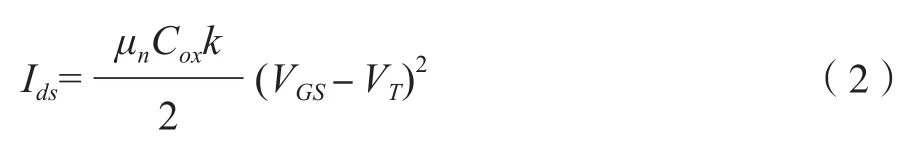

NMOS管的漏极电流表达式为:

其中k为NMOS管的宽长比。

M1为耗尽型NMOS管,由于M1的栅极和源极同时接在地电位GND,因而依据(2)式,可求得M1的漏极电流为:

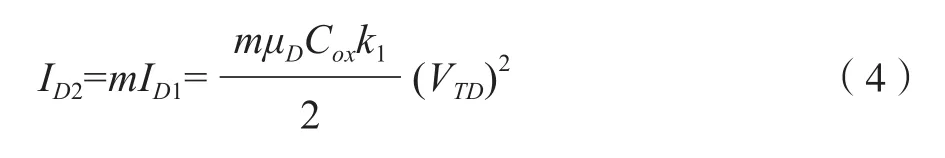

M3,M4组成电流镜,使ID1与ID2相等或倍数关系。设ID2=m ID1,则

可求得:

在E/D NMOS工艺中,衬底掺杂一般为1011~1015cm-3。根据分析,杂质浓度在这个范围内变化时,电子迁移率μn几乎不变,因而可将(5)式简化为:

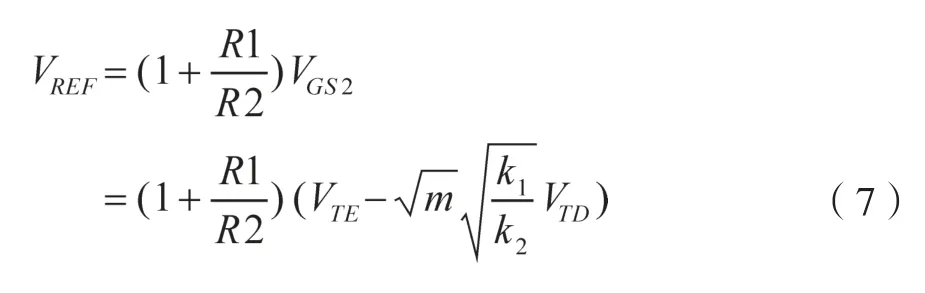

由于电压VGS2通过串联的电阻R1, R2组成的输出级分压后输出,即输出电压VREF,因而VREF的表达式为:

输出参考电压为增强型与耗尽型NMOS晶体管阈值电压的线性组合,且增强型与耗尽型NMOS晶体管阈值电压与温度皆为线性关系,而两个温度系数都为负值。故参考电压VREF可实现温度系数近乎等于0。阈值电压对温度的导数为一常数,其关系可表达为:

其中,KT为NMOS阈值电压的温度系数,且KT<0;T为绝对温度;T0为测量KT时的绝对温度。参考电压VREF对温度的导数表达式为:

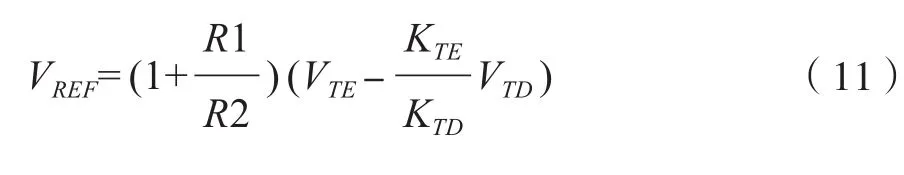

由(10)式可看出,通过设置调整M1, M2的宽长比的比例,并调整组成电流镜的M3, M4的宽长比的比例,以改变电流镜两端电路的倍数关系,就可得到零温度系数的参考电压。依据(6)、 (10)式可得:

其中,KTE, KTD, VTE, VTD决定于所用的制造工艺,因而输出参考电压的值决定于R1与R2的比值,且此比值不受其他条件的限制,使输出参考电压可通过改变R1与R2的比值而在较大范围内自由设定。因此,可根据不同系统、不同电路的参数要求而改变参数得到不同的参考电压值。

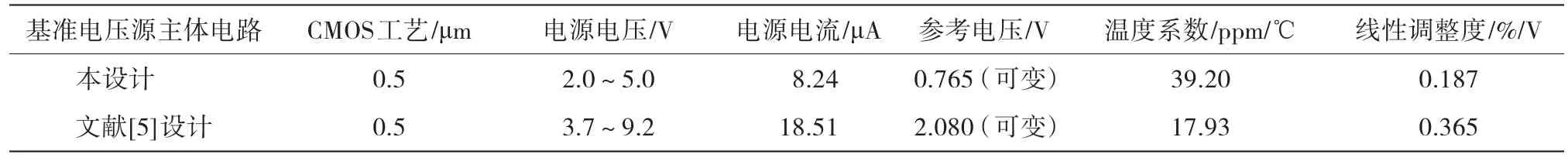

将本设计性能指标与文献[5]设计性能指标进行比较,结果见表1。相比文献[5]设计,本设计参考电压的调整具有更大的灵活性,可简单地通过改变电阻之间的比值而调整输出参考电压的大小。同时由于改进了文献[5]电阻分流的缺陷,本设计在温度特性上有着更好的表现。

2.3 反馈回路的设计

当受主杂质掺杂浓度较小时,电子迁移率随杂质浓度改变的变化并不明显,故在以上分析和计算中,增强型NMOS与耗尽型NMOS中电子迁移率的比值μE/μD近似代为1。但由于比值μE/μD稍偏离1,且在温度较高时,增强型NMOS与耗尽型NMOS中电子迁移率μE与μD因为掺杂浓度的不同而呈现不同的变化趋势,使参考电压随温度变化而偏离理论值。

表1 电路性能指标比较

负反馈环由电阻R1, R2及晶体管M5组成。其负反馈过程为:当温度变化时,若VGS2升高,通过R1, R2的分压,VREF随之升高,且ID=VGS2/R2亦随之升高。M5的栅源电压VGS5随之增加,故M5的栅极电位随之升高,即M 2的漏极电位升高。M 2的漏极电位与M 2的栅极电位相位相反,故VGS2随之减小。当电阻间比值R1/R2确定时,通过调整R1与R2的比值可微调输出参考电压VREF的电压值,同时可改变参考电压的温度系数,以达到最佳的温度稳定性。

3 仿真实验

为验证输出电压VREF的具体特性,对电路进行仿真,分析其温度特性、功耗、供电电压及线性调整率等关键参数,从而说明电路的优势。

3.1 温度特性

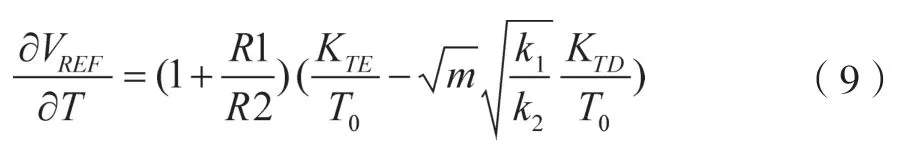

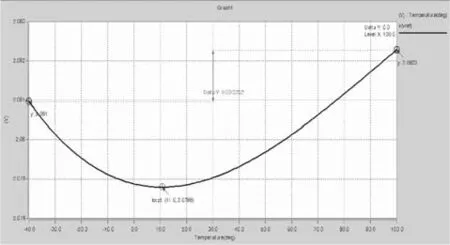

固定供电电压为5V,扫描-40℃~100℃的温度范围,查看输出的温度特性,仿真所得的VREF温度特性曲线如图3所示。

图3 VREF温度特性曲线

图3的温度系数可计算为:

由此说明VREF在不需要高阶温度补偿的情形下具有非常好的温度特性。

3.2 功耗

在一固定的电源电压下,为降低功耗,需降低三路电路的值,即ID1, ID2, ID5。依据(4)、 (5)式可得:

降低电路功耗,需适当减小M1的宽长比,并适当增加电阻R1,R2的阻值。在上述电路设置中,当温度为25℃时,仿真得到的电流分别为:ID1=10.94μ,ID2= 5.49μ,ID5=2.08μ;VDD=5V,I=-18.51μA,P=96.57μW。

3.3 供电范围

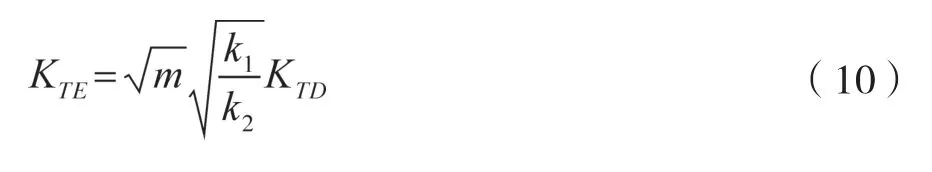

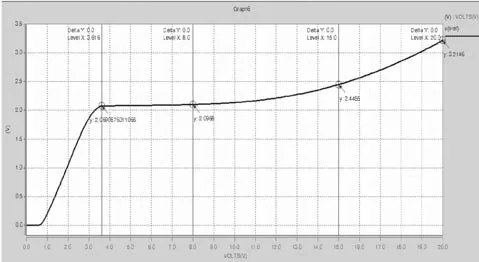

温度为25℃时,将电源电压VDD在0~20V范围内进行扫描,所得参考电压VREF随VDD变化的曲线如图4所示。

由图4可知,当电源电压VDD在3.6~9V间变化时,参考电压VREF基本保持不变。在可正常工作的电源电压范围的上下边缘处进行温度曲线的扫描,即对不同的电源电压下参考电压VREF在-40℃~100℃温度范围内进行扫描,可得到较为精确的可正常工作的供电电压范围。

图4 VREF随VDD变化的曲线

3.4 线性调整

温度为25℃时,在电源电压范围内对参考电压VREF进行扫描,可求出电路的线性调整率。当电源电压VDD在3.7~9.2V间连续变化时,其线性调整率曲线如图5所示。

图5 线性调整率曲线

由图5可知,当电源电压VDD=3.7V时,VREF= 2.0717V;当电源电压VDD=9.2V时,VREF=2.1135V。

故基准电压源的线性调整率为:

4 结 论

本文设计的基于E/D NMOS的基准电压源具有NMOS工艺速度快、高频特性好、与CMOS工艺兼容、非线性失真小等优点,结构简洁,更易实现低功耗,在不需要高阶补偿的情况下能获得很好的温度系数,同时工作电压范围广,能满足不同电压下的应用,且输出基准电压可调。本设计的低功耗是在晶体管工作饱和区下设计的,相比于亚阈值区还有较大的优化空间,后续低功耗的研究将会集中在亚阈值区的基准电压源的设计。

[1] 杨方杰.低供电电压基准电压源设计[D].长沙:国防科学技术大学计算机学院,2011:7-11.

[2] 齐领,恩云飞,章晓文.MOSFET迁移率随温度变化关系研究[C]//广州:中国电子学会第十四届青年学术年会,2008:70-72.

[3] 张彦飞,游雪兰,吴郁.线性区工作模式下沟道中的载流子迁移率和温度梯度如何影响功率MOSFET的温度系数(TC):理论研究、测试和仿真[J].电力电子,2008(1):37-41.

[4] 罗衡,邓联文,易图林.半导体Si载流子迁移率的统计模型计算模拟[J].材料导报,2011(2):112-115.

[5] XIA X,XIE L W,SUN W F,et al.Temperature-stable Voltage Reference Based on Different Threshold Voltages of NMOS Transistors[J]. IET Circuits Devices & Systems,2009(5):233-238.

[责任编辑:谢树林]

Design and Realization of a Low-power Voltage Reference

YANG Jinliang1, LI Tiansheng2

(1.Computer Department, Ganzhou Teachers College, Ganzhou, 341000, China; 2.College of Micro-electronics and Solid-state Electronics, University of Electronic Science and Technology of China, Chengdu, 610054, China)

To realize the requirements of low voltage and low power, a low-power voltage reference w ith enhanced voltage reference and depleted NMOS threshold difference is designed by utilizing the characteristics of negative temperature coef f cient of E/D NMOS threshold voltage. The temperature coef f cient of voltage reference is made to approach zero through the design of circuit parameters. The voltage reference is designed to be easily adjustable by adopting two series resistors as outputs. And the voltage reference is made to be more stable by adding negative feedback loop to the circuit. Simulation results show that the low-power voltage reference has many advantages, such as high-speed response and high stability.

Low-power consumption; Voltage references; Threshold voltage difference

TN432

A

1671-4326 (2017) 02-0038-04

DO I: 10.13669/j.cnki.33-1276/z.2017.031

2016-07-05

杨金亮(1976—),男,江西赣州人,赣州师范高等专科学校计算机系讲师,硕士;李天生(1993—),男,江西赣州人,电子科技大学微电子与固体电子学院硕士研究生.