用于5.2 GHz带宽的低噪声放大器电路设计

刘艳竹

(惠州工程技术学校 电子科,广东 惠州 516001)

用于5.2 GHz带宽的低噪声放大器电路设计

刘艳竹

(惠州工程技术学校 电子科,广东 惠州 516001)

提出了一种在5.2 GHz带宽下使用反馈电路用于低噪声放大器(LNA)的新型自适应增益控制方法。通过使用基于级联型拓扑的双级LNA来实现可变增益。反馈电路由多个功能块组成,其中每个功能块被设计成具有最小的功耗。反馈电路中的存储电路可用于存储先前的信号幅度,从而避免LNA中不必要的功耗。在噪声因数(NF)、增益、IIP3和功耗方面均模拟了LNA的性能,其具有的反馈电路LNA的可变增益范围从11.39~22.74 dB,文中的可变增益LNA的DC功率在1.8 V的电源电压下为5.68~6.75 mW。

低噪声放大器;反馈;可变增益;基带信号

近年来,通信和网络的开发研究对于无线通信越来越重视[1]。由于无线市场激烈的价格竞争,降低电路的成本成为关键设计目标。与其他技术相比,CMOS技术在价格、电路面积等方面均具有显著优势。对于包括蜂窝电话和无线局域网络(WLAN)的市场需求导致了对无线通信系统领域的深入研究,因此对于低噪声放大器(LNA)的设计研究得到了广泛关注[2-5]。

根据诸如IEEE 802.11a的通用标准,可开发在5.2 GHz带宽下数据速率高至54 Mbit·s-1的WLAN装置。但所传送的信号不仅含有噪声,且在WLAN中衰减,从而接收器可能难以检测到衰减后的信号。通信系统中由于接收信号的功率衰减,导致了一些常见的问题。当所接收的信号受到衰减的影响时,LNA丢失了目标信号而检测到另一具有较高功率的信号。因此,可变增益LNA可缓解无线通信中的这一问题。高频应用中的可变增益LNA可使用两种可能的方式来控制增益:一种是使用具有数字的离散增益步长来建立可变增益LNA[6-7];另一种方法通过模拟增益控制反馈信号,以便通过调整MOSFET中的偏置点来改变LNA增益[8-9]。本文提出了一种使用反馈电路来实现的新型自适应可变增益LNA。所提出的可变增益LNA根据基带信号的幅度而具有4个增益模式。使用反馈电路的可变增益LNA可通过采用切换操作控制增益来降低功耗,并使总体动态范围最大化。

1 可变增益低噪声放大器的设计

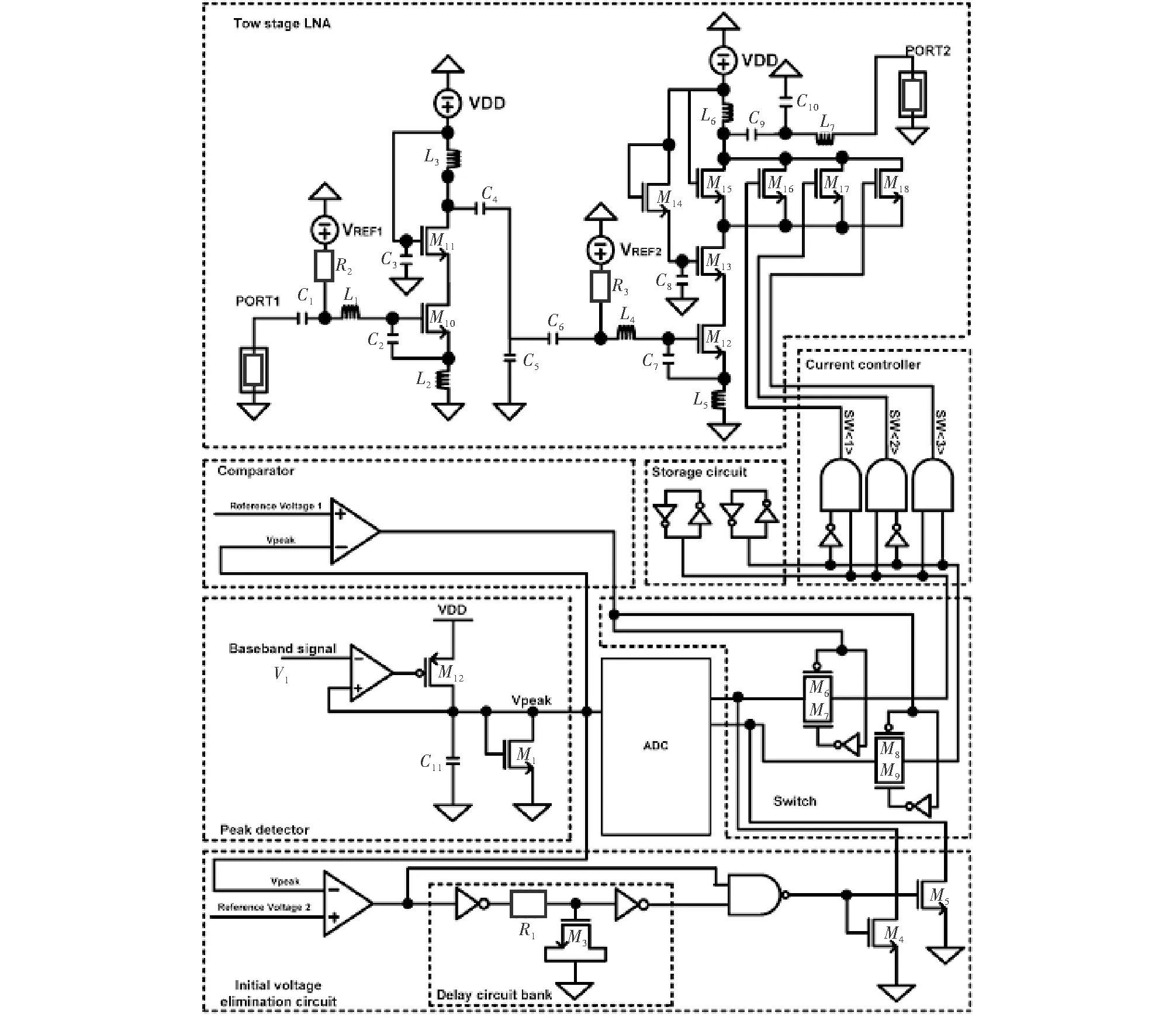

LNA在通信系统的接收器中起到重要的作用,这是由于从天线接收的信号通过LNA直接放大。为了放大所接收的RF信号,LNA必须能改变增益以便缓解衰减影响,且避免使下一个RF块饱和。因此,可变增益LNA可通过根据输入信号的强度选择LNA的适当增益来改善总体动态范围以及避免不必要的功耗[10]。图1示出了所提出的具有反馈电路的可变增益LNA的框图,反馈电路可监测信号强度以便控制LNA的增益。

图1 具有反馈电路的可变增益LNA的框图(虚线内部)

第一级LNA的设计具有如下通用目的:最小化噪声因数;提供具有足够线性度的增益;为从天线至放大器传送信号提供可用的输入阻抗[11]。本文所提出的可变增益LNA具有4个不同的增益模式,其可根据所接收的基带信号的幅度进行自动选择,如图2所示。

图2 所提出的可变增益LNA的示意图(虚线表示每个功能块)

对于可变增益LNA采用了两级级联拓扑,其能够获得高的增益、低输入相关噪声以及宽的增益。第一级LNA在降低整个接收器的噪声因数中起到重要作用。第一级LNA应当在MOSFET的栅极尺寸和偏置条件方面被优化以实现低噪声。第二级LNA被设计用于避免线性度的退化,这是由于最后一级的线性度会影响总的线性度。文中使用具有修改的感应退化级联拓扑来提供低噪声、高增益、良好的输入/输出阻抗匹配以及高的稳定性。

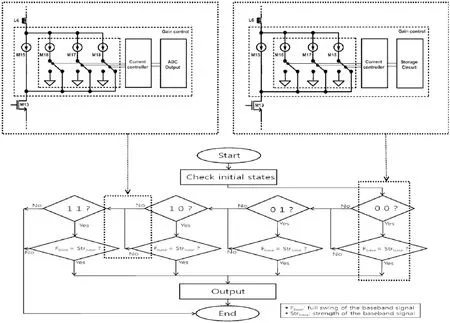

增益控制机制通过4个晶体管(M15、M16、M17和M18)来实现,且4个增益控制模式通过开启或关断在第二级LNA的输出处的4个分流n型MOSFET来执行。LNA增益可通过选择增益模式之一来改变。图3中示出了输出级的电路示意图,可变增益级中的4个晶体管根据来自反馈电路所生成的数字将输入电压转换成电流。当可变增益级被启用时,小信号电流流过一个或两个晶体管。当输入信号较弱时,电流控制器被设定为具有最低噪声因数(NF)的增益模式4。若输入信号变大,则电流控制器被设定为具有适合NF的增益模式1。

图3 根据反馈电路中的多个状态控制可变增益级的增益的流程图

2 反馈电路

反馈电路根据输入信号强度对所提出的LNA中的增益进行自动控制。反馈电路包括7个功能块:尖峰检测器、比较器、ADC、初始电压消除电路(IVEC)、开关、存储电路和电流控制器。其中,尖峰检测器是用于生成与基带信号的振幅成比例的瞬时尖峰电压的电路[12-13]。所提出的尖峰检测器包括二极管连接的晶体管、缓冲器和p型MOSFET,如图2所示。IVEC由比较器和时间延迟电路组成,IVEC用于避免在初始级处的ADC输出中生成错误信号。IVEC输出可将ADC输出设定为降低至接地[14-15],ADC输出可使用IVEC来设置期望的二进制字。

3 模拟结果

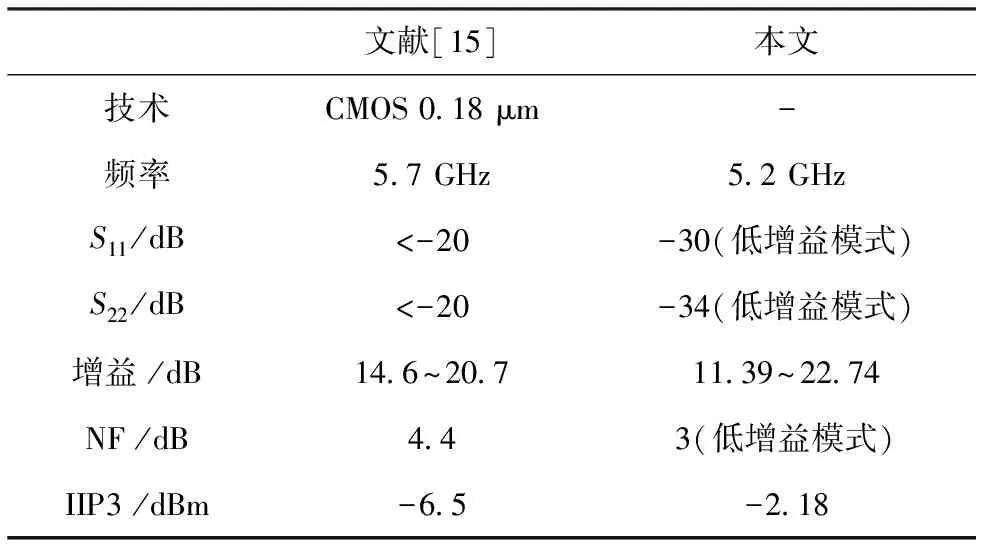

通过使用Cadence Spectre-RF、HSPICE和ADS模拟器在1.8 V的电源电压下评估了自适应可变增益LNA的总体性能。对所提出的电路进行深入模拟以找出最小的噪声因数和宽的可变增益范围。文中,对于5.2 GHz带宽使用反馈电路来提供自适应增益控制的可变增益LNA计算了噪声因数、增益、IIP3及功耗。表1总结了所提出的可变增益LNA在4个不同增益模式下的性能,且表2示出了与其他公开结果的性能比较。

表1 在5.2 GHz下在1.8 V电源电压下具有不同增益模式的两级LNA的性能总结

表2 具有不同增益模式的两级LNA的性能比较

图4示出了对于4个不同增益模式的LNA随频率变化的S21特性。可以看到,LNA的增益从11.39~22.74 dB变化,步长为4 dB。图5示出了所提出的LNA根据电流控制器中的控制位的增益、NF和功耗的性质。LNA对于控制位‘11’,增益为23 dB且NF为2.4 dB,而对于控制位‘00’,增益为11 dB且NF为3 dB。所提出的可变增益LNA对于较弱信号在增益模式4下提供了最高增益和最低NF。然而,在所接收的信号较强时,LNA在增益模式1下具有最低增益和最高NF。

图4 在4个增益模式下的可变增益LNA的S21随频率变化关系

图5 关于LNA中电流控制器的控制位的增益、功率消耗和噪声因数的性质

图6 可变增益LNA的噪声因数随频率变化关系

第一级LNA的噪声因数被直接加至所提出的LNA的总噪声因数,且第一级的可用增益能抑制随后电路的噪声贡献。当LNA被设置为增益模式4(最高增益)时,接收器接收最弱的输入信号(其会受到噪声的强烈影响)。因此,文中在增益模式4下对最小噪声因数进行优化。增益模式1下的噪声因数为3 dB,增益模式2下为2.8 dB,增益模式3下为2.6 dB,以及增益模式4下为2.4 dB,如图6所示。可变增益LNA的所有增益模式的噪声因数在5.2 GHz下均被保持为<3 dB。

4 结束语

本文提出并设计了使用反馈电路在5.2 GHz下的自适应可变增益LNA,其采用TSMC CMOS 0.18 μm技术来设计用于IEEE 802.11a WLAN。所提出的可变增益LNA通过实现自动增益控制避免了不必要的功耗。在1.8 V电源电压下运行,电路的可变增益范围为11.39~22.74 dB。在5.19 GHz和5.21 GHz下使用双音测试,IIP3在-2.18~1.5 dBm之间变化。LNA的NF为3 dB(增益模式1)、2.8 dB(增益模式2)、2.6 dB(增益模式3)和2.4 dB(增益模式4)。此外,该LNA还具有自适应增益控制的优点,且没有不必要的功耗,因此其可用于WLAN应用中。

[1] Cha C, Lee S. A 5.2 GHz LNA in 0.35 lm CMOS utilizing inter-stage series resonance and optimizing the substrateresistance[J].IEEE Journal of Solid-State Circuits, 2003, 38(4):669-672.

[2] 张胜标,张志浩,章国豪.用于S波段的高线性低噪声放大器[J].电子器件,2016,39(1):57-61.

[3] 彭龙新,牛超,凌显宝,等.2~20GHz GaAs超宽带杂谱抑制单片低噪声放大器[J].固体电子学研究与进展,2016,36(1):12-16,20.

[4] 李远鹏,魏洪涛,刘永强.一款超宽带低噪声放大器MMIC[J].半导体技术,2016,41(4):276-279.

[5] 陈立伟.基于自适应遗传算法的低噪声放大器设计[J].现代电子技术,2015,38(22):118-121.

[6] Piazza F, Tsivis P. A 2 mA/3 V 71 MHz IF amplifierin 0.4 lm CMOS programmable over range[C].Turke:International SolidState Circuit Conference,2009.

[7] Elwan H O, lsmail M. Digitally programmabledecibel-linear CMOS VGA for low-power mixed signal applications[J].IEEE Transactions on Microwave Theory and Techniques,2000,47(5):388-398.

[8] Yamaji T, Kanou N,Itakura T. A temperaturestable CMOS variable gain amplifier with 80 dB linearly controlledgain range[J]. IEEE Journal of Solid-State Circuits,2002,37(5):553-558.

[9] Christopher W M. A variable gain CMOS amplifier withexponential gain control[C].MA,USA:Symposium on VLSI Circuits Digest Oftechnical Paper,2000.

[10] Ellinger F,Jackel H. Low-cost Bi CMOS variablegain LNA at ku-band with ultra-low power consumption[J].IEEE Transactions on Microwave Theory and Techniques,2004,52(2):702-708.

[11] Shaeffer D K, Lee T H. A 1.5 V, 1.5 GHz CMO slow noise amplifier[J].IEEE Journal of Solid-State Circuits,1997,32(5):745-759.

[12] Steyaert M, Real P. A CMOS rectifier-integrator foramplitude detection in hard disk servo loop[J].IEEE Journal of Solid-State Circuits,1995,30(7):743-751.

[13] Barker R. CMOS circuit design layout simulation[M].CA,USA:IEEE Press Series on Microelectronic System,2005.

[14] Hwang Y S, Huang P H. An efficient powerreduction technique for CMOS flash analog-to-digital converters[J].Analog Integrated Circuits and Signal Processing,2009,61(3):271-278.

[15] Tangel A, Choi K. The CMOS inverter as a comparatorin ADC designs[J].Analog Integrated Circuits and SignalProcessing,2004,39(2):147-155.

Circuit Design of Low Noise Amplifier at the 5.2GHz Band

LIU Yanzhu

(Electronic Department, Huizhou Engineering & Technical School, Huizhou 516001, China)

This paper proposes a new adaptive gain control method for low noise amplifiers (LNAs) at the 5.2 GHz band by using a feedback circuit. A variable gain can be realized by using a two-stage LNA on the basis of the cascade topology. The feedback circuit consists of several functional blocks, each of which is designed with minimum power consumption. The storage circuit in the feedback circuit can be used to store the previous signal magnitude, therefore avoiding unnecessary power consumption in the LNA. The performances of LNA has been simulated in terms of the noise figure (NF), gain, IIP3, and power consumption. The variable gain of the LNA with the feedback circuit ranges from 11.39 to 22.74 dB. The DC power of the variable gain LNA is from 5.68 to 6.75 mW at a 1.8 V supply voltage.

low noise amplifier; feedback; variable gain; baseband signal

2016- 10- 08

刘艳竹(1979-),女,讲师。研究方向:电工与电子。

10.16180/j.cnki.issn1007-7820.2017.07.040

TN722.3

A

1007-7820(2017)07-142-04