DCF77时间码解码方案的设计

周振洲,席自强,王 平

(1.太阳能高效利用湖北省协同创新中心,湖北 武汉 430068;2.上海交通大学 电子信息工程与电气工程学院,上海200240)

DCF77时间码解码方案的设计

周振洲1,席自强1,王 平2

(1.太阳能高效利用湖北省协同创新中心,湖北 武汉 430068;2.上海交通大学 电子信息工程与电气工程学院,上海200240)

提出了一种基于FPGA的DCF77解码方案设计。实现过程中着重针对码元识别部分进行分析,设计了一种有限状态机来完成对不同码元的识别以及数据写入等。通过Modelsim软件对程序进行了功能仿真,验证了该方案可以正确的进行时间解码。相比常用的IRIG-B码,增加了星期的信息,并且每一帧只有60位,恰好与时间进制相同,具有代码简单、工作稳定性强、易于移植等优点。

DCF77码;解码;有限状态机;码元识别

DCF77码是德国无线长波对时信号的时间码,该时间格式码包含年、月、日、时、分、星期等完整的绝对时间信息,在法国、德国等主要欧洲国家得到了广泛应用[1-2]。我国电力、通讯、石化、冶金、国防、金融等一些行业中也都将DCF77作为一种重要的时间格式来使用[3-4]。本文介绍了DCF77码的格式与规范,针对目前DCF77码解码方案较少,解码过程不连续等问题,提出了一种新的解码方案。

1 DCF77时间码

DCF77时间码是一种串行格式[5]的时间码,它在秒信号的间隙传输时间信息;为方便理解时间码的格式,这里引入“码元”的概念[6]。将每帧信号中最小的单位定义为1个码元。由于是在秒信号的间隙传输信息,所以得出在DCF77码中,每帧包括60个码元,每个码元长度都为1 000 ms,刚好对应时间信息里的“秒”。

根据DCF77码的特点,共引入3种不同的码元,如图1所示。一个秒脉冲持续0.1 s(脉宽为0.1 s)表示二进制编码的“0”;持续0.2 s(脉宽为0.2 s)表示二进制编码的“1”;第59 s通常不进行传输,脉宽为0。利用59 s的这种特殊性,将其作为起始标志,用来检测输入时间信息的起点。

格式方面,由3个测试位P1,P2,P3扩展成时间码的3个主要段落:7位表示分钟,6位表示小时,22位表示包含星期数在内的日期,具体编码规则如表1所示。

图1 3种码元

码元标识数代表意义0分钟,常为01~14保留,常为0续表115天线(0表示正常天线,1表示备用天线)16时区变化通告(0表示正常,1表示提前1h)17~18夏令时(01表示正常,10表示夏令时开启)19润秒通告[7],一般提前1h通告(0表示润,1表示不润)20时间码的起始位,常为121~27分钟信息(位权分别为1,2,4,8,10,20,40min)28P1测试位,21~28位的奇偶校验应为偶数,常为129~34小时信息(位权分别为1,2,4,8,10,20h)35P2测试位,29~35位的奇偶校验应为奇数,常为036~41所在月的日信息(位权分别为1,2,4,8,10,20日)42~44星期信息(位权分别为1,2,4)45~49月份信息(位权分别为1,2,4,8,10月)50~57年份信息(位权分别为1,2,4,8,10,20,40,80年)58P3测试位,36~58的奇偶校验应为奇数,常为059通常,这一位不被传输;本文中当作“起始标志”来使用。

图2给出了一帧完整的数据示意图,其包含的二进制信息[8]为: 000000000000000000101_1001101_ 0_110001 _1_100101111_1100000000000_1_0。为了更清晰地表示出起始标志,把第59位码元放到第1位。本文将就对此帧数据进行解码并进行验证。根据前边DCF77编码规则可知,此帧数据代表的时间信息为:2000年2月29日23时59分,星期日。

图2 DCF77编码帧示意图

2 解码程序设计

程序首先需要对码元进行识别[9],通过对输入的脉冲进行计数,首先找到起始标志,然后根据脉冲的个数判断该码元是“0”还是“1”,接着采用状态机对0~58位的数据依次进行采集,最后根据DCF77的格式有序的对所采集到的信息进行解码,提取出所需要的时间信息[8]。

2.1 分频模块设计

为完成对数据的采样,采用归一化的时钟[10-11],这里采用频率为1 kHz的时钟,每个间隔为1 ms。由于59 s作为起始标志,是连续1 000 ms的低电平,为便于检测,这里统一选取对时钟的负边沿进行计数,完成时间数据采样。当data_in处于低电平时,count_1_valid标志置1,count_1开始计数。

2.2 码元识别有限状态机设计

针对码元的几种不同类型以及所代表的不同意义,本文设计了一个有限状态机[12](FSM),包括5个状态:Idle,Judge,Start,St0,St1。该状态机可以完成状态的检测,脉冲计数,开始标志的判断以及数据的写入等功能。状态转移过程如图3所示。其中,Idle为空闲状态,count_1_valid为计数有效标志,只有在输入数据处于负边沿时才有效。同时,状态转移到Judge状态,进行判断。

Judge为判断状态,这里设置一个计数器count_1,来对1ms间隔的个数进行计数,通过间隔数的不同判断采集到的码元属于哪种,并跳到对应的状态。前边提到过,为了方便检测,统一采取时钟负边沿进行计数。所以码元0,1以及起始标志的计数应分别为900,800,1 000。但是由于实际时间信息不可能做到绝对精确,所以,这里需要适当的放宽检测门限[13]。经过实际测试,这里选取880-920与780-820分别作为码元0,1的门限,选取960作为起始标志的门限。

Start为开始状态,前文中曾经提到过由于59 s的特殊性,将其作为起始标志来使用。所以当Judge检测到脉冲个数为>960时(59 s在低电平持续1 000 ms),视为检测到起始标志,同时置Start_f=1,采集信息开始。否则,返回Idle状态。

St0,St1状态分别在检测到的脉冲个数为880-920和780-820时由Judge状态跳入,同时分别置St0_f=1,St1_f=1,并且分别在寄存器data中写入二进制信息”0”或”1”。否则,返回Idle状态。

图3 状态转移图

2.3 进位模块设计

由于DCF77码的格式问题,要在第21位开始才是有效的时间信息,但是真实时间的分钟位在0 s的时候就会完成进位,而不会等到21 s再进位。所以需要在时间信息初始化后,完成自动进位操作。然后,再分别在分(data[28]),时(data[35]),日(data[42]),周(data[45]),月(data[50]),年(data[58])信息解析完毕时进行核对。

具体进位规则如下:分每逢60进1,时每逢24进1,月每逢12进1,周每逢7进1;需要特别关注的是月份[14],因为涉及到每年有大月31天和小月30天的区别以及闰年2月份天数的不同,所以根据图4所示的流程进行设计。

图4 月份进位模块设计流程图

2.4 信息解析模块设计

按照DCF77码的格式,根据BCD编码的规则,分别将解析出的时间信息赋给寄存器minute,hour,day,week,month,year。Verilog算法[15-16]描述如下:

assign year=data[50]+2*data[51]+4*data[52]+8*data[53]+10*data[54]+20*data[55]+40*data[56]+80*data[57];assign month=data[45]+2*data[46]+4*data[47]+8*data[48]+10*data[49];

assign week=data[42]+2*data[43]+4*data[44];assign day=data[36]+2*data[37]+4*data[38]+8*data[39]+10*data[40]+20*data[41];

assign hour=data[29]+2*data[30]+4*data[31]+8*data[32]+10*data[33]+20*data[34];assign minute=data[21]+2*data[22]+4*data[23]+8*data[24]+10*data[25]+20*data[26]+40*data[27];

assign second=count_2;

由于minute,hour,day,week,month,year分别在第27,34,41,44,49,57位接受信息完毕,所以均在接受完毕后的下一位将信息赋给对应的值寄存器XX_r,并且与自进位的数值进行判断,如果相同,则保持不变,如果不同,就把赋予的值代替自进位的数值,完成自动纠正。Verilog算法描述如下:

always @ (count_2)

begin

if (count_2==0) minute_r<=minute_r+1'd1;

if (count_2==28) minute_r<=minute;

if (count_2==35) hour_r<=hour;

if (count_2==42) day_r<=day;

if (count_2==45) week_r<=week;

if (count_2==50) month_r<=month;

if (count_2==58) year_r<=year;

end

3 Modelsim仿真验证

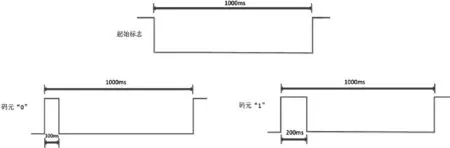

3.1 状态机功能验证

如图8所示,首先查找到起始标志start_f,并开始记录时间信息。通过状态机进行判断,确定码元的类型,并激活不同的标志位st0_f,st1_f,然后在data中分别写入0或这1。直到第59位,这一分钟的信息写入完毕,然后清空data寄存器,准备下一分钟信息的记录[16]。

图5 状态机仿真示意图

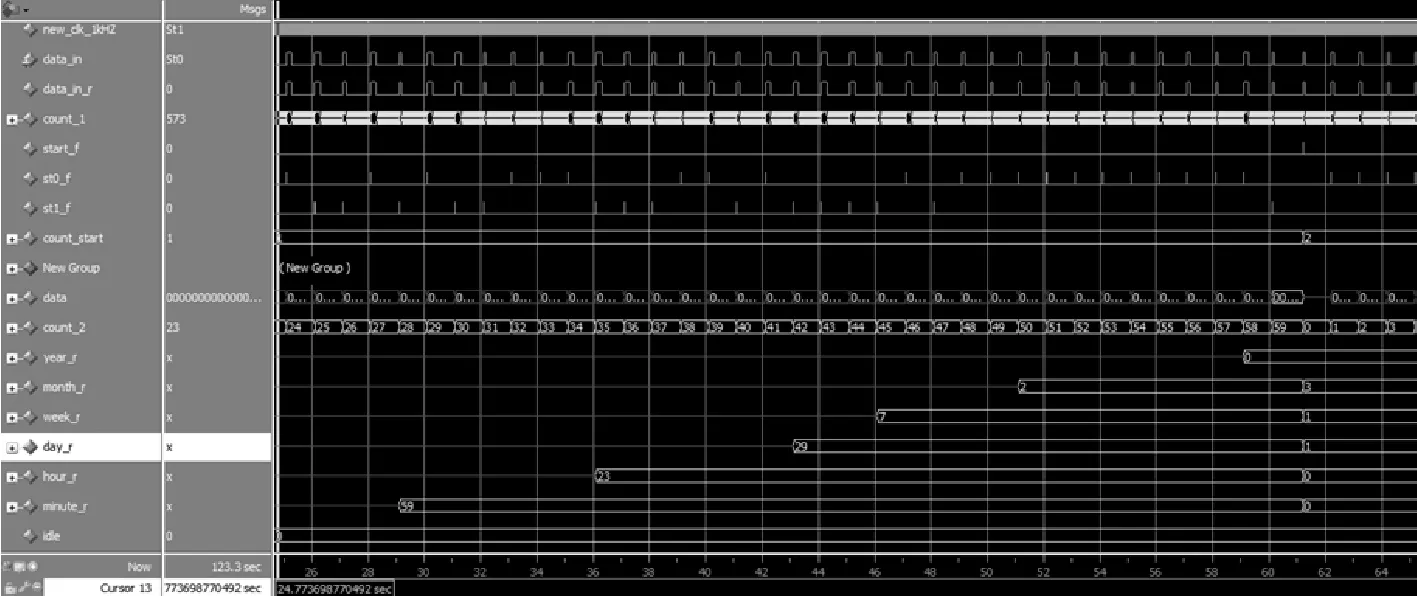

3.2 信息解析验证

由图6可以看出解析得到的时间信息为2000年2月29日23时59分,星期日,与上文所得结论一致,证明解码正确。

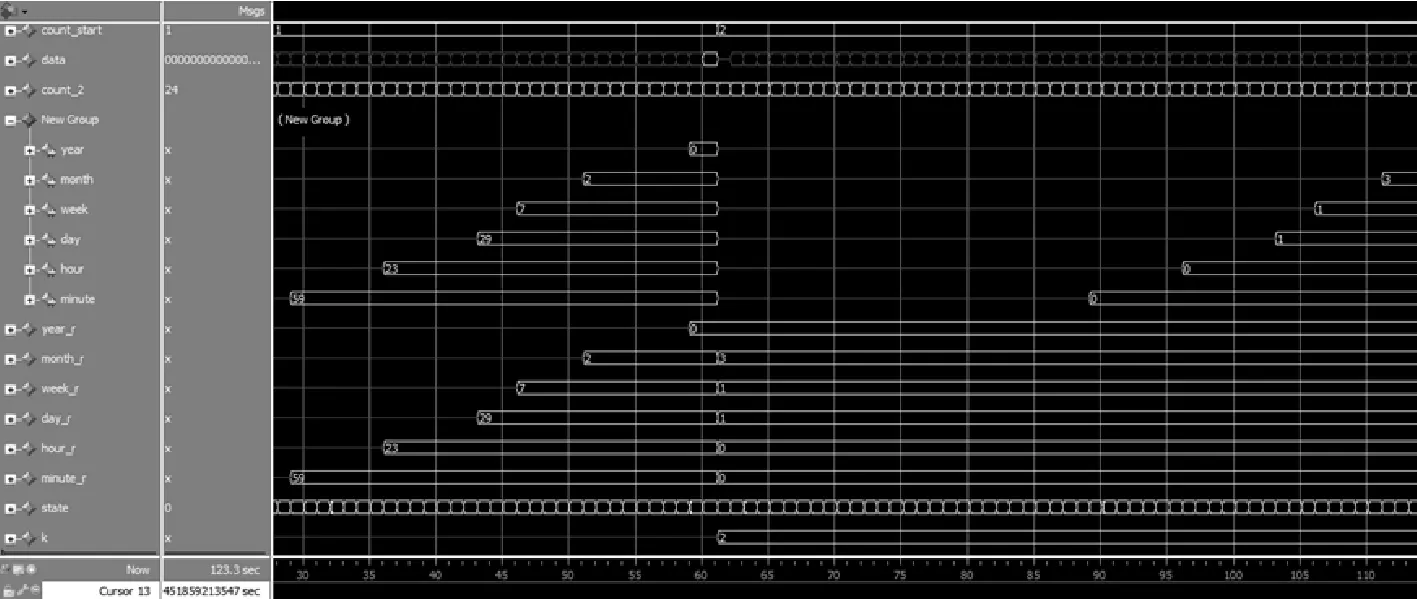

3.3 进位模块功能验证

通过图7中的对比可以看出,New Group中并未采用进位模块设计,所以信息只有在下一分钟的第28,35,42,45,50,58位才会分别解析出来,中间出现了明显的“断层现象”,这与日常计时明显不符。而采用了进位模块设计后则可以在起始标志位之后(00 s)完成自动进位,使时间解码保持了连续性。从图中可以看出,在检测到第2个start_f之后时间变为2000年3月1日0时0分,星期一,验证成功。

图6 解码结果验证

图7 进位功能验证

4 结束语

本文采用有限状态机的方法解决了码元识别的问题,并且使用进位模块设计避免了可能遇到的时间信息解析不连贯的问题,可以成功的对DCF77码进行解码,得到所需的时间信息。整体基于Verilog语言设计,代码简单、移植性强,经过Modelsim仿真软件验证,该解码方案正确可靠。

[1] 于斌,米秀杰.ModelSim电子系统分析及仿真[M].北京:电子工业出版社,2011.

[2] 周国平,屈少君.DCF77时间格式码产生器的设计[C].西安:第20届测控、计量、仪器仪表学术年会,2010.

[3] 高志远,刘长虹.厂站自动化系统中应用网络时间同步技术探讨[J].电力自动化设备,2006,26(7):84-89.

[4] 童宝润.时间统一系统[M].北京:国防工业出版社,2003.

[5] 马红皓,胡永辉.GPS&IRIG-B时间系统分析[J].电子科技,2007,190(7):21-25.

[6] 顾阳阳,付道文.基于FPGA的IRIG-B码解码器设计[J].电子科技,2015,28(5):39-42.

[7] 杨志刚,郑丽丽.IRIG-B码终端中闰秒时间的处理[J].电子科技,2013,26(6):89-93.

[8] 康华光.电子技术基础数字部分[M].北京:高等教育出版社,2004.

[9] 卢伟明,卢伟平.基于FPGA的IRIG-B(DC)码解码[J].现代电子技术,2012,35(11):88-90.

[10] Zhou Caiqin,Li Shizhong,Liang Guoqiang.Design of IRIG-B(AC) encoder based on FPGA[J].Journal of Measurement Science and Instrumentation,2015,6(3):291-294.

[11] 秦娟,徐月超.利用FPGA的IRIG-B码解码新方法[J].信号处理,2015,31(12):1654-1657.

[12] 周国平,邢灿华.IRIG-B格式时间编码电路的设计[J].机械制造与自动化,2005,34(2):88-90.

[13] 王丽敏,胡永辉.基于FPGA的IRIG-B(DC)码的解码方案设计与实现[J].时间频率学报,2012,35(4):228-234.

[14] 贾磊,崔永俊等.基于FPGA的IRIG-B(DC)码解码卡的设计[J].计算机测量与控制,2015,23(6):2143-2155.

[15] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[16] 张明.Verilog HDL实用教程[M].成都:电子科技大学出版社,1999.

Design of a DCF77 Code Decoding Scheme

ZHOU Zhenzhou1,XI Ziqiang1,WANG Ping2

(1.Hubei Collaborative Innovation Center for High-efficiency Utilization of Solar Energy, Wuhan 430068, China;

2. School of Electronic Information and Electrical Engineering, Shanghai Jiaotong University, Shanghai 200240, China)

A decoding scheme based on FPGA is proposed with emphasis on analyzing and processing code element re-cognition. A FSM is designed for recognition of different code-elements and data recording. Modelsim functional simulation validates the accuracy and availability of the scheme. Compared with the IRIG-B code, the proposed scheme adds the week information at a frame length of only 60 bit, which is the same with time radix. This scheme has the advantage of simplicity, stability and easy implementation.

DCF77 code; decode; finite-state machine; code-element recognition

2016- 07- 27

周振洲(1991-),男,硕士研究生。研究方向:数字化故障录波器。席自强(1960-),男,博士,教授。研究方向:电能质量检测与控制技术。

10.16180/j.cnki.issn1007-7820.2017.06.023

TN919.3+1

A

1007-7820(2017)06-085-04