单片FPGA的小型非制冷红外机芯设计

顾 鑫, 曹丹华, 吴裕斌, 栾永昕, 王伟成

(1.华中科技大学 光学与电子信息学院,湖北 武汉 430074; 2.江苏北方湖光光电有限公司,江苏 无锡 214035; 3.南京大学 软件学院,江苏 无锡 210000)

单片FPGA的小型非制冷红外机芯设计

顾 鑫1,2, 曹丹华1, 吴裕斌1, 栾永昕2, 王伟成3

(1.华中科技大学 光学与电子信息学院,湖北 武汉 430074; 2.江苏北方湖光光电有限公司,江苏 无锡 214035; 3.南京大学 软件学院,江苏 无锡 210000)

针对传统的基于数字信号处理器(DSP)+现场可编程门阵列(FPGA)的非制冷红外机芯平台存在体积大、功耗大、实时性差、系统集成度低等不足,提出了一种基于单片FPGA的小型化非制冷红外机芯平台设计。针对25 μm非制冷红外探测器,为满足小型化、低功耗要求,平台在采用先进的FPGA处理器和DDR3存储器技术的同时,将硬件逻辑算法与NIOS Ⅱ软核相结合,完成对红外探测器的时序驱动、温度控制、图像的非均匀性处理、图像增强以及各种人机接口控制。实验结果表明:该系统成像质量较高,系统功耗小于2 W,系统延时小于0.5 ms,系统具有较强的可拓展性。

非制冷红外机芯; 现场可编程门阵列; IP核; NIOS Ⅱ

0 引 言

非制冷红外机芯[1]有着广阔的应用前景,我国在此领域与国际先进水平还存在较大差距。国内单位在非制冷机芯开发的时候往往采用基于现场可编程门阵列(FPGA)+数字信号处理器(DSP)的处理架构[2,3],其中FPGA负责探测器的时序驱动、A/D数据采集和一些简单的控制处理,DSP负责复杂图像算法的运算。这种机芯由于采用了双处理系统的架构存在体积和功耗过大的问题,同时还存在实时性较差、算法可移植性差等问题。这些弊端决定了该处理架构不适用于一些特别的定制领域,如手持便携设备、高速图像采集设备等。

FPGA是一种大规模可编程芯片,其本身存在着编程灵活、并行快速、模块化可移植性高等特点。随着芯片技术的发展FPGA内部又引入了NIOSⅡ软核[4],这更是弥补和加强了其作为系统主芯片的软硬件集成控制力。

本文采用单芯片的处理架构将探测器时序驱动、A/D釆集处理、非均匀性校正[5]、图像处理、人机通信和I/O控制等功能全部集成在一块FPGA芯片上,并采用分时复用的DDR3仲裁技术使多个图像处理算法共享DDR3内存。实现紧凑化、小型化、低功耗机芯设计。系统实验证明了该非制冷红外机芯成像质量良好、功耗较低、实时性较好、体积较小。

1 非制冷机芯总体设计

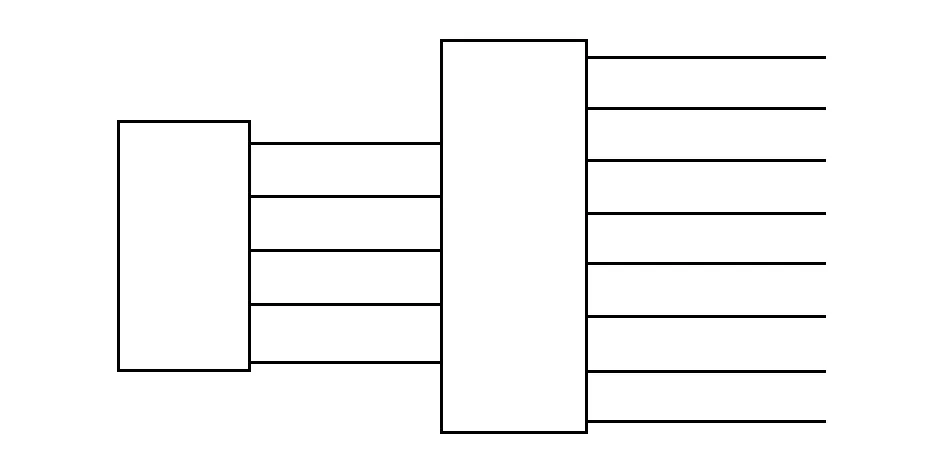

非制冷红外机芯由探测器,驱动模块,FPGA控制模块和电源模块4部分组成,如图1所示。

图1 非制冷机芯组件整体设计

其中,探测器采用国产25 μm氧化钒探测器。FPGA控制模块共有2片DDR3,其中一片作为NIOSⅡ运行的外部存储器,另一片则用来存储图像及校正数据,FLASH用来存储一些非均匀性参数以及其他需要掉电存储的信息供开机后调用。硬件上,FPGA芯片选用 Cyclone 5系列的5CEFA7F31C7NES;DDR3选用MT41J18M16JT—125;FLASH芯片选用M25P64。整个系统中FPGA首先对探测器发送工作时钟、积分时间、TEC参数、片上非均匀性校正(OCC)参数等配置及校正信号,为探测器正常工作提供正确的时序,在保证探测器能正常工作的情况下,对探测器送来的14 bit量化图像信号进行红外图像算法处理,这些处理包括单点校正算法[6]、两点校正算法[7]、盲元补偿、直方图均衡图像增强[8]、非均匀性校正等。在完成各项时序控制和实时图像处理后,红外视频信号将在PAL制模拟监视器上显示。

2 FPGA的定制与交互设计

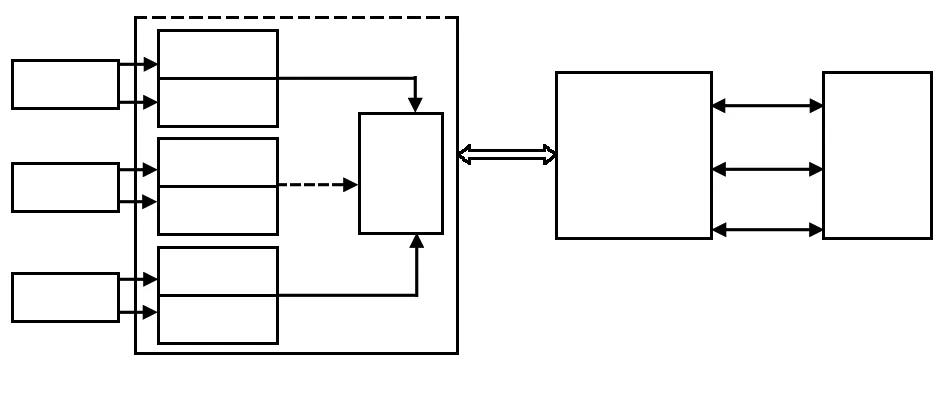

整个FPGA系统由NIOS Ⅱ,控制寄存器组和外部硬件3个部分组成,系统定制如图2所示。

图2 FPGA系统定制

NIOS Ⅱ为系统的控制核心,各个逻辑模块为具体功能实现采用硬件逻辑语言(VHDL)满足高实时性。控制寄存器组为独立外设IP核,用来存储各个逻辑模块的数据和控制指令。NIOS Ⅱ与逻辑模块之间通过Avalon总线与控制寄存器组进行数据传递和指令下达。人机控制按键部分采用I/O口经Avalon总线与NIOS Ⅱ交互。其他外部硬件也是通过各自IP核驱动NIOS Ⅱ读写。系统工作时NIOS II对传来的串口指令、按键状态进行存储译码后转入不同的流程语句处理,并调用各个功能逻辑模块得到所需的输出图像。

比较发现,相比传统的DSP+FPGA架构的系统而言,由于该系统图像处理部分采用硬件逻辑语言设计,其实时性明显要高于前者;同时系统采用FPGA内部集成的NIOS Ⅱ软核作为中央控制器,提出了一种基于控制寄存器组的软硬交互的控制方式,将众多功能控制集成于一组寄存器,通过编址实现控制,具有较高的集成度和可控性。而以上功能仅需要一片芯片即可实现。

3 系统软件设计

非制冷红外机芯软件设计包含2部分组成,其中对实时性要求较低的外部控制、以及数据初始化部分通过NIOS Ⅱ程序完成,对实时性要求较高的探测器时序驱动、图像处理算法和通信部分通过硬件逻辑语言实现。

3.1 非制冷机芯FPGA逻辑程序设计

3.1.1 探测器时序驱动设计

探测器工作需要FPGA提供正确的时序,其中包括输入时钟(SCL)、帧使能信号(FS)、上电复位信号(Res_N)、配置信号(SDL,SDH)。像素时钟6 MHz,探测器时钟频率(SCL)为像素时钟频率的6倍。FS为高电平期间,SDL配置图像的行周期、积分时间。FS的下降沿为一帧图像的开始,此时OCC图像校正数据通过SDL和SDH输入到探测器,每行输入一次。上电后驱动模块首先从DDR中获得探测器配置参数,然后实时配置红外探测器。驱动模块具体设计如图3所示。

图3 探测器时序驱动模块设计

驱动模块正常工作前需要为每个像素点寻找最优的片上非均匀性校正(OCC),本文通过模块内的算法,分析红外数据“videodata”的均匀性,不断调整OCC输出直至“videodata”达到设定的均匀性指标。同时探测器时序驱动模块也可以通过Avalon总线NIOS Ⅱ相连, NIOS Ⅱ读取实时配置的OCC数据和所对应的图像数据,通过串口传至上位机,利用上位机软件进一步分析OCC数据。

3.1.2 DDR3仲裁控制设计

传统的DSP+FPGA设计往往常用SRAM或者是SDRAM,SRAM的读写速度最高为100 MHz,而SDRAM最高位167 MHz,较低的运行速度直接导致了红外系统需要采用4片或更多存储器芯片,增加了系统体积和功耗。如图4所示本文采用DDR3的设计。

图4 DDR3仲裁模块控制流程

DDR3有较高的运行速度可达1 600 MHz,而红外图像处理的像素时钟频率较低为6 MHz,通过采用DDR3仲裁模块设计可以协调各个图像处理算法的读写需求,只需要一片就能满足系统运行。仲裁模块采用异步时钟缓冲技术,各图像处理模块只需要对仲裁模块提出访问申请并给出数据、地址、时钟等信号就能在周期内完成操作而不影响其他模块的读写。

3.2 非制冷机芯NIOS Ⅱ软核设计

红外机芯的NIOS Ⅱ配置通过Qsys软件生成,Qsys是ALTERA最新一代的可视化SOPC[9]工具。NIOS Ⅱ程序通过不同地址设定读取各个控制器和外部IP核的数据,并向其发送指令。NIOS Ⅱ主要功能流程如图5所示。

图5 NIOS II程序流程图

NIOS Ⅱ在上电初始化时负责将探测器参数从Flash中写入SDRAM;初始化完成以后,NIOS Ⅱ等待上位机指令,并根据指令调用各个功能逻辑模块,更新图像及图像界面中的参数。

4 实验结果及其分析

4.1 OCC

受材料、工艺影响国产非制冷红外焦平面探测器的各个像元之间的非均匀性不如国外器件, 会影响系统成像质量,降低空间分辨率和温度分辨率。国产探测器提供了一种前端校正手段,即OCC,通过每帧设定并发送OCC数据给探测器保证输出响应的一致性。图6为通过示波器得到的OCC配置前后的探测器每帧数据的电压输出响应(观察背景为均匀黑体)。

图6 探测器输出波形

图6中ⓐ,ⓑ采样点的电压差为电压极差,观察图6(a)发现在OCC配置前探测器输出电压分布极差达到2.5 V,图像均匀性较差。为了改善输出响应的一致性,通过程序计算OCC校正数据并配置,使探测器输出稳定在AD采样区间内基准电压值附近。图6(b)为OCC配置后的一帧数据电压输出,其电压分布极差得到了改善达到了460 mV。

4.2 红外图像处理

虽然OCC校正能保证一定的图像非均匀性,但成像质量仍不高,为了提高图像质量以及便于观察,需要后期对探测器数据进行两点校正、图像增强等工作,成像效果如图7和图8所示。

图7 两点非均匀性校正

图8 红外图像增强

观察可以发现:两点非均匀性校正算法去除了图像中的非均匀竖条纹,图像增强算法显著加强了图像边缘的轮廓感。

4.3 机芯功耗和实时性测试

为了测试机芯的性能我们将FPGA机芯与基于DM642 DSP芯片的非制冷红外机芯做了对比,其结果如表1所示。

需要指出的是,实时性是指图像处理系统的延时量,具体值为图像输入信号与图像输出信号阶跃点的时间差。通过对比可以发现:基于FPGA的红外机芯无论是在体积、功耗还是实时性方面都优于传统DSP机芯。

5 结 论

本文介绍了一种针对国产非制冷探测器的红外机芯设计,设计采用以单片FPGA为核心的电路设计,通过SOPC技术及NIOSⅡ将驱动程序、图像处理算法、应用程序与硬件接口有效结合,在功耗、体积、实时性上相对传统DSP红外机芯有较大优势。实验结果显示,该红外机芯有着较高的图像均匀性和成像质量。该系统的完成对非制冷红外机芯的国产化和小型化有着重要的意义。

[1] 冯 涛,金伟其,司俊杰.非制冷红外焦平面探测器及其技术发展动态[J].红外技术,2015(3):177-184.

[2] 王 磊,王宝珠,薛双苓,等.基于DSP+FPGA的红外热成像伪彩色变换系统[J].制造业自动化,2013,35(7):149-152.

[3] 黄战华,杨鹤猛,孙立彬,等.一种基于DSP+CPLD的低功耗实时红外成像系统实现方法[J].光学技术,2012(1):14-18.

[4] 张天恒,叶 伟,王阳阳,等.基于SOPC的便携式高精度频率仪设计[J].仪表技术与传感器,2015(5):34-37.

[5] 薛 慧.红外焦平面阵列非均匀性校正方法研究[D].哈尔滨:哈尔滨工业大学,2007.

[6] 候良科,杨俊刚,邓新浦,等.含运动目标的红外图像非均匀校正算法[J].传感器与微系统,2015,34(8):142-148.

[7] 杨正宇.基于SoC的IRFPA非均匀性校正研究[D].成都:西华大学,2010.

[8] 陈 钱.红外图像技术及发展趋势[J].红外技术,2013,35(6):311-318.

[9] 刘紫燕,冯 亮,祁 佳.一种基于FPGA的实时视频跟踪系统硬件平台设[J].传感器与微系统,2014,33(7):98-102.

Design of miniaturized uncooled infrared movement based on FPGA

GU Xin1,2, CAO Dan-hua1, WU Yu-bin1, LUAN Yong-xin2, WANG Wei-cheng3

(1.School of Optical and Electronic Information,Huazhong University of Science and Technology; Wuhan 430074,China; 2.Jiangsu North Huguang Opto-Electronics Co Ltd,Wuxi 214035,China; 3.SoftWare Institute,Nanjing University,Wuxi 210000,China)

Aiming at problem that traditional uncooled infrared imaging system which based on DSP+FPGA has many disadvantages such as large volume,high power consumption,poor real-time performance,low system integration,and so on,a design of miniaturized uncooled infrared imaging system based on FPGA is proposed.The design aims at 25 μm uncooled infrared detector.The latest FPGA processor and DDR3 memory technology are adopted to meet the requirement of miniaturization and low power consumption.A novel solution of combination of hardware logic algorithm and NIOS Ⅱsoft core architecture is proposed.By this way,complete timing driving of infrared detector,temperature control,non-uniformity processing of image,image enhancement,man-machine interface control.Experimental results show the system owns characteristics of higher imaging quality,power consumption of system is less than 2 W,system delay is less than 0.5 ms and the system can be easy extended.

uncooled infrared movement; FPGA; IP core; NIOS Ⅱ

2016—06—08

10.13873/J.1000—9787(2017)06—0083—03

TN 216

A

1000—9787(2017)06—0083—03

顾 鑫(1979-),男,博士,高级工程师,主要从事模式识别、人工智能图像处理等技术研究。