基于FPGA的自适应解调器设计

郭 京,朱晓峰,李双明

(中国人民解放军92941部队第110所,辽宁 葫芦岛 125001)

基于FPGA的自适应解调器设计

郭 京,朱晓峰,李双明

(中国人民解放军92941部队第110所,辽宁 葫芦岛 125001)

IRIG-B(AC)码广泛应用于航天测控系统的远距离时间同步,由于在传输过程中信号易受干扰且存在路径传输时延,因此采用IRIG-B(AC)码实现时间同步其精度往往较差。为满足远距离高精度时间同步要求,针对IRIG-B(AC)码同步误差较大问题,提出一种基于FPGA的数字化解调方法。该方法采用全数字化软件设计,具备相位自动判别功能,针对不同调制比和不同输入幅值的IRIG-B(AC)码,能够实现快速自适应解调译码。测试结果表明,该方法抗干扰能力强,工作稳定可靠,使IRIG-B(AC)码的时间同步精度得到极大提升,甚至优于1 μs。

IRIG-B(AC);现场可编程门阵列;相位识别;时间同步

0 引言

现代时间同步技术主要包括短波授时[1]、长波授时[2]、卫星授时[3]、IRIG-B码授时[4]、NTP授时[5]和PTP授时[6]等多种时间同步方法。短波授时由于信号不稳定、易受干扰、信号衰落明显、噪声大,其应用受到较大限制;长波授时抗干扰性强、信号稳定、传输距离远,但授时精度较差[7];卫星授时应用较为广泛,主要包括GPS、北斗和GLONASS三个卫星系统,按照工作方式又可分为卫星单向授时[8]、卫星共视比对[9]和卫星双向比对授时[10]等;NTP授时主要应用于网络时间同步,授时精度仅在ms级[11];PTP授时具备路径时延修正功能,可实现亚μs级的时间同步精度[12];IRIG-B码作为目前国际通用的一种标准时间同步码型应用最为广泛[13],特别在通信、电力、金融、控制、测量以及航天军工等领域,其时间同步均采用IRIG-B码授时技术为整个系统提供统一的时间基准。IRIG-B码主要包括IRIG-B(DC)码和IRIG-B(AC)码2种(以下简称B(DC)码和B(AC)码)[14]。B(DC)码同步精度高,可实现ns级的时间同步误差[15],但传输距离短,适用于系统内设备的时间同步;B(AC)码同步精度相对较差,但可以通过时延补偿的方式进行修正,相比B(DC)码,其优势在于更适合远距离信号传输。在现代靶场中,由于各参试站点比较分散,为实现总站和各分站之间的时间同步,主要采用B(AC)码实现整个系统的时间同步。文献[14,16]采用模拟方法从B(AC)信号中提取1 pps信号,其解调器同步精度能达到10 μs,但不支持相位自适应功能。本文采用数字化解调方法实现B(AC)码的时间同步,利用双极性解调法完成正弦波信号的极性自动识别,并通过相位补偿和误码修正技术提高B(AC)码的时间同步精度和工作可靠性。

1 B(AC)码特性

IRIG-B码包含100个码元,每个码元的宽度均为10 ms。B(DC)码采用BCD编码表示秒、分、时、天和年等时间信息,每个脉冲的前沿为码元的准时点。时间编码采用脉宽调制进行编码,位置标示位P0、P1…P9以及基准码元Pr均为脉宽8 ms的码元,脉宽为2 ms的码元表示二进制数“0”,脉宽为5 ms的码元表示二进制数“1”[17]。B(AC)码则是对B(DC)码进行1 kHz载波调制后的交流码信号,低幅值正弦信号表示低电平,高幅值正弦信号表示高电平。B(DC)码的每个码元和B(AC)码的对应关系如图1所示。

图1 B(AC)码调制信号

B(AC)码虽然常用于远距离传输,但经过长距离的信道传输后,其信号幅度经常受到削弱,且可能引入较大的环境噪声,甚至会发生信号畸变,产生误码。传统的B(AC)码解调解码设备,自适应能力比较差,锁定性能差对信号幅度和信噪比要求较高,难以提供高可靠和高精度的基准时间信息。此外,现代靶场为实现快速机动性,配置了很多移动车载站,设备更换新站点后需要重新连接总站提供的B(AC)码信号,可能会出现B(AC)码输入接反的情况,造成输入信号相位反向180°,虽然时码终端设备仍然可以正常解码,但时间同步误差会达到500 μs以上,导致系统同步时间精度变差,因此对时间统一系统提出了B(AC)码解调器需具备相位识别功能[17]。

2 B(AC)码解调器设计

2.1 总体设计

系统由隔离变压器、低通滤波器、AD转换器、FPGA、DA转换器、运放、光电耦合器和接口电路等组成,如图2所示。B(AC)码通过隔离变压器和低通滤波器完成输入信号的隔离和滤波,利用AD转换器实现模拟量信号采集,再由FPGA进行采集数据的处理,实现B(AC)码的解调译码,从中提取出精确时间信息,生成1 PPS、B(DC)及其他基准时间信号,再通过输出光耦隔离以及接口电路输出B(DC)码。调制器能够利用DA转换器将生成的PWM信号调制成1 kHz交流信号,并根据高、低电平控制输出正弦信号的幅值高低,从而获得调制比为10∶3的B(AC)码信号输出。

图2 系统组成结构

由于B(AC)码在远距离传输过程中容易受到干扰,经常会发生波形畸变,如何消除引入的信号干扰、解决波形畸变带来的解调误码问题是系统设计的关键。同时还需要具备信号消抖技术,准确提取稳定的1 PPS秒信息,实现B(AC)码相位自动识别和相位补偿功能,能够满足正向和反向B(AC)码均可自适应解调译码。从如图2中也可看出,系统设计的主要功能均需在FPGA软件实现。

2.2 FPGA软件设计

FPGA软件设计是解调器的核心设计部分,采用了Verilog HDL语言实现软件编程,主要包括:解调器、译码器、误码判别、时延修正、锁定判决和时间信号发生器等功能模块。

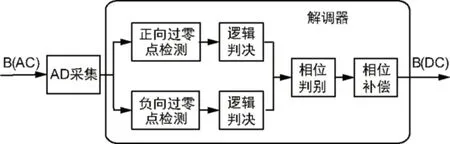

解调器主要功能是将B(AC)码转化为B(DC)码,包含过零检测、逻辑判决、相位识别和相位补偿等4个子模块,如图3所示。采集到的B(AC)码信息送入FPGA后,一路通过正向过零检测器,另一路通过反向过零检测器,在每个正弦周期内均可提取出一个正向过零点和一个反向过零点,信号过零点包含了关键的秒信号起始时刻点等基准时间信息。过零点信息结合逻辑判决器即可将B(AC)码解调,转变为B(DC)码。

图3 解调器工作原理

(1)

采用双极性判别法实现对正向和反向输入B(AC)码的自动识别,通过相位识别器自动完成极性判别并解调出正确的B(DC)码,如图4所示。

图4 双极性解调示意

从正向解调和反向解调的波形图可以看出,相位超前半个正弦周期的信号为正确的B(DC)码。由于低通滤波器、AD转换器以及FPGA软件处理模块会导致输入B(AC)码的相位延迟,因此需要利用相位补偿器进行时延补偿。译码器从解调的B(DC)码提取出年、天、时、分、秒以及1 PPS等时间信息。

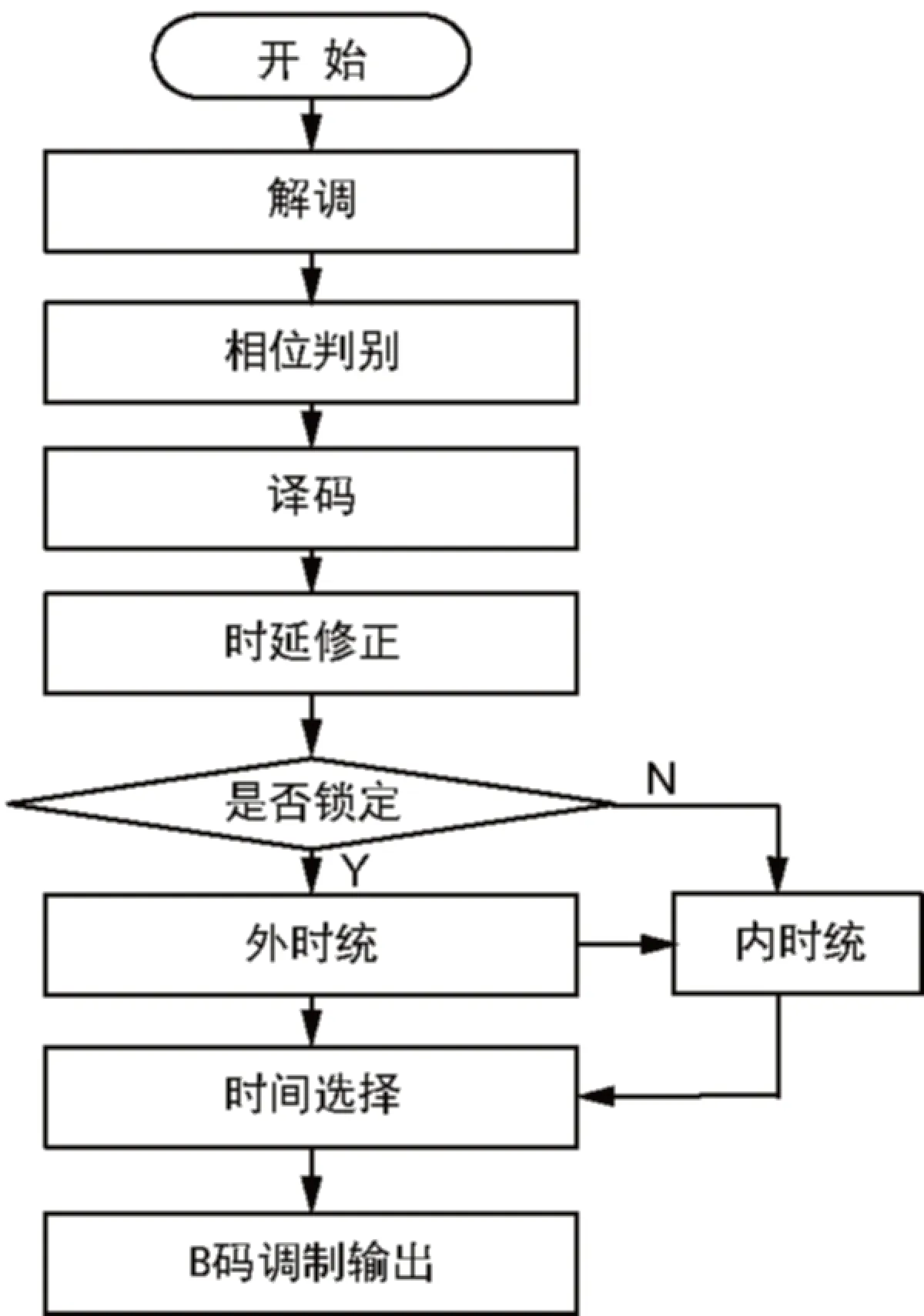

B(AC)码信号在传输过程中会因波形出现畸变导致解调误码产生,因此需要对接收的信号进行误码判别,将前一帧接收到的时间加1 s后和当前帧接收的时间进行比较,如果相等则认为当前帧正确,否则判断该帧为误码。如发现误码,则判定信号失锁;如连续3帧时间正确,则可判断信号锁定,同时将当前时间加1 s作为译码器下一秒输出的时间信息。时延修正用于对B(AC)码远距离传输所产生的路径时延进行补偿。时统产生器则将得到的BCD时间码生成各种基准时间信息输出,并在外输入信号断开或失锁时,能够自动进入守时工作状态。时统产生器主要由外时统、内时统、时间选择器以及基准时间信号产生器组成。当处于锁定状态时,时统产生器以外时统作为时间源;当失锁时,时统产生器以内时统作为时间源;失锁时,内时统会以外时统最后一次有效时间作为起始时间,每秒自动进行加1 s处理,确保输出时间信号的连续性和准确性。系统软件流程图如图5所示。

图5 软件流程

3 测试结果分析

常温25 ℃、湿度42%、传输线缆长度2 m的情况下,经过测试,正向和反向B(AC)码均能正确解码,时间同步精度优于1 μs,B(AC)码同步精度测试结果如表1所示。

表1 B(AC)码同步精度

从表1中可以看出,正向B(AC)码和反向B(AC)码的时间同步精度有差异,这主要是由于信号的零点漂移导致正向过零点和反向过零点采样误差造成。此外,低幅值信号的时间同步精度较差,则是因为小信号达到过零点判决门限需要的时间更长,致使实际提取的过零点信号相对于大幅值信号提取的过零点相位偏移较大,从而导致时间同步精度变差,如图6所示。

图6 正弦信号过零点提取

该方法具备相位自动判别功能,能够自适应正向和反向的B(AC)码信号,解调精度可实现小于1 μs,相比文献[5-6]的B(AC)同步指标提高了10倍,远优于国内同类产品。相比采用比较器法提取过零点和全波整形实现相位自适应的模拟处理方法,本文方法更灵活、方便,可靠性更高,而且减少了硬件设计复杂度,降低了成本。

4 结束语

本文提出的基于FPGA的数字化B(AC)码解调设计能够实现精确时间同步,其技术指标已处于国内领先水平,可极大地提高航天测控系统的时间同步精度。实际应用结果表明,设备工作稳定可靠、抗干扰能力强,对于远距离传输且具有波形畸变的B(AC)码能够正确解码。系统中采用的AD转换器为ADS805E[16],采样速率仅有5 MHz,且并未调整输入信号的零点漂移,后续研究可在以上两方面进行改进,能够进一步提高B(AC)码同步精度。

[1] 蒙智谋.BPM短波时码授时发播技术方案[J].时间频率学报,2014,37(3):145-150.

[2] 魏孝锋,车爱霞,乔建武,等.光纤传输高精度时频信号在长波授时中的应用[J].时间频率学报,2015,38(2):95-100.

[3] 龚小维.基于北斗二号/GPS授时的靶场时间统一系统设计[D].南京:南京理工大学,2013.

[4] 李群续,张沪玲,李冠宇.岸船卫星双向对时应用系统IRIG-B码设计[J].无线电工程,2010,40(2):42-43.

[5] 毛瀛洲.NTP网络授时系统设计与实现[D].济南:山东大学,2008.

[6] IEEE1588-2008.IEEE Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems[S].

[7] 李瑞敏.长波授时附加二次相位因子ASF时延修正的研究[D].西安:中国科学院国家授时中心,2012.

[8] 张立新,杨文强.单项卫星授时体制及精度分析[J].空间电子技术,2001(3):1-3.

[9] 赵当丽,胡水军,翟慧生,等.基于卫星共视技术的电网时间同步[J].电力科学与技术学报,2011,26(3):20-24.

[10] 孟凡芹.基于星地双向时间比对的卫星钟差确定方法[D].西安:中国科学院国家授时中心,2013.

[11] 黄沛芳.基于NTP的高精度时间同步系统实现[J].电子技术应用,2009,35(7):122-127.

[12] 李洪亮.基于PTP协议的高精度网络时间同步系统的设计与实现[D].天津:天津大学,2012.

[13] 童宝润.时间统一系统[M].北京:国防工业出版社,2004.

[14] 陈 涛,曹永刚.IRIG-B码数字解调技术[J].光学精密工程,1999,7(2):73-75.

[15] 林习良,唐晓春.基于SDH的IRIG-B(DC)码时间信号传输方案设计[J].无线电工程,2005,35(6):32-34.

[16] 佟 刚,崔 明,曹永刚,等.MSP430F149在IRIG-B码解码中的应用[J].计算机测量与控制,2007,15(11):1 597-1 598.

[17] GJB2991A-2008.B时间码接口终端通用规范[S].

Design of Adaptive Demodulator for IRIG-B(AC)Code Based on FPGA

GUO Jing,ZHU Xiao-feng,LI Shuang-ming

(The110thInstituteofUnit92941,PLA,HuludaoLiaoning125001,China)

IRIG-B(AC)code is widely used in aerospace measurement and control systems for long-distance time synchronization.However,due to the signal interference and transmission delay during the process of transmission,the accuracy of time synchronization realized by IRIG-B(AC)code is quite low.In order to meet the requirement for long-distance high accuracy time synchronization,and considering the synchronization error of IRIG-B(AC)code,a novel digital demodulation method based on FPGA software is proposed.This method adopts an all-digital software design with an automatic phase discrimination function.According to the different modulation ratios and input amplitudes of IRIG-B(AC)codes,the method can realize fast adaptive demodulation and decoding.The test results show that this method has a strong anti-interference capability and operates stably and reliably.With the function of this method,the time synchronization accuracy of IRIG-B(AC)code is greatly improved,even better than 1 μs.

IRIG-B(AC);FPGA;phase identification;time synchronization

2017-02-28

10.3969/j.issn.1003-3106.2017.06.19

郭 京,朱晓峰,李双明.基于FPGA的自适应解调器设计[J].无线电工程,2017,47(6):79-82.[GUO Jing,ZHU Xiaofeng,LI Shuangming.Design of Adaptive Demodulator for IRIG-B(AC)Code Based on FPGA[J].Radio Engineering,2017,47(6):79-82.]

V249

A

1003-3106(2017)06-0079-04

郭 京 男,(1975—),硕士,高级工程师。主要研究方向:测控及水面靶标总体。

朱晓峰 男,(1981—),工程师。主要研究方向:测控及水面靶标总体。