中高频四端口网络频率特性测试仪设计*

李小亮,王丽霞

(黄河科技学院信息工程学院,郑州 450000)

中高频四端口网络频率特性测试仪设计*

李小亮*,王丽霞

(黄河科技学院信息工程学院,郑州 450000)

频率特性测试仪主要用来测量四端口网络的频率特性和相频特性,广泛应用于现代电子、通信等测量领域。基于Altera公司的CycloneⅢ系列EP3C16F256C8芯片,采用DDS技术产生100 kHz~40 MHz的两路正交扫频信号,根据正交调制解调原理和现代显示技术实现对一中高频四端口网络幅频特性和相频特性曲线的测量显示。扫频间隔Δf为10 kHz,幅频特性测量误差小于1 dB,相频特性测量精度优于3°。

FPGA;频率特性;正交调制;DDS

传统的频率特性测试仪设计主要以LC振荡器或压控振荡器为扫频信号源,采用峰值检测或有效值检测方法实现对被测网络幅频特性曲线的测量;采用相位差法实现对被测网络相频特性曲线的测量。主要缺点就是频率漂移严重、最大线性频偏较窄,需要使用多个波段开关切换,电路结构复杂且体积庞大、集成化程度不高、容易受外部因素影响而导致测量精度不够且价格较为昂贵[1]。目前,国外先进的频率特性测试仪主要集中在甚高频、特高频等领域,而中高频段的频率特性测试仪相对缺乏[2]。作者基于FPGA设计,采用DDS技术实现两路正交扫频信号源,对一被测RLC陷波网络进行调制和解调,并经STM32处理器进行数据处理和控制液晶显示器进行显示。

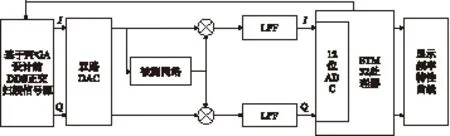

1 整体电路组成

频率特性测试仪主要由基于CycloneⅢ系列EP3C16F256C8芯片的DDS正交扫频信号源、12位的双路数模转换器(DAC)芯片MAX5873、模拟乘法器芯片AD835、有源低通滤波器、STM32处理器及TFT液晶显示屏构成。电路设计框图如图1所示。

图1 四端口网络频率特性测试仪电路组成框图

首先采用DDS技术在FPGA上输出两路正弦正交扫频信号源I和Q,经双通道高速DAC进行数模转换及7阶巴特沃斯低通滤波器滤波后,得到两路正交的模拟信号记为:I=Asin(ωt),Q=Acos(ωt)。设被测网络的幅频特性函数为Z(ω),相频特性函数为φ(ω)。正弦分量经被测网络后输出为:A·Z(ω)×sin[ωt+φ(ω)]。该信号同时作用于两路乘法器输入端,分别与DAC输出的正弦分量和正交分量相乘,假设乘法器的增益为k,则两路乘法器的输出分别为:

uI1=A·Z(ω)·k·sin[ωt+φ(ω)]·Asin(ωt)=

uQ1=A·Z(ω)·k·sin[ωt+φ(ω)]·Acos(ωt)=

图2 基于FPGA设计的正交扫频信号源电路

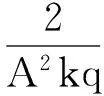

设二阶有源低通滤波器电压增益为q,则经低通滤波器滤除高频分量后:

该直流分量经STM32处理器内部的两路12位ADC模数转换、算法实现后便可得到被测网络的幅频特性和相频特性函数关系[3]:

2 电路实现

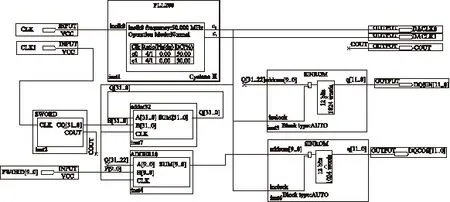

2.1 基于FPGA设计的正交扫频信号源

基于CycloneⅢ系列EP3C16F256C8芯片,采用DDS结构完成正交扫频信号源的设计。电路结构如图2所示,主要包括锁相环电路PLL200、相位累加器电路adder32、移相电路ADDER10、正弦波数据存储器SINROM及频率字扫描电路SWORD 5部分。

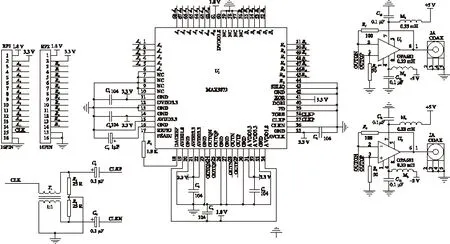

图3 MAX5873双路数模转换电路

IF CLK'EVENT AND CLK='1' THEN

IF CNT32=x"33333332" THEN

CNT32:=x"0020C496";

COUT0<='1';

ELSE CNT32:=CNT32+x"000346DC ";

COUT0<='0';

END IF;

END IF;

CQ<=CNT32;

END PROCESS;

COUT<=COUT0;

END behav;

电路中还设计了扫频方式、频域选择等模块电路。频域选择根据STM32处理器提供的频率字范围、扫频间隔字、扫频字信号发生器基准时钟选择信号,通过模块电路中定义的Generic端口实现扫频频域的切换。

2.2 双路DAC转换及滤波电路

由FPGA输出的两路正交扫频信号为数字量形式的阶梯信号,需要经过DAC转换及低通滤波后再送入被测网络及乘法器电路。本设计使用的DAC芯片为Maxim公司提供的MAX5873。该芯片支持12位总线输入、双路数模转换,刷新速率可达200 Msample/s。具有极高的动态性能和极佳的无杂散动态范围(SFRD)和互调失真(IMD)。其满量程差分输出电流范围可由量程设置电阻RSET(位于MAX5873的17脚和18脚之间)确定,控制输出电流表达式为:

式中,IOUTFS为DAC满量程输出电流,VREFIO选择片内1.2 V带隙基准电源。电路设计中为保证满量程输出电流为20 mA,设置电阻RSET选取1.9 kΩ,结合后级电流电压转换电路,可输出幅度为1 V的电压信号[9]。设计电路如图3所示。

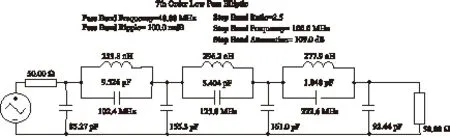

MAX5873芯片差分输出以后,为防止噪声干扰,电路中接入了7阶椭圆低通滤波器,带宽为40 MHz,阻带为100 MHz,且衰减大于60 dB,带内波动小于0.1 dB。其电路设计如图4所示。

图4 7阶椭圆低通滤波器设计

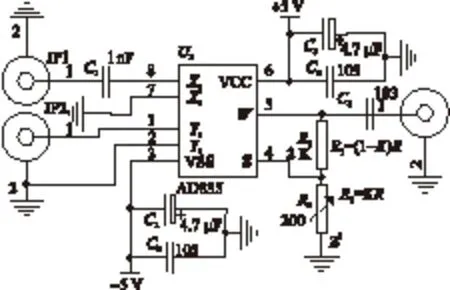

2.3 正交调制电路

图5 正交调制电路

2.4 二阶有源低通滤波器设计

二阶有源低通滤波器主要为了滤除正交调制后高频成分及互调干扰信号。由于扫频信号间隔为10 kHz,扫频周期为1 s,因此整个扫频周期内扫频点数为4K,故二阶有源低通滤波器的截止频率也应设为4 kHz,为留有余量,最终截止频率设计为5 kHz。滤波电路增益设计为2。另外,STM32内部自带的A/D无法对负电压采集,因此在低通滤波电路后级又加入了电压提升电路,使电压输出范围为0~2 V。电路设计中采用高精度低噪声运算放大器OP07搭建而成。

2.5 STM32处理电路及显示

STM32处理器选用增强型的STM32F103VC,使用高性能的ARMR CortexTM-M3 32位的RISC内核,工作频率为72 MHz,内置64 kbyte闪存,具有丰富的I/O端口及包括了3个12位的ADC转换电路,有效降低了外部电路设计的复杂程度,提高了电路的稳定性[10]。电路软件部分包括主程序、键盘扫描、FPGA控制、A/D转换、运算处理及液晶显示等程序。系统主程序首先进行上电复位,进行设备初始化,包括配置系统时钟、定时器、片内ADC及TFTLCD[11-12];然后进行按键扫描,等待选择测量模式和测量频域档位,STM32根据档位选择计算频域控制字、扫频间隔控制字及输出扫频字信号发生器基准时钟控制信号,送给FPGA实现扫频频域的控制;A/D转换子程序对片内AD实现采样时序控制;STM32对转换后的信号进行运算处理,并通过LCD显示子程序输出相应幅频特性曲线或相频特性曲线。主程序流程图如图6所示。

图6 STM32主程序流程图

3 测试结果

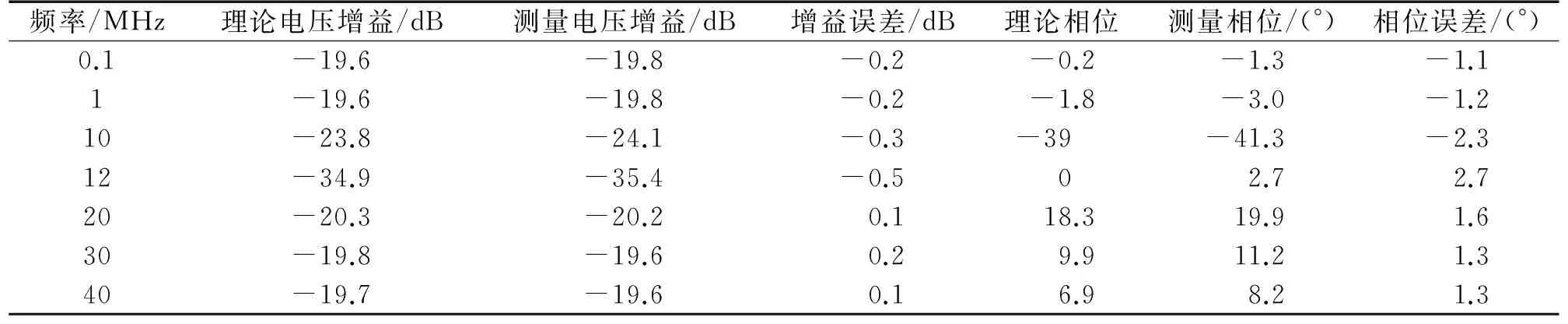

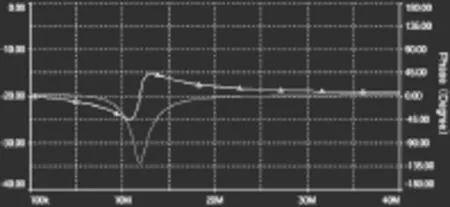

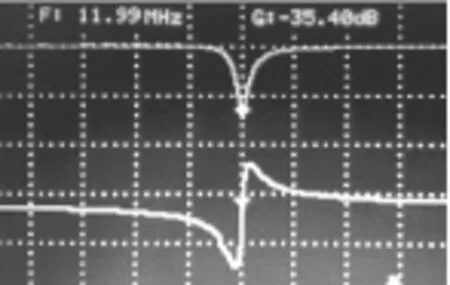

测试电路选择一衰减电路进行测量。回路中心频率为12 MHz。系统上电后默认为全频域扫描,先进行系统的自检和矫正;然后将扫频信号源的输出接入电路输入端,被测电路输出端接入系统输入端,完成频率特性的测试。表1列出了测试网络在衰减电路各频率点的实测数据与理论数据,由此可知,幅频特性测量的绝对误差小于1 dB,相频特性测量绝对误差小于3°,测试中,频率特性测试系统的输入、输出电阻均设计为50 Ω。图7、图8分别为衰减网络频率特性曲线的仿真图形与测量图形。

表1 频率特性测试仪测量数据与误差分析

图7 被测网络仿真图形

图8 被测网络实测波形

4 结束语

本设计采用基于FPGA的DDS技术与单片机技术,并结合Maxim、ADI公司等提供的专用集成电路,根据正交调制解调原理,完成了这一款中高频四端口网络的频率特性测试仪设计。系统控制界面良好,可通过按键选择扫频范围和扫频间隔。通过对一衰减网络频率特性进行测量,测试结果表明可实现100 kHz~40 MHz扫频输出范围,幅频特性测量误

差小于1 dB,相频特性测量精度优于3°,达到了预期设计要求。而且电路中大量采用集成电路设计,提高了系统的集成度和稳定性,缩小了仪器体积,有利于系统的产品化和市场化。

[1] 李尧,孙媛媛,马泽伟. 基于DSP的频率特性分析仪设计[J]. 电子科技,2015,28(1):16-19.

[2] 文时祥,赵菁. 基于DSP的频率特性测试仪设计[J]. 电子科技,2011,24(5):41-43.

[3] 叶朝锋,崔爱芳,袁燕岭,等. 数字式电路系统频率特性分析仪的研制[J]. 清华大学学报(自然科学版),2011,51(12):1792-1795.

[4] 董宝玉,薛严冰,马驰,等. 基于AD9854与STM32的频率特性测试仪设计[J]. 化工自动化及仪表,2014,41(6):655-659.

[5] 潘松,黄继业. EDA技术实用教程[M]. 第5版. 北京:科学出版社,2013:197-200.

[6] 李明,臧凤仙. 基于FPGA的甚高频DDS设计[J]. 微计算机信息,2011,27(2):13-15.

[7] 邓岳平,肖铁军. 基于FPGA的并行DDS信号发生器的设计与实现[J]. 计算机工程与设计,2011,32(7):2319-2323.

[8] 毛敏,王淑仙. 新型直接数字合成式扫频仪的原理和研制[J]. 仪器仪表学报,2004(4):534-537.

[9] 邓安波. OFDM基带和中频信号处理系统研究与实现[D]. 成都:电子科技大学,2015:51-62.

[10] 孙启富,孙运强,姚爱琴. 基于STM32的通用智能仪表设计与应用[J]. 仪表技术与传感器,2010(10):34-36.

[11] 丁红斌,秦会斌,孙顺远. 基于STM32的虚拟示波器的设计与实现[J]. 电子器件,2009,32(6):1007-1010.

[12] 孟瑞丽,宋安,张宏群,等. 一种数字频率特性测试仪的设计[J]. 南京信息工程大学学报(自然科学版),2015,7(2):137-141.

Design of a Frequency Characteristic Tester for Four Port Network in High Frequency*

LIXiaoliang*,WANGLixia

(College of Information Engineering,Huanghe Science and Technology College,Zhengzhou 450000,China)

Frequency characteristic tester is mainly used to measure the frequency characteristic and phase frequency characteristics of four port network,which is widely used in modern electronics,communications and other fields. A method of measuring and displaying amplitude frequency characteristic and phase frequency characteristic curve is proposed according to the orthogonal modulation and demodulation principle and modern display technology. Two channels of orthogonal swept-frequency signal is generated,of which frequency range is 100 kHz~40 MHz by using DDS technology based on a CycloneⅢ EP3C16F256C8 chip of the Altera corporation. The swept-frequency interval of the system,Δfis 10 kHz,which has a precision of 1 dB and phase detection accuracy of 3°.

FPGA;Frequency characteristics;Orthogonal modulation,DDS

项目来源:郑州市重点建设实验室项目(ZZLG201414)

2016-04-11 修改日期:2016-05-17

TN98

A

1005-9490(2017)03-0612-05

C:7310G

10.3969/j.issn.1005-9490.2017.03.019