基于CPCIe的重型采煤机状态监测信号采集板卡设计

张慧慧, 孟令军, 韩朝辉

(中北大学 电子测试技术国家重点实验室,仪器科学与动态测试教育部重点实验室,山西 太原 030051)

基于CPCIe的重型采煤机状态监测信号采集板卡设计

张慧慧, 孟令军, 韩朝辉

(中北大学 电子测试技术国家重点实验室,仪器科学与动态测试教育部重点实验室,山西 太原 030051)

针对重型采煤机在线状态监测对信号采集的需求,提出了一种基于CPCIe架构的高速多通道信号采集板卡的设计方案。方案中使用了Xilinx公司Virtex-6系列的FPGA为主控制器,以TI公司推出的高性能双通道ADC、DAC芯片为信号采集回放单元,结合多片大容量的DDR3 SDRAM作为高速缓存单元,采用FPGA内部集成的PCIe硬核解决方案来构建CPCIe总线接口单元。对信号采集板卡的软硬件设计进行详细的介绍,并进行了仿真测试。实验验证,板卡最高可以在100 MHz采样频率下同时对4路模拟量信号进行采集和传输,PCIe接口数据上传速率不低于800 MB/s;该板卡具有易于升级、灵活性强、应用广泛的特点。

CPCIe总线; 采煤机; 多通道; 信号采集

0 引 言

煤机在运行过程中会出现系统零部件由于冲击、磨损、老化、疲劳等因素引起的劣化和失效等重要信息,因此,对相关信号进行监测、分析和处理,可以监测设备的运行状态,对煤机的状态监测和故障诊断有着至关重要的作用。要实现对煤机状态的实时检测,需要对信号进行多通道、高速采集,为了满足这一需求,设计了一款可靠性强、采样精度高、数据处理实时性强、采样信号多的信号采集系统。CPCIe(Compact Peripheral Component Interconnect Express)总线以其良好的抗震性和通风性得以广泛的使用,其本质上就是使用欧卡的规格实现PCI Express总线。专用的电缆能够延伸总线,提高系统的扩展范围[1-2]。

1 CPCIe多通道信号采集板卡方案设计

CPCIe高速多通道信号采集板卡主要完成对数据的实时采集和传输。该信号采集系统主要包括以下几个单元:前端AD、DA信号转换单元、DDR3高速缓存单元、PCIe总线接口单元以及主控制器FPGA的协调控制单元[3]。其工作原理为:采集到的4路AD信号经过高速缓存单元,然后进入到主控制器FPGA,在FPGA内部完成信号处理,然后将处理后的结果通过PCIe接口上传到主控上位机。同时,也可以将已经处理完成的信息经过DA转换器,传输到下一级设备。本设计将信号处理板卡拆分为信号采集卡(子卡)和主控卡(母卡)进行分离设计。整个信号采集板卡由两块子卡和一块母卡构成。子卡和母卡间通过FMC接口进行互联[4]。

图1为所设计的CPCIe信号采集主控卡与采集子卡。主控卡由两片Virtex6 LX130T系列FPGA作为核心控制接口芯片,对外实现FMC标准接口, CPCIe总线连接器上连接大量LVDS信号线,方便在背板上实现板卡间的通信。FPGA芯片外挂两簇大容量256 MB SDRAM进行数据缓存。FMC子卡接口连接FPGA大量LVDS信号以及GTP高速串行收发器,可实现与AD/DA采集子卡之间的数据接收与发射功能。逻辑控制主控卡使用PCIe硬核接口接入系统CPCIe总线,实现与PC主机的数据、控制命令之间的状态交互。AD/DA采集子卡具有双收双发功能,通过FMC LVDS接口直接将数据下载到接口控制主卡上的FPGA上。

2 板卡硬件电路设计与实现

2.1 时钟网络设计

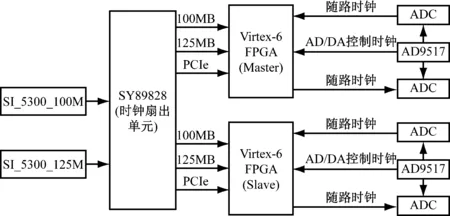

时钟单元是整个系统工作的心脏。本设计提出了一种源同步时钟处理系统[5],所谓的源同步时钟系统,就是指在发送端所传输的数据和时钟源是同步传输的,而且这两个信号的传输路径和延时要完全一致。图2所示为整个板卡的时钟网络设计框图。两片SI5300高精度时钟单元分别为两片Virtex 6 FPGA内部集成的高速串行收发器RocketIO GTP提供高精度时钟,时钟扇出芯片SY89828为两片FPGA与CPCIe主机交互通信提供了相同的参考时钟。信号采集板卡上要满足4路AD能够同时进行转换,并且要实现采样率的可程控化,所以方案中使用了专用时钟激发产生芯片AD9517。为了能够最大程度的实现采样时钟的调控范围,设计中使用了4对LVDS标准的时钟输出。一对作为ADC芯片的采样时钟;一对作为DAC芯片的采样时钟;另外两对通过FMC接口连接到FPGA控制器,实现对采集模块的逻辑时序控制。

图2 信号采集板卡时钟网络设计框图

2.2 DDR3缓存单元设计

缓存单元是高速信号传输系统设计中重要的一环。本设计采用将级联后的DDR3单元封装成多级Virtual FIFO接口的设计。这种设计不仅接口简单,而且利用率较高,对于数据的读写空满状态可以根据需要进行制定,数据输入的位宽也可以自由配置。图3所示为DDR3的多级Vrtual FIFO设计框图。

图3 DDR3的多级Vrtual FIFO设计框图

在DDR3 SDRAM电路设计中,布局布线也尤为重要。多片DDR3之间设计为T型网络拓扑结构,DDR3与FPGA之间尽可能近点,所有DDR3的电源管脚对应一个滤波电容。信号线分组走线。数据线每8位一组,外加相应的DQS和DQM;地址线、控制线、时钟线分为一组。布线时同组信号线在同一层走线,且同组信号线长度误差范围控制在±0.254 mm内。对于差分信号线的等长要使用蛇形走线规则[6-7]。

2.3 CPCIe总线接口单元的设计

对于CPCIe板卡的PCIe总线控制器的设计,采用FPGA内部的PCIe IP核实现。Virtex-6 FPGA的PCIe硬核IP兼容PCI Express V1.0和PCI Express V2.0标准,由于板卡技术指标要求速率不低于800 MB/s。所以设计中只需要FPGA工作在V1.0模式下,采用×4通道(传输速率为1.25 GB/s)。PCIe硬核接口使用的是FPGA内部的高速收发器(GTX Transceivers)资源,CPCIe总线接口相对于CPCI总线接口来说,需要连接的信号线更少。物理接口和标准的PCIe总线相同,所以在整个板卡的硬件电路的设计中,使用了CPCIe接口的物理卡槽设计。其中FPGA与XSP2连接器的连接,完成CPCIe总线架构的搭建[8-9]。

2.4 高速电路板卡关键信号仿真分析

对于高速硬件电路板卡的设计,保证其信号的完整性是必要的工作。所以PCB印制电路板绘制完成后,要对其进行系统的信号完整性分析[9]。主要对设计中的关键信号进行反射、串扰以及EMC电磁辐射仿真和分析,这里给出了信号边沿模式反射仿真结果和控制信号的串扰仿真结果,分别如图4、5所示。

图4 信号边沿模式反射仿真结果

图5 FPGA_WE#信号串扰仿真结果

图4是对DDR3模块的数据线data[0]进行仿真分析,驱动信号为边沿模式(上升沿)。由仿真结果可见,data[0]网络驱动端的过冲峰值为5.3 V左右,属于可以接受的范围,则该网络的布线设计符合要求。

图5是FPGA对DDR3单元的写控制信号的串扰仿真分析。仿真结果可以看出,该网络的最大串扰峰值为167.7 mV,小于设定值200 mV,满足设计需求。

3 采集板卡各模块的设计与实现

3.1 DDR3级联缓存单元设计与仿真

高速缓冲单元是由多片DDR3 SDRAM构成的,本设计采用将级联后的DDR3单元封装成多级Virtual FIFO接口,各个接口之间相互独立。各FIFO之间的数据传输主要通过内部的3个状态控制器实现:写数据控制器、命令控制器、读数据控制器[10]。对于DDR3 SDRAM的时序设计采用的是Xilinx的MIG IP核。设计中使用了两簇32位的DDR3缓存单元,一簇设计为2级Virtual FIFO,作为ADC、DAC和FPGA之间的数据缓存。另一簇设计为单级FIFO接口,实现对CPCIe接口上传数据的缓存[11-12]。图6所示为DDR3缓存单元的整体设计结构图。

图6 DDR3高速缓存单元程序设计框图

图7所示为DDR3缓存单元在在线逻辑分析仪chipscope中的仿真结果。其中wr_en为FIFO的写时能,wr_data为FIFO数据输入端,full为FIFO满标志,高电平表示FIFO写满,rd_en为FIFO的读使能,rd_data为FIFO数据输出,empty为FIFO空标志位,高电平表示FIFO读空。由仿真结果可知,DDR3级联后封装成的FIFO读写逻辑时序正确,满足DDR3缓存单元设计要求。

图7 DDR3缓存单元在chipscope中的仿真结果

3.2 PCIe接口协议的逻辑设计与仿真

使用FPGA控制器实现PCIe总线协议,对于用户而言只需要完成事务处理层包(TLP)的封装和编码[13-14]。具体操作就是对用户接口单元进行编程,把需要传送的数据编码成TLP包的格式,导入到PCIe硬核单元,然后选择PCIe的工作模式,实现在PCIe总线上数据的传输。为了完成800 MB/s速率的数据传输,选择了总线主控DMA模式的PCIe操作。Xilinx公司提供了PCIe硬核的时序逻辑程序代码。程序设计的总体思路是通过信号采集板卡作为主控,其主动向PC上位机发起读写数据请求,PCIe信号采集板卡与PC主控上位机之间的数据读写操作基本类似。首先需要PC主控机申请一段连续的物理内存空间,不能被其他应用程序占用;其次采集板卡根据用户数据的规模决定对板卡进行读写操作,并向上位机发送中断请求;PC接收中断后,开始对BAR0内的相关寄存器进行配置,配置完成后启动DMA[15-16];然后板卡内部DMA引擎根据DMA的命令,开始进行存储器读写操作;最后所有数据转换结束后,板卡主动向PC机发送结束中断。图8所示为信号采集板卡通过DMA方式进行读写操作的流程图。

(a) DMA方式写数据操作

(b) DMA方式读数据操作

图8 DMA方式读写操作流程图

板卡向上位机发送了1 KB的数据,数据传输位宽为32位,发送的数据内容可以通trn_td中看出,其中trn_lnk_up_n代表整个事务链路的配置完成,trn_tsof_n为代表有效数据帧的开始,trn_teof_n代表每次数据帧的结束。

4 实验结果

图9所示为PC端与信号采集板卡间数据传输界面,由图中可见,数据上传速率为823.1 MB/s,下发速率为819.5 MB/s。因此,整体系统达到了数据传输速率不低于800 MB/s。图10所示为4路AD采集界面,图中是对4种不同模拟噪声的采样结果,采样值可以通过左侧的窗口查看,采样频率为100 MHz,实现了4路同时采集。

图10 4路AD采集界面

5 结 语

对所设计的基于CPCIe的高速多通道信号采集板卡,在规定条件范围内,进行了各项指标的检测,结果整个板卡总功耗不大于20 W,单板同时具备4路AD信号输入和4路DA信号输出,最高采样频率100 MHz,传输速率不低于800 MB/s,达到了设计要求。目前已成功进入试用阶段。

[1] 王 丰. PCI-E接口技术研究及其应用[D]. 哈尔滨:哈尔滨工业大学, 2009.

[2] 安 震,张会新.基于PCI总线与FPGA多通道信号采集传输系统的设计[J].科学技术与工程.2013,13(3):625-629.

[3] 邬 琦,杨江涛,马喜宏.基于FPGA的高速信号采集电路的设计与实现[J].实验室研究与探索,2015,34(4):124-128.

[4] 张 喆, 刘数奇. 基于FMC的高速多通道AD采样板卡设计[J]. 数字技术与应用, 2014(6):167-167.

[5] Bontu C, Wu K T, Mcnicol J,etal. Efficient data transmission and training of data processing functions: US, US 7522841 B2[P]. 2009.

[6] 贺良飞.高速数字信号完整性设计[J].安徽电子信息职业技术学院学报,2014,13(5):1-3

[7] 王晓彬,马 戎,李乐尧,等.基于FPGA的高速信号采集板卡的设计[J].测控技术,2011,30(6):25-28.

[8] 信 侃.基于Xilinx FPGA的PCIe总线接口设计与实现[J].无线电通信技术,2014,40(4):94-96.

[9] 赵宇玲.基于FPGA的信号采集与处理系统设计与实现[D].南京:南京理工大学,2008

[10] 吕书勇.一种超高速数据采集与分析系统设计[J],煤炭技术,2011,30(6):76-78.

[11] 苏海冰, 张刚, 郭帅. 高速数字电路的信号完整性与 电磁兼容性设计[J]. 单片机与嵌入式系统应用, 2010(5):14-17.

[12] Zheng Yongqiu,Ren Yongfeng,Liu Xin,etal.Multi-channel & high-precision data acquisition device for aerospace[J].Journal of Measurement Science and Instrumentation,2013,4(2):184-189

[13] 关凯锋.PCIe事务层及数据链路层的实现与验证[D]. 西安:西安电子科技大学,2013.

[14] 方宝林. PCI-E总线高速数据采集卡的研制[D]. 北京:北京交通大学, 2014.

[15] 侯杭呈, 王忆文, 李辉. 一种基于PCI Express总线的DMA高速传输系统[J]. 微电子学, 2013, 43(3):383-386.

[16] 张 亮. PCI Express协议的实现与验证[D]. 西安:西安电子科技大学, 2012.

Heavy Shearer Condition Monitoring Data Acquisition Board Design Based on CPCIe

ZHANGHuihui,MENGLingjun,HANZhaohui

(National Key Laboratory for Electronic Measurement and Technology,Key Laboratory of Instrumentation Science & Dynamic Measurement of Ministry of Education,North University of China, Taiyuan 030051, Shanxi, China)

For requirements for signal online acquisition of heavy shearer, this paper presents a design scheme of high speed multi-channel signal acquisition board based on CPCIe architecture. The scheme uses FPGA of virtex-6 series as the main controller, which is produced by Xilinx company. And this scheme uses high performance dual channel ADC, DAC conversion chip as the signal collecting and reading unit, combining with many pieces of large capacity DDR3 SDRAM as the cache unit. With the use PCIe hard solutions internal integrated in FPGA, the CPCIe bus interface unit has been constructed. In this paper, the hardware and software of the signal acquisition board are introduced in detail and a comprehensive simulation, testing and validation are carried out. Experiments verified that the board can process simultaneously 4 channel analog signal acquisition and transmission at 100 MHz sampling frequency, and the rate of the PCIe interface data upload is not less than 800 MB/s. This board is easy upgraded and flexible, and can be widely used.

CPCIe bus; shearer; multi-channel; signal acquisition

2016-08-10

国家高新技术研究发展(863)计划资助项目(2015AA042601)

张慧慧(1990-),女,山西太原人,硕士生,主要研究方向为FPGA逻辑、电路设计。

Tel.:18734136441;E-mail:2234887049@qq.com

孟令军(1969-),男,山东青岛人,副教授,硕士生导师,主要从事集成测量系统及仪器、微纳仪器及测试技术方向的研究。

Tel.:18734855988;E-mail:467978439@qq.com

TP 274.2

A

1006-7167(2017)03-0120-05