4路多相信号半带抽取滤波器优化实现结构

张 娜,贾和平

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081; 2.原兰州军区通信网络技术管理中心,甘肃 兰州 730000)

4路多相信号半带抽取滤波器优化实现结构

张 娜1,贾和平2

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081; 2.原兰州军区通信网络技术管理中心,甘肃 兰州 730000)

高速FIR滤波器的4路多相实现结构工作的采样速率是单路串行实现结构的4倍,针对4路多相信号半带抽取滤波器直接实现结构计算复杂度大这一问题,提出了一种4路多相信号半带抽取滤波器的优化实现结构。推导得到4路多相信号FIR滤波器优化实现结构;在此基础上,分析不同输出组合的计算复杂度,给出4路多相信号半带抽取滤波器的优化实现结构。对于4路多相信号半带抽取滤波器,仿真结果表明,提出的优化实现结构的计算复杂度约为直接实现结构的75%,验证了其优越性。

FIR滤波器;多相分解;半带滤波器;抽取

0 引言

相对于模拟信号处理,数字信号处理具有灵活性、高精度和高稳定性、便于大规模集成、对数字信号可以存储和运算且系统可以获得高性能指标等优点,已广泛应用于语音、图像、控制、航空和航天等众多领域[1]。随着信息技术的飞速发展,对高性能的数字信号处理要求越来越高[2]。在数字信号处理系统中,有限脉冲响应(Finite Impulse Response,FIR)滤波器由于其优良的线性相位特性和无条件稳定的特点,在多个领域都得到了广泛的应用[3]。在雷达、通信和遥测遥感等信号处理领域,通常要求FIR滤波器能工作在较高的频率上[4]。近些年来,高速FIR滤波器的高速并行实现结构得到了广泛的关注。文献[5-6]给出了数字下变频的并行FIR滤波器实现结构;针对变采样率抽取,文献[7]论述了一种多相滤波实现方法;文献[8]介绍了一种节约硬件资源的FIR滤波器多相并行实现结构;在对称系数情况下,文献[9]提出了一种FIR滤波器多相并行实现方法;为了进一步节约硬件资源,文献[10]论述了一种基于迭代短卷积算法的低复杂度并行FIR滤波器结构。

半带滤波器是一种基于抽取和内插原理的滤波器,是一种特殊的低通线性相位有限冲激响应数字滤波器,即抽取因子为2的抽取滤波器。这种滤波器由于通带和阻带相对于1/2 Nyquist频率对称,因而有近一半的滤波器系数为零[11]。由于系数为零的部分在运算的过程中不需要消耗运算量,所以运算量减少了一半,使实际滤波过程中的运算量大幅度减少,因此计算的效率高,实时性比较强,有利于滤波运算的实时实现,在多速率信号处理中有着特别重要的地位,并且得到了广泛的应用[12]。文献[13-14]的主要研究聚焦于滤波器设计,文献[12,15]的主要研究聚焦于简化实现结构,而鲜有文章涉及多相信号的半带抽取滤波器的优化实现。

本文聚焦于4路多相信号半带抽取滤波器的优化实现结构,在4路多相信号FIR滤波器优化实现结构的基础上,分析不同输出组合的计算复杂度,给出了4路多相信号半带抽取滤波器的优化实现结构,其计算复杂度约为直接实现结构的75%。

1 半带低通滤波器

半带低通滤波器是一种特殊的FIR滤波器,其幅频特性如图1所示。其中,ωP为滤波器的通带上限数字频率,ωS为滤波器的阻带下限数字频率,δP为滤波器的通带误差容限,δS为滤波器的阻带误差容限[16]。

图1 半带低通滤波器幅频特性

如图1所示,对于半带低通滤波器有如下关系

(1)

2 半带低通抽取滤波器优化实现结构

首先介绍4路多相信号FIR滤波器优化实现结构;并在此基础上,分析不同输出组合的计算复杂度,给出4路多相信号的半带抽取滤波器的优化实现结构。

2.1 4路多相信号FIR滤波器优化实现结构

FIR滤波器的频域表达式为[4]:

(2)

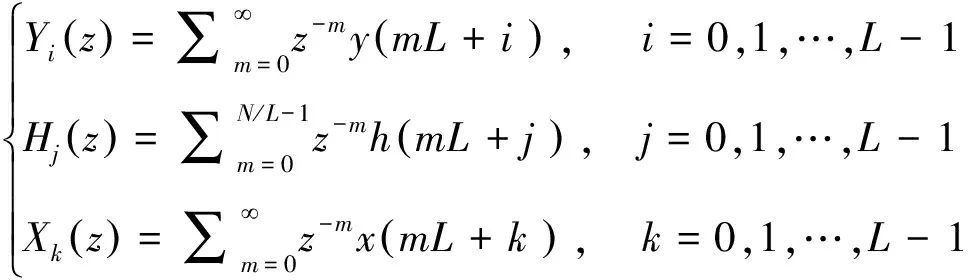

式中,L为滤波器并行的路数;Yi(z)、Hj(z)和Xk(z)分别为:

(3)

当并行路数为4时,式(2)可以表示为:

(4)

式(4)可以简化表示为[8]:

(5)

(6)

将式(6)代入式(5)并化简可得

Y=X0H0+z-4((X1+X3)(H1+H3)-X1H1-X3H3+X2H2)+z-1((X0+X1)(H0+H1)-X0H0-X1H1+z-4((X2+X3)(H2+H3)-X2H2-X3H3))+z-2((X0+X2)(H0+H2)-X0H0-X2H2+X1H1+z-4X3H3)+z-3((X0+X1+X2+X3)(H0+H1+H2+H3)+X0H0+X1H1+X2H2+X3H3- (X0+X1)(H0+H1)-(X0+X2)(H0+H2)- (X1+X3)(H1+H3)-(X2+X3)(H2+H3))。

(7)

从式(7)中可以看出4路多相信号FIR滤波器的优化实现结构,如图2所示。

从式(7)和图2中可以看出,经过推导得到的4路多相信号FIR滤波器优化实现结构需要9个子滤波器,其计算复杂度是16个子滤波器直接实现结构的56.25%。

图2 4路多相信号FIR滤波器优化实现结构

2.2 4路多相信号的半带抽取滤波器的优化实现

对4路多相信号进行降2抽取,下面分析图2所示4路多相信号FIR滤波器优化实现结构选择Y0和Y2输出及选择Y1和Y3输出的计算复杂度。

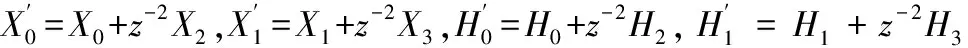

式(4)和式(7)中各子滤波器所需的计算复杂度如表1所示。

表1 各子滤波器计算复杂度统计

由于半带滤波器有限脉冲响应取值的特点,下面比较采用式(4)所示的4路多相信号FIR滤波器直接实现结构进行半带滤波和抽取所需的计算复杂度以及采用式(7)和图2所示的4路多相信号FIR滤波器优化实现结构进行半带滤波和抽取所需的计算复杂度,如表2所示。

表2 计算复杂度比较

从表2中可以看出,对于优化实现结构,相比于选择Y1和Y3输出,选择Y0和Y2输出所需的计算复杂度约减小一半;对于直接实现结构,选择Y1和Y3输出与选择Y0和Y2输出的计算复杂度是一样的;选择Y0和Y2输出,优化实现结构的计算复杂度约为直接实现结构的75%;由此,选择优化实现结构进行半带滤波和抽取,并选择Y0和Y2作为抽取输出,4路多相信号半带抽取滤波器优化实现结构如图3所示。

图3 4路多相信号半带抽取滤波器优化实现结构

对于4路多相信号半带抽取滤波器,需要确定的主要参数包括输入的数据位宽、滤波器阶数、滤波器系数和位宽,这些参数主要由系统指标(如适应的动态范围和处理精度等)和可利用的逻辑资源综合决定。如图3所示,4路多相信号半带抽取滤波器优化实现结构为4路多相信号半带抽取滤波器的实现提供了一种计算复杂度较小的实现结构,适用于任意输入数据位宽、任意滤波器阶数、任意滤波器系数和位宽的半带抽取滤波器;滤波器的输入为4路多相数字信号,输出为经半带滤波抽取后的2路多相数字信号;输入的4路多相数字信号是系统经高速数字信号获取、多相化并行处理和其他处理等操作后的结果,是某高速数字信号的4路多相并行表示。

3 算法仿真分析

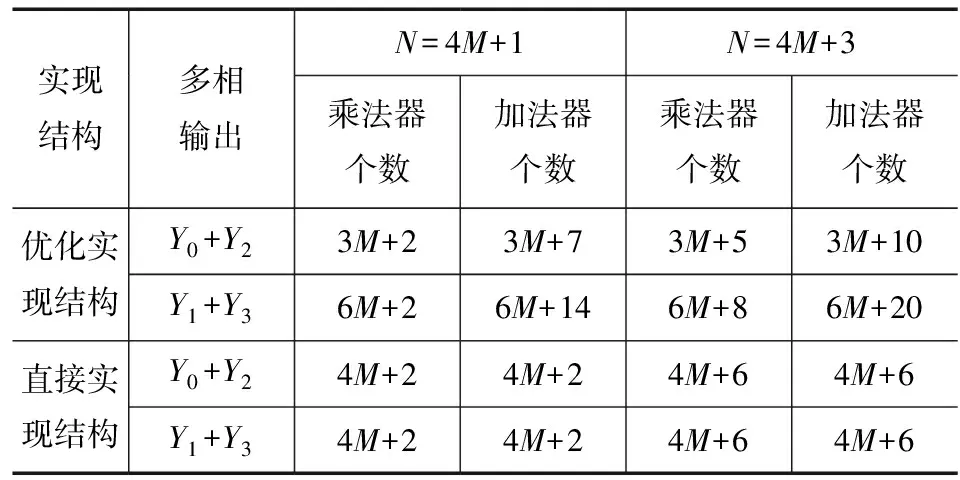

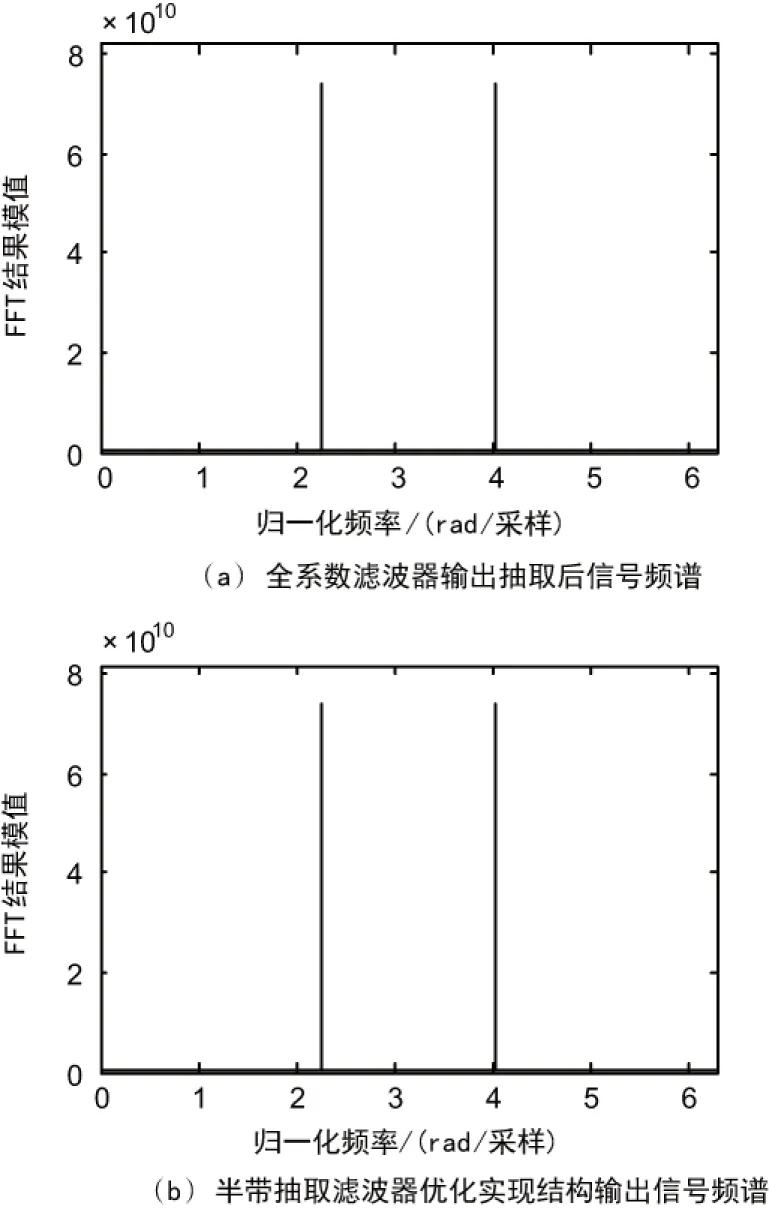

数值仿真分析结构框图如图4所示,其中全系数滤波器和半带抽取滤波器优化实现结构都采用定点数的形式进行实现。

图4 数值仿真分析结构

不失一般性,滤波器数据输入定点数位数为9 bit,滤波器系数为12 bit。半带滤波器幅频响应、输入信号频谱和全系数滤波器输出信号频谱如图5所示。

图5 输入输出信号频谱

全系数滤波器输出抽取后信号和半带抽取滤波器优化实现结构输出信号时域误差为0;全系数滤波器输出抽取后信号频谱和半带抽取滤波器优化实现结构输出信号频谱如图6所示。

图6 滤波器输出结果对比

可以看出,半带抽取滤波器优化实现结构能够同时正确地对输入信号进行半带滤波和抽取,且其计算复杂度约为直接实现结构的75%。

4 结束语

半带滤波器的计算效率高,实时性比较强,有利于滤波运算的实时实现,在多速率信号处理中有着特别重要的地位,得到了广泛的应用。本文对FIR滤波器的4路多相并行实现结构进行了推导,得到FIR滤波器的4路多相优化实现结构;在4路多相信号FIR滤波器优化实现结构基础上,分析不同输出组合的计算复杂度,给出4路多相信号半带抽取滤波器的优化实现结构,其计算复杂度约为直接实现结构的75%。本文结论对系统的工程实现有指导意义。

[1] 张建伟,展雪梅.FIR数字滤波器的设计与实现[J].无线电工程,2010,40(6):54-56.

[2] 张维良,张 彧,杨再初,等.高速并行FIR滤波器的FPGA实现[J].系统工程与电子技术,2009,31(8):1 819-1 822.

[3] 张红梅,韩万刚.FIR滤波器时延分析及其在信号融合中的应用[J].武汉大学学报(工学版),2016,49(2):303-308.

[4] 宋广怡.FIR滤波器的8路多相27子滤波器实现结构[J].无线电工程,2015,45(2):22-25.

[5] 王 璐,李 明.基于并行FIR滤波器结构的数字下变频[J].火控雷达技术,2010,39(3):36-40.

[6] 顾明超,李 倩.宽带数字下变频器的FPGA实现[J].无线电通信技术,2014,40(5):69-72.

[7] 苟晓刚,周红彬.一种新的多相滤波结构在FPGA中的实现[J].无线电通信技术,2004,30(4):53-54.

[8] PARKER D A,PARHI K K.Area-efficient Parallel FIR Digital Filter Implementations[C]∥IEEE Proceedings of International Conference on Application Specific Systems,Architectures and Processors,1996:93-111.

[9] TSAO Y,CHOI K.Area-efficient Parallel FIR Digital Filter Structures for Symmetric Convolutions Based on Fast FIR Algorithm[J].IEEE Transactions on Very Large Scale Integration Systems,2012,20(2):366-371.

[10] 田晶晶,李广军,李 强.一种基于迭代短卷积算法的低复杂度并行FIR滤波器结构[J].电子与信息学报,2014,36(5):1 151-1 157.

[11] 韩治国,王红梅,许 辉.基于窗函数和特征滤波器的半带滤波器设计[J].计算机仿真,2013,30(8):181-185.

[12] 任堰牛,青小渠.FIR半带滤波器的简化结构及其仿真研究[J].兵工自动化,2013,32(3):53-56.

[13] 苏 飞,孙 杰.全相位半带滤波器设计与实现[J].信号处理,2015,31(2):194-200.

[14] 郄志鹏,翟海涛,付永明,等.半带脉冲成形滤波器设计及性能分析[J].国防科技大学学报,2015,37(4):106-110.

[15] 沈 志,王宏远.基于半带滤波器的插值结构FPGA优化实现[J].微电子学与计算机,2011,28(2):15-20.

[16] 韩计海,吴炳洋.基于MATLAB的高性能半带滤波器设计[J].信息化研究,2009,35(6):24-28.

张 娜 女,(1984—),硕士,工程师。主要研究方向:卫星通信。

贾和平 男,(1968—),高级工程师。主要研究方向:通信网络。

Optimized Implementation Structure of 4-Channel Polyphase Halfband Decimation Filter

ZHANG Na1,JIA He-ping2

(1.The54thResearchInstituteofCETC,ShijiazhuangHebei050081,China; 2.CommunicationNetworkControlCenteroftheFormerLanzhouMilitaryArea,LanzhouGansu730000,China)

Compared with the serial FIR filter,the sampling frequency of the implementation structure of the 4-channel polyphase decomposition of high-speed FIR filter is increased by a factor of 4.Aiming at the problem that the implementation structure of the direct 4-channel polyphase halfband decimation filter has enormous computational complexity,an optimized implementation structure of 4-channel polyphase halfband decimation filter is proposed.Firstly,the optimized implementation structure of the 4-channel polyphase FIR filter obtained.And then based on this,the optimized implementation structure of 4-channel polyphase halfband decimation filter is derived.Finally,the computer simulation shows the superiority of the proposed implementation structure for the 4-channel polyphase decomposition filter,which is verified by the fact that the computational complexity of the proposed implementation structure is 75% of the structure before optimization.

FIR filter;polyphase decomposition;halfband filter;decimation

10.3969/j.issn.1003-3106.2017.05.26

张 娜,贾和平.4路多相信号半带抽取滤波器优化实现结构[J].无线电工程,2017,47(5):106-110.[ZHANG Na,JIA Heping.Optimized Implementation Structure of 4-Channel Polyphase Halfband Decimation Filter[J].Radio Engineering,2017,47(5):106-110.]

2017-02-16

中国电子科技集团公司航天信息应用技术重点实验室开放基金资助项目(EX166290012)。

TN919

A

1003-3106(2017)05-0106-05