基于射频收发应用的低噪声频率综合器设计

曲 明,翟 越,王 楠

(中国电子科技集团公司第五十四研究所,河北 石家庄050081)

基于射频收发应用的低噪声频率综合器设计

曲 明,翟 越,王 楠

(中国电子科技集团公司第五十四研究所,河北 石家庄050081)

随着无线通信技术的高速发展,载波频段的不断升高,对收发芯片中频率综合器的噪声性能提出了较高的要求。针对通信收发系统中频率综合器的设计,提出了一些低噪声的设计技术,电源电压1.2 V,采用SMIC 0.13 μm CMOS 工艺。主要对频率综合器主要组成模块鉴相器、电荷泵、LC型压控振荡器以及ΔΣ调制器的噪声性能进行了分析和优化,在此基础上提出了优化相位噪声的方案,并展示了关键模块的仿真结果和整体电路相位噪声的测试情况。结果显示其噪声性能达到了国内较高水平。

频率综合器;低相位噪声;电荷泵;ΔΣ调制器;LC压控振荡器

0 引言

随着射频集成电路制造工艺的快速发展,基于CMOS射频工艺的频率综合器可以很容易地实现数GHz的频率时钟信号输出,使利用CMOS射频工艺实现前端接收机和发射机成为可能。但随着通信系统中频带资源的变大,对信号通信质量要求的提高,尤其是在射频通信、无线广播的接收设备中,为了更好地改善信噪比,对接收芯片中本振信号的质量提出了较高的要求。因此,研究满足通信行业发展需求的低相位噪声频率综合器已成为当下的研究热点[1-2]。

1 延迟可调鉴相器(PFD)的设计

目前,在大多数锁相环的设计中通常采用的都是无死区的鉴频鉴相器,因为死区是引起杂散、相噪的主要因素之一,死区使后级压控振荡器的相对输入必须将随机相位差累积到额定值时,环路才得到有效的反馈。压控振荡器的输出在这些过零点时,就会使输出时钟产生抖动[3]。

消除“死区”的方法为:在复位路径上插入延时单元,从而使PFD产生的UP和DOWN信号在高电平末尾会同时为高,使电荷泵的开关不会出现因为信号时间过短而导致电荷泵无法输出或输入电流,从而消除该电路的死区效应。

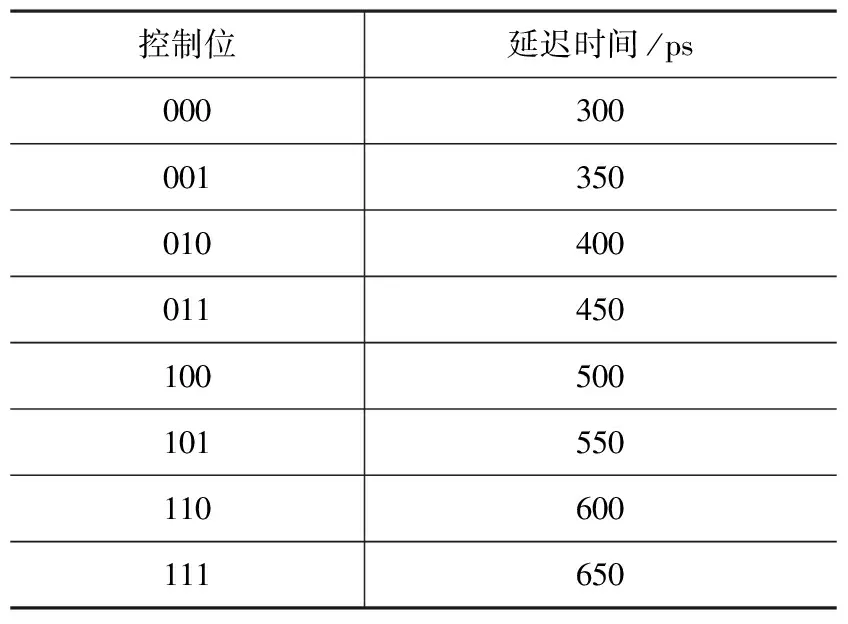

通过以上分析可知,死区是可以消除的,但PFD中复位延迟时间过长,会将后级电荷泵中(CP)的电流失配效应累积放大,即使在电荷泵完全匹配的情况下,也存在参考时钟的馈通,在锁相环的输出存在着参考频率的毛刺。而复位时间过短,则又不能做到无死区的鉴相。因此,在延迟单元设置上,本文在PFD的复位延迟设计了3 bit延迟可调,从而能够灵活地控制延迟时间,如表1所示,具体电路如图1所示。

表1 延迟配置

控制位延迟时间/ps000300001350010400011450100500101550110600111650

图1 3 bit延迟可调PFD

2 自校准差分电荷泵(CP)的设计

通常电荷泵在工作时不可避免地有电荷泄漏、充放电流适配等非理想性因素存在,使得电压存在抖动,造成输出频率的相位偏差,引起VCO的频率抖动而产生噪声[5-6]。所以,设计一个高性能的电荷泵电路对锁相环路来说是非常重要的。

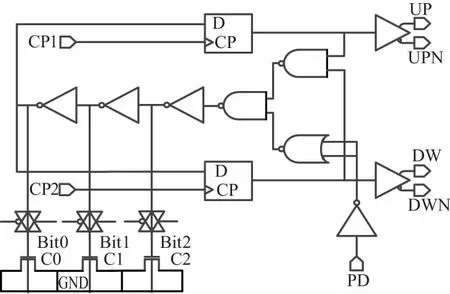

为了消除上述的电荷泄漏、充放电流适配等非理想性因素,可采用自校准电荷泵电路,其原理和电路结构如图2所示。

由于CMOS实现的开关电流源的内阻并非无穷大,电荷泵在输出电压范围较大时泵出或者泵入的电流不能完全匹配,这个电流误差将引入杂散。自校准电路的引入可以克服这个问题,引入复制电荷泵电流支路的参考支路,把参考支路和电荷泵电流支路的输出节点电压作为放大器的输入,放大器的输出直接调节2条支路的电流偏置。这种电路可以保证电荷泵的泵出或者泵入电流的匹配特性不随输出电压的改变而改变,完全由器件工艺尺寸误差决定输出电流的适配。

图2 自校准电荷泵原理图

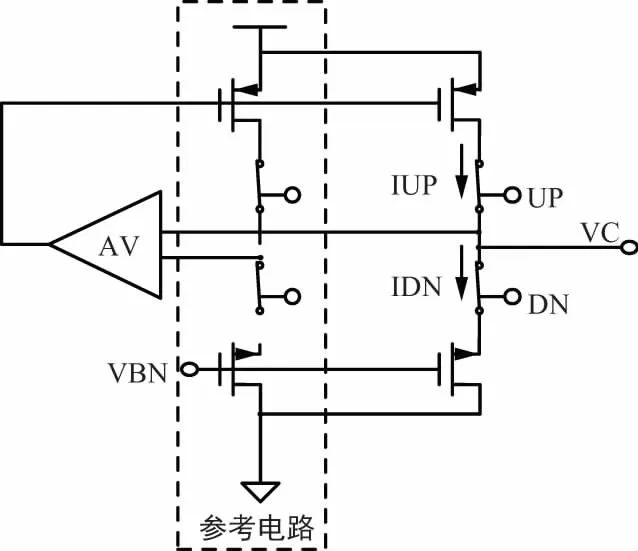

为了确保环路的稳定性,又增加跨导运算放大器,如图3所示。在参考支路以外又增添了偏置支路,把放大器的输出连接到偏置支路上,降低放大器这一级的增益,使反馈回路的开环等效为一级放大,则反馈回路处于无条件稳定状态,无需进行频率补偿。改进电路的优点是在保证输出范围大、电流匹配性好的同时,极大地增强了电路的稳定性。

图3 本文设计采用的自校准差分电荷泵

另外,由于电流源MP3和MN3的漏端有限寄生电容不一样,会引起电荷共享的问题,即MP3和MN3的漏端在开关开启和关断时,电荷的变化量不一样,这将导致净电荷量流入或流出环路,最终导致环路滤波器的电压出现纹波,恶化锁相环的相噪[8]。为了解决这一问题,采用了差分电荷泵,如图3所示,将差分两端用一个单位增益放大器连接起来,使得两边的共模电平保持相等,两侧电压保持恒定,也就不会产生电荷共享的问题。

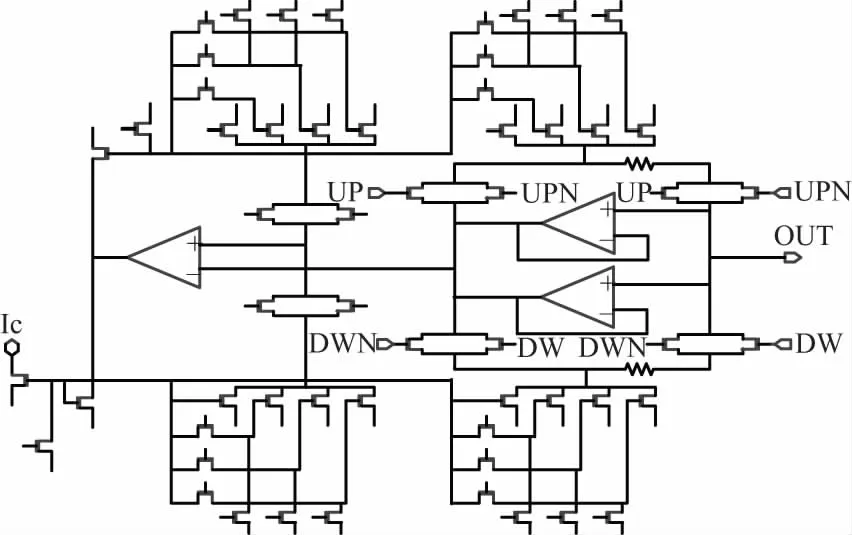

本设计采用的具体电荷泵电路如图4所示,开关管的设计采用互补式对管,降低时钟馈通效应;单位增益运放采用了PMOS尾电流源和NMOS尾电流源两级运放,以保持运放两侧电压范围的一致性,同时还增加了一些电流控制位。

图4 电荷泵电路

3 无源滤波器的分析设计

电荷泵输出信号包含有直流成分和高阶谐波成分,其中高频成分则是不需要的信号,这些高频成分通常由环路低通滤波器滤除。

环路滤波器有2种实现方式:无源和有源,两者具有相同的零极点位置,只是有源的在输出增加了增益[9]。一般来讲,无源滤波器的噪声比有源滤波器的噪声小,所以本设计采用无源滤波器,无源滤波器的常用结构如图5所示。

图5 环路滤波器

图5 (a)是二阶环路滤波器,它有1个零点和2个极点。其传输函数为:

(1)

图5 (b)是三阶环路滤波器,其传输函数为:

(2)

通过传输函数式(1)和式(2)的对比,较二阶滤波器来说,三阶滤波器又增加了一个高频极点,因此环路滤波器对高频噪声有较好的抑制作用。

本文设计采用三阶环路滤波器,在实际设计中,C1远大于C2和C3,R1远大于R2。

无源滤波器的噪声主要来源于电阻的热噪声,一般设计中,电阻R值越小越好。因为R越小,输出噪声系数越小。但是R越小,则系统的相位裕度越小,系统越不稳定,而且使得系统跟踪的速度变慢,系统带宽变小,所以本文电路设计在满足带宽前提下尽量降低电阻R1和R2的值。

4 低噪声LC型VCO设计

基于射频收发的本振输出频率一般在几GHz左右,因此VCO的振荡频率一般也在几GHz,若有正交输出的要求,需要引入高速二分频电路,则振荡频率还会有一个成倍的变化。

压控振荡器主要分为环形振荡器和LC型振荡器两大类,环形振荡器一般为多个放大器级联反馈而成,但是由于其可实现频段不高,而且相位噪声比LC压控振荡器差,因此,在射频收发本振的设计上,主要采用LC型压控振荡器。该结构主要由高Q值的电感、可变电容阵列和MOS交叉负阻管组成。常用的结构包括NMOS交叉耦合管、PMOS交叉耦合管和NMOS/PMOS互补交叉耦合管3种[10-12]。

本文采用NMOS/PMOS交叉耦合负阻振荡电路,如图6所示,这样对耦合晶体管跨导的要求较低,约为LC环路寄生电阻的1.25~1.5倍即可。另外,采用该结构,可以保证电路的对称性,能够输出质量较高的差分信号。

图6 本电路采用的交叉耦合LC型VCO

LC型振荡器的噪声水平,主要和其中电感的Q值有很大关系,因此,在设计仿真时,通过降低电感匝数,来提高电感的Q值。此外,还采取了以下措施来降低相噪[14-17]。

措施一,通过在差分对管共源点加一个与尾电流源管并联的大电容,来滤除二次及二次以上谐波附近的噪声,这样做也削弱了尾电流源管的沟道长度调制效应,使振荡器输出波形更加对称。

措施二,降低振荡器的调谐增益。由于输出相位和频率的变化是控制线上的噪声所导致的结果,对于给定的噪声幅度:

wout=w0+KVCOVcont。

(3)

由式(3)可知,输出频率中的噪声正比于Kvco,所以要使Vcont上的噪声效应减到最小,VCO的增益必须最小,这就需增加调谐曲线的数量。

措施三,在VCO版图的设计中,LC的环路走线尽量采用高层宽金属,以减小寄生电阻对相位噪声的贡献。

本文设计的VCO调谐范围从2~4 GHz,采用3个VCO,每个VCO采用5 bit控制电容阵列,共32根调谐曲线,这样可以将Kvco控制在20 MHz/V左右。

5 小数分频ΔΣ调制器的分析设计

频率综合器必然要用到小数分频技术,其中减少分数杂散的方法,目前较多采用的是ΔΣ技术,该技术能够有效地将量化噪声随机化,低频率段的量化噪声推移到较高的频率段,以提高信号带内的信噪比[4]。

本文ΔΣ调制器采用的是基于MASH 1-1-1结构的三阶调制器,如图7所示。

图7 典型MASH1-1-1结构

该结构简单,主要是由累加器和延迟单元组成,由于经过了三级噪声整形,输出电平从-3~4,因此对相位噪声的抑制效果好,非线性噪声电平一般可以达到<-45 dB@300 kHz[7]。

高阶全数字调制器的寄存器是有限的,输出序列还是无法避免周期性的存在,这将会导致杂散噪声的产生,特别在输入x(n)为一些周期性的小数时,输出序列的周期性会更强。为了消除输出序列的周期性,将三阶调制器中的第1级累加器的进位输入端置零,同时分别在第2级和第3级累加器的进位输入端口输入一个7位线性反馈移位寄存器(LFSR)产生的伪随机序列d(n)。如图8所示,这种伪随机序列近似为高斯白噪声,没有任何能量,只会破坏输出序列的周期性,并不会对调制器的调制功能产生影响。

图8 带伪随机产生器Mash结构

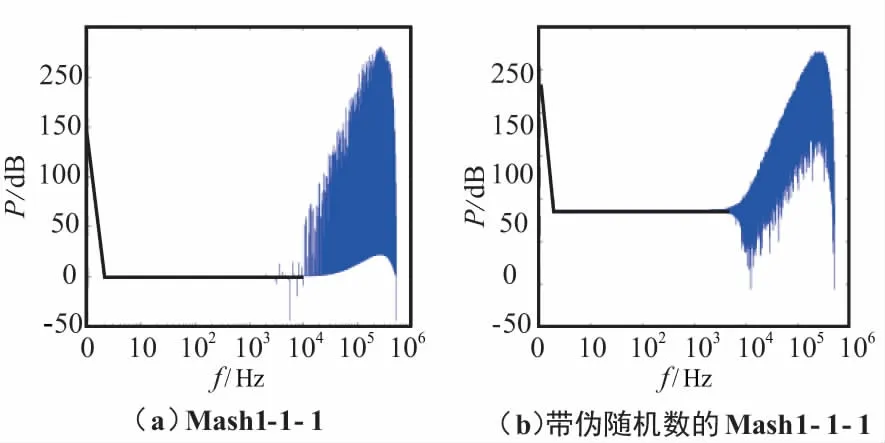

本文基于matlab对典型Mash1-1-1和带伪随机产生器Mash结构进行了建模仿真,仿真结果如图9所示。

图9 Matlab建模仿真结果

图9(a)是典型Mash 1-1-1的仿真结果,图9(b)是带伪随机产生器的仿真结果,可以明显看到,虽然二者都实现了将低频的小数杂散向高频搬移,但左图中在104频率处杂散的能量是在70 dB左右,而右图中在相同位置的能量是在10 dB左右,由于伪随机数的加入削弱了杂散的能量,并且使杂散的能量更为集中。

6 频率综合器整体环路带宽的分析设计

前面在降低频率综合器各个模块自身噪声方面进行了分析研究,然而整体频率综合器输出频率的相位噪声性能不仅同各模块的设计相关,而且严重依赖整个环路带宽的选择[13]。

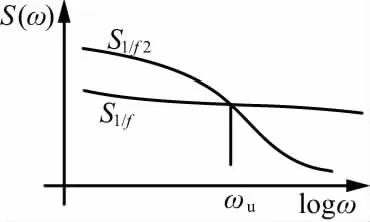

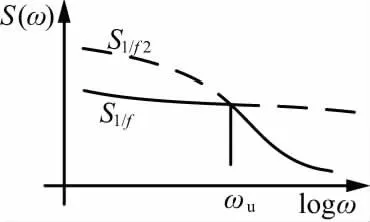

各模块噪声可被划分为2类:① 电荷泵和分频器的固有相位噪声(具有1/f频域特性);② VCO和滤波电阻等效的相位噪声(具有1/f2频域特性)。相应环路传输函数HL和HH分别为低通和高通函数:

(4)

(5)

2类噪声源对输出总噪声的贡献大小取决于各自到输出传输函数式(4)和式(5)的带宽。

图10为2类噪声源的功率密度谱,图11为引入了环路高通和低通效应修正后的密度谱,可以看到,当带宽正好在2根谱线交点ωu频率处时,2根谱线交叉高出部分将能够被抑制掉,如图中虚线部分,这样能进一步减弱各个模块噪声源所引入的相位噪声。

图10 2类噪声源的 功率密度谱

图11 环路调整后噪声 功率密度谱

本文设计频率综合器,在VCO振荡在2 GHz时,分频输出400 MHz,输入鉴相频率为3 MHz,带宽设置在100 kHz,对输出的相位噪声进行了测试,结果如图12所示。

图12 相位噪声测试结果图

可以看到相位噪声在1 kHz处达到了-97 dB,在10 kHz处达到了-102 dB,在100 kHz处达到了-101 dB,在1 MHz处达到了-115 dB,该指标达到了国内在该频率段相噪的较好水平。

7 结束语

本文在对射频收发器中的频率综合器的低噪声设计中,对鉴相器、电荷泵、环路滤波器、LC振荡器和小数分频ΔΣ调制器进行了优化,并对环路带宽进行了合理设计,仿真及测试结果表明,各模块的噪声性能得到了改善,整体频率综合器输出频率的噪声性能得到了较大提高,能够适应当前射频收发器的应用要求。

[1] Phillip E A.CMOS模拟集成电路设计(第2版)[M].北京:电子工业出版社,2011.

[2] Sansen W M C.模拟集成电路设计精粹[M].北京:清华大学出版社,2008.

[3] 拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2008.

[4] Pamarti S,Jansson L,Galton I.A Wideband 2.4 GHz Delta-Sigma Fraetional-N PLL with l-Mb/s In-LooP Modulation[J].IEEE Journal of Solid-State Circuits,2004,39(1):49-62.

[5] Temporit E,Albasini G,Bietti I,et al.A 700-kHz Bandwidth ΔΣ Fractional Synthesizer with Spurs Compensation and Linearization Techniq-ues for WCDMA Applications [J].IEEE Journal of Solid-State Circuits,2004,39(9):1446-1454.

[6] Swaminathan A,Wang K J,Galton I.A Wide-Bandwidth 2.4 GHz ISM Band Fractional-N PLL With Adaptive Phase Noise Cancellation [J].IEEE Journal of Solid-State Circuits,2007,42 (12):2639-2650.

[7] Meninger S E,Perrott M H.A 1-MHz Bandwidth 3.6-GHz 0.18-um CMOS Fractional-Synthesizer Utilizing a Hybrid PFD/DAC Structure for Reduced Broadband Phase Noise [J].IEEE Journal of Solid-State Circuits,2006,41(4):966-980.

[8] Hedayati H ,Khalil W ,Bakkaloglu B.A 1 MHz Bandwidth,6 GHz 0.18 um CMOS Type-I ΔΣ Fractional-N Synthesizer for WiMAX Application [J].IEEE Journal of Solid-State Circuits,2009,44(12):3244-3252.

[9] 何 捷.DVB-T 接收机中频率综合器的研究[D].上海:上海交通大学,2005.

[10]邓贤进,李家胤,张 健.锁相频率合成器相位噪声的精确估计与仿真[J].电路与系统学报,2006,11(5):128-131.

[11]张淑娥,王 丹.基于LTC1562的谐振器设计与实现[J].无线电工程,2011,41(11):40-42,60.

[12]刘 欣,井科学,欧阳萍.基于YIG振荡器的宽带频率综合器设计[J].无线电工程,2012,42(2):58-61.

[13]彭志华,周存麒.C波段低相噪频率合成器设计[J].无线电工程,2012,42(3):44-46.

[14]吴俊晨,任文成,徐志平.利用PLL减小时钟前沿抖动的研究[J].无线电工程,2013,43(2):52-54.

[15]杨 强,李栋贤.毫米波卫星通信频段功率合成器的研究[J].无线电工程,2013,43(5):59-61.

[16]胡丽格.一种S波段宽带小步进频率合成器的设计与实现[J].无线电工程,2015,45(5):70-72.

[17]王战永.基于DDS+PLL一种快速跳频频率合成电路的设计与实现[J].移动通信,2014,38(24):57-61,66.

Design of Low Noise Frequency Synthesizer Based on RF Transceiver Applications

QU Ming,ZHAI Yue,WANG Nan

(The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China)

The rapid development of wireless communication technology and the higher and higher carrier frequency band put higher demands on the noise performance of the frequency synthesizer in the transceiver chip.For the design of frequency synthesizers in communication transceiver system,some low noise design techniques are proposed.The power supply voltage of the design is 1.2 V,and the process is CMOS 0.13 um.The paper analyzes and optimizes the noise performance of the main components of the frequency synthesizer,including the phase detector,charge pump,LC type oscillator and the ΔΣ modulator.Based on this,the paper proposes the scheme of phase noise optimization and presents the simulation results of key modules and phase noise test results of the whole circuits.The results show that the noise performance has reached the high domestic level.

synthesizer;low phase noise;charge pump;ΔΣ modulator;LC oscillator

10.3969/j.issn.1003-3114.2017.03.19

曲 明,翟 越,王 楠.基于射频收发应用的低噪声频率综合器设计[J].无线电通信技术,2017,43(3):76-80.

[QU Ming,ZHAI Yue,WANG Nan.Design of Low Noise Frequency Synthesizer Based on RF Transceiver Applications[J].Radio Communications Technology,2017,43(3):76-80.]

2016-11-23

国家部委基金资助项目

曲 明(1982—),男,工程师,主要研究方向:模拟集成电路设计。翟 越(1989—),男,助工,主要研究方向:模拟集成电路设计。

TN911.7

A

1003-3114(2017)03-76-5