CCSDS标准下低码率LDPC码的编码器设计

龚杨阳,安军社,朱 岩

(1.中国科学院国家空间科学中心 北京100190;2.中国科学院大学 北京100190)

CCSDS标准下低码率LDPC码的编码器设计

龚杨阳1,2,安军社1,朱 岩1

(1.中国科学院国家空间科学中心 北京100190;2.中国科学院大学 北京100190)

基于空间咨询委员会(CCSDS)推荐的深空通信标准,针对码长为4096,码率为1/2、2/3、4/5的LDPC码,提出了一种实现在FPGA的编码器设计方法。根据生成矩阵的块循环特性,使用移位累加寄存器来设计编码器,3个码率使用同一套触发器,从而极大的节省了硬件消耗资源。

LDPC码;原模图;CCSDS标准;深空通信;移位累加寄存器

低密度奇偶校验(LDPC)码是Gallager[1]博士在1961年提出的一种线性分组码,采用迭代译码算法译码。近年来的很多研究表明,LDPC码有着接近香农极限的优异性能,有着广阔的应用前景[2]。空间咨询委员会(CCSDS)也将其推荐为应用于深空通信的信道编码方式[3]。

香农指出,对于任何信道,只要采用随机性编、译码方式,编码长度接近无限大,在其信息传输速率不超过信道容量时,采用最佳的似然译码方案,必然存在一种编码方式的误码率可以任意小[4]。LDPC码之所以有如此好的性能,就在于其编码时引入交织器而实现了伪随机性。并且,由于迭代译码算法的译码复杂度不会因码长的增加,使得LDPC码在码长较长的情况下也可以有很强的纠错能力,用较少的资源消耗获得极高的吞吐量。

文中是基于CCSDS提出的131.1-O-2标准,实现了码长为4096,码率为1/2、2/3、4/5的LDPC码的编码器设计。该编码器硬件实现复杂度低,通过软件仿真译码性能,与标准中给出的译码性能曲线进行对比,保证编码器编码优越性能。

1 原模图LDPC码

LDPC码是一种有着稀疏校验矩阵的线性分组码,校验矩阵的稀疏性让LDPC码与其他线性分组码有着不同的译码算法,也保证了LDPC的译码低复杂度和较小的最小码距。LDPC码的设计也是从构造一个稀疏的校验矩阵开始的,然后再通过校验矩阵确定生成矩阵,从而进行后续的编码。所以构造LDPC码的本质就是构造一个稀疏的校验矩阵。构造稀疏矩阵的方法有很多种,基本方法就是在全零矩阵中将少数的0置换为1。一个好的LDPC码要满足无短环、无低码重码字和码间最小距离要尽可能大的条件[9],因此我们要使用合理的构造稀疏矩阵的方法。

2003年,J.Thorpe[5]提出了一种由原模图构造的LDPC码的方法,我们称之为原模图LDPC码。原模图是一种指节点数量相对较少的Tanner图。精心设计的原模图一般无四环,且构造出来的稀疏矩阵一般是准循环矩阵。

图1 原模图复制三次后置换

原模图由校验节点C、变量节点V和边E组成,边连接校验节点和变量节点[6]。图中1(a)是一个基本的原模图,它由4个变量节点,3个校验节点和8条边组成。此时原模图校验矩阵Hs可以表示为

当原模图复制三次之后(如图1(b)所示),此时得到的校验矩阵Hm表示为

其中I表示为3阶单位矩阵,0表示三阶全零矩阵。最后经过节点置换后,可以得到一个派生图(如图1(c)所示)。对同类节点边置换相当于在矩阵中的单位矩阵Hm进行列置换,因此在式(2)的基础上,派生图的校验矩阵[7]可以表示为

其中,E1,1…,E3,4为三阶置换矩阵。H就是最终原模图LDPC码的校验矩阵。

由式(3)我们可以知道,使用原模图设计LDPC码的难点就是设计置换矩阵。一般来说,置换矩阵都会被设计为一个循环矩阵,这样在存储校验矩阵的时候就只需要存储每一个置换矩阵的多项式,大大的降低了LDPC码的编码复杂度和译码复杂度。

2 CCSDS标准下的LDPC码

CCSDS发布的131.1-O-2标准中,给出了两种方法来设计LDPC码,其中对于应用于深空通信的LDPC码,CCSDS标准使用的就是原模图构造方法[8]。在该标准中,一共定义了9种适用于深空的LDPC码,码长为1024、4096、16384,码率r为1/2、2/3、4/5[9],这9种码的参数如表1所示。

表1 码率与码长

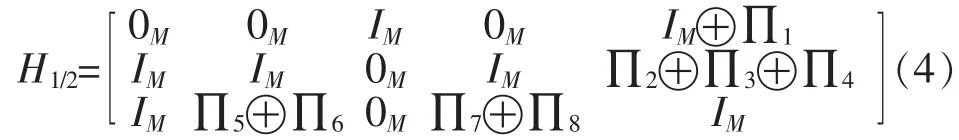

下面以1/2码率为例来说明。当码率r=1/2时,校验矩阵H1/2,由3×5个子循环矩阵构成:

在(4)式中,∏1到∏8是M×M维置换矩阵。0M为M×M维全零矩阵,IM为M×M维单位矩阵,M的取值与(n,k)相关。

CCSDS标准中定义置换矩阵∏k,k∈{1,2,…,8}中的第i行中的非零项的列序号为πk(i)表示,其中i∈1,…,M-1}。则πk(i)的计算公式见式(5):

最终我们可以求得原模图LDPC码的校验矩阵。接下来可以根据校验矩阵求得生成矩阵,最后使用生成矩阵完成编码。由于校验矩阵H是一个准循环矩阵,且生成矩阵G是校验矩阵H的逆矩阵,则生成矩阵G是分块循环矩阵[10]。

具体的编码方法如下[11]。

1)将校验矩阵H表示为H=[Q P],其中P是H的后3M列,Q是H的前MK列。

2)求解W=(P-1Q)T,其中矩阵运算在GF(2)中进行。

3)得到生成矩阵G=[IMKW],其中IMK是单位矩阵,W是稠密循环矩阵,大小可分块表示为:

3 编码电路FPGA实现

CCSDS标准将原模图构造的LDPC码推荐为深空通信的信道编码方式,在航天应用中要求硬件资源消耗少,算法稳定性高。针对以上要求,本文设计了如图2的LDPC编码器,对LDPC码进行分组,使用末位补零的方法提高编码稳定性,并将1/2、2/3、4/5 3种码率使用同一套触发器,极大的减少了资源消耗率。同时编码后进行扰码和添加帧头[12]的操作,极大的方便在实际空间通信系统中的使用。

图2 编码器设计

在CCSDS标准中我们选择了码长为4096位的信息帧来做完成LDPC的编码,首先我们需要将数据流进行分组,每一帧码长为4096位。针对1/2、2/ 3、4/5这三种码率,经过LDPC码编码器之后分别得到码长为8192位、6144位、5120位。编码器的输入位数和输出位数不一致,这样容易造成内存泄露。为了解决这个问题,我们采用累加器来设计编码器的核心结构。当信息码字为0时,不影响累加器的结果。因此我们在对码流进行分组时,采用末位补零的方法,针对种码率,将4096位信息位分别补零成为8192位、6144位、5120位,这样编码器的输入位数和输出位数一致,能更好的保障编码器的稳定性。

同时,由于LDPC码的生成矩阵比较大[13],如果直接存储,会使用很多资源。因此,根据生成矩阵的块循环特性,使用移位寄存器来设计编码器。生成矩阵是由一个单位矩阵和一个稠密循环矩阵构成。在编码器设计中,核心是完成信息序列和矩阵乘法即可。由上节中的格式可知,每行有8个子循环矩阵,我们只需要存储每个循环矩阵的第一行,通过移位的方法就可以完成乘法运算,这极大的减少了所需存储空间。将这8个循环移位寄存器并行设计,通过累加器来存储运算结果,既节省了资源,又提高了吞吐量。具体编码方法见图3所示。

图3 使用反馈移位寄存器的准循环编码器

文中的LDPC码编码器设计了1/2、2/3、4/5这3种码率,为了方便在航天应用的具体使用,我们将这3种码率的LDPC码使用一套触发器,以1/2码率的LDPC码编码所需的触发器长度来设计编码器,在FPGA实现时能更好的节省资源。根据上图的编码器结构,我们在Xilinx公司的xc4vsx55-12ff1148上实现了码长为4096,码率为1/2、3/4、4/5的LDPC编码。表4是所消耗的硬件资源,从表中我们看到所占用的硬件资源相对较少,说明该编码器实现复杂度低,硬件资源消耗少。

表2 编码器消耗的资源

4 仿真验证

为了验证编码硬件实现的正确性,我们把编码后的码字序列,使用BPSK调制,加上高斯白噪声,使用Matlab仿真译码,译码方法选用置信度传播算法[14],也称为和积算法,最大迭代次数设置为100。我们一般使用误比特率和误帧率来衡量信道编码性能[15]。图4和图5分别是码长为4096,码率为4/5的LDPC码的误比特率和误帧率的性能曲线。在 CCSDS标准中,也给出了相应的参考性能曲线,由此我们可知编码算法和硬件实现都是正确的。从下面两幅图中,我们也可以看出CCSDS标准下的LDPC码性能优越,在误码率为10-5时,所需信噪比仅为3.35 dB。

图4 误比特率性能曲线

图5 误帧率性能曲线

5 结 论

文中主要讨论了CCSDS标准中,使用原模图构造的低码率LDPC的编码方法和FPGA[16-17]的硬件实现。通过末位补零保障编码器的稳定性,3种码率使用一套触发器以更好的节省硬件资源,从实验结果可以看出,文中设计的编码器具有高效的编码增益性能,吞吐量高,纠错能力很强,消耗硬件资源少,非常适用于深空通信。

[1]R.G.Gallager.Low-Density Parity Check Codes [M].Cambridge,MA:MIT Press,1963.

[2]ETSI EN 302 307 V1.1.1,Digital Video BroadcastingSatelliteSecondGeneration[S].European,2004.

[3]CCSDS 131.1-0-2.Low density parity check codes for use in near-Earth and deep space applications [S].Washington DC,USA,2007.

[4]D.J.C.MacKay,R.M.Neal.Near Shannon limit performance of low density parity check codes[J].Electronics Letters,1997,33(6):455-457.

[5]J.Thorpe.Low-density parity-check LDPC codes constructed from protographs[C]//IPN Progress Report,2003.

[6]D.Divsalar,S.Dolinar,C.Jones.Low-rate LDPC codes with simple protograph structure[J].IEEE ISIT[C].Adelaide,Australia,2005(9):1622-1626.

[7]肖扬.Turbo与LDPC编解码及其应用[M].北京:人民邮电出版社,2011.

[8]Divsalar D,Dolinar S,Jones C.Construction of protographLDPC codeswith linearminimum distance[J].IEEE ISIT[C]//Seattle,USA,2006[T]:664-668.

[9]Abbasfar A,Divsalar D,Yao K.Accumulate Repeat Accumulate Codes[J].In Proceedings of the IEEE,2004(4):509-513.

[10]Divsalar D,Dolinar S,Thorpe J,et al.Construction LDPC codes from simple loop-free encoding modules[J].In Proceedings of the IEEE International Symposium on Information Theory,2006(6):664-668.

[11]李忠亮,夏国江.原模图LDPC码的准循环扩展和编码算法[J].空间科学学报,2011,31(3):406-411.

[12]CCSDS.1310-B-2.TM Synchronization and channel coding[S].Washington D.C.,USA,2011.

[13]Y.Kou,S Lin,M Fossorier.Low density parity check codes based on finite geometries:a rediscovery and new results[J].IEEE Transactions Information Theory,2001,47(10):2711-2736.

[14]J.H.Chen,M.P.C.Fossorier.Near optimum universal belief propagation based decoding of lowdensity Parity check codes[J].IEEE Trans.Commun,2002,50(3):406-414.

[15]袁东风,张海刚.LDPC码理论与应用[M].北京:人民邮电出版社,2008.

[16]郎宝华,单成刚,无刷直流电机的FPGA控制系统设计及仿真 [J].西安工业大学学报,2014(2):160-166.

[17]严明,李斌康,郭明安,等.高速光电探测器阵列实时信号处理系统 [J].现代应用物理,2014(4):316-321.

An encoder architecture for low-rate LDPC codes based CCSDS standard

GONG Yang-yang1,2,AN Jun-she1,ZHU Yan1

(1.National Space Science Center of the Chinese Academy of Science Department of Space Technology,Beijing 100190,China;2.University of Chinese Academy of Sciences,Beijing 100190,China)

An encoder architecture is proposed to implement 1/2,2/3,4/5 rates LDPC codes based on the Consultative Committee for Space Data Systems standards.According to block cycle characteristics of the generation matrix,we used a feedback shift register design this encoder for saving hardware cost.And we add zeros at the end of information to ensure the stability of the LDPC code encoder.

LDPC codes;protograph;CCSDS standard;feedback shift registers;deep-space application

TN911.22

:A

:1674-6236(2017)05-0057-04

2016-03-15稿件编号:201603191

龚杨阳(1991—),女,江西上饶人,硕士研究生。研究方向:数字信号与图像处理。