可编程器件在电工电子实验案例教学中的改革与探索

孙科学,郭宇锋,刘芫健,肖 建,谌 静

(南京邮电大学 电子科学与工程学院,江苏 南京 210023)

可编程器件在电工电子实验案例教学中的改革与探索

孙科学,郭宇锋,刘芫健,肖 建,谌 静

(南京邮电大学 电子科学与工程学院,江苏 南京 210023)

针对目前高校电工电子实验教学中存在的问题,该文从提高学生实践动手能力出发,在电工电子实验课程中引入可编程逻辑器件。把传统电子电路设计与FPGA设计做了比较,锻炼了学生基于模块化设计数字电路的能力以及调测复杂电路的水平。将组合逻辑和时序逻辑结合,通过VHDL语言设计动态显示典型案例,该案例可以作为其他单元电路设计的模板,突出了基于硬件描述语言设计硬件电路的灵活性。实践表明,案例教学法作为一种交互式的教学方法,增强了学生学习的兴趣,使学生主动参与学习,提高了学生对实际工程的认知能力和解决问题的综合能力。

电工电子实验;现场可编程门阵列;案例教学; 可编程器件

电工电子实验是一门理论性、工程性、技术性、实践性和实用性都很强的课程,在南京邮电大学是一门独立设置的实验课程,是一门重要的必修学科基础课,同时也是江苏省重点建设课程和省级精品课程。本课程被视为工科学生进入电子工程领域的入门课程,是联系公共基础课程和专业课程的重要桥梁。目前数字电路的发展日新月异,有必要对数字电路部分的实验进行更新[1-4]。

随着微电子设计技术和工艺的发展,数字集成电路从电子管、晶体管、中小规模集成电路、大规模超大规模集成电路(very large scale integrated circuit,VLSIC),逐步发展到今天的专用集成电路(application specific integrated circuit,ASIC)。ASIC的出现降低了电子产品的生产成本,提高了系统的可靠性,缩小了电子设计的物理尺寸。但ASIC设计周期长,改版投资大等缺陷也制约了其应用范围。

可编程器件的开发可以用原理图输入的方法或者采用硬件描述语言(HDL)的方法设计。原理图输入可控性好,比较直观,但设计大规模CPLD/FPGA时显得很烦琐,移植性稍差。HDL设计方法开发可编程器件可移植性好,使用方便,但直观性不如原理图。在稍复杂的FPGA/CPLD设计中,通常采用原理图和硬件描述语言相结合的方法进行电路设计,适合用原理图的地方就用原理图,适合用硬件描述语言的地方就用硬件描述语言,并没有强制的规范。在较短的时间内,用熟悉的工具设计出稳定、高效并符合设计要求的电路才是设计人员的最终目的[5-6]。

在较为完整的实验训练中引导学生综合运用数字电路的相关知识,让学生了解电子电路实现方法的多样性及根据工程需求比较选择技术方案。学习时分复用技术的动态显示原理,运用数字电路与逻辑设计理论和相关电子技术,按照分模块设计与调测的方法[7-13],完成4位数码管动态显示实验。同时训练学生的可编程器件的设计能力,基于硬件描述语言的逻辑设计能力,培养学生的数字电路设计和分析能力,提升学生硬件调测的工程素质。

本文以案例教学的方式体现可编程器件在现代数字电子电路中的应用,突出基于硬件描述语言设计硬件电路的灵活性。

1 电工电子实验课程案例

本案例以动态显示为例研究数字电路的设计方法,对传统的基于中小规模集成电路的数字电路设计和基于可编程逻辑的现代数字电路进行对比,体现出现代数字电路设计的优势和特色。

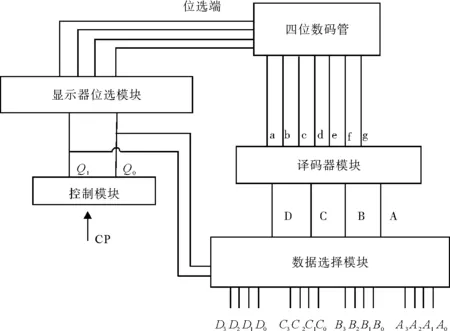

动态显示的特点是由位选线控制数码管的有效显示。这样就没必要每一位数码管配备一个七段译码器,从而可以简化硬件电路。所谓动态扫描显示即轮流向各位数码管送出字形码和相应的位选信号,利用发光管的余晖效应和人眼视觉暂留效果,给人的直观感觉是多位数码管同时显示。

通过学习时分复用技术的动态显示原理,运用数字电路与逻辑设计理论和相关电子技术,按照分模块设计与调测的方法,完成4位数码管动态显示实验。同时训练学生的可编程器件的设计能力,基于硬件描述语言的逻辑设计能力以及培养学生的数字电路设计和分析的能力。

图1 动态显示电路系统结构图

2 实施方案

2.1 基于中小规模集成电路实现

根据设计原理,将动态显示分为计数控制模块(7474)、位选模块(74139)、数据选择模块(74153)和译码显示模块(7448,数码管)4个模块进行调测。总体电路通过Multisim11仿真,电路图如图2 所示。

2.2 基于FPGA实现4位动态显示电路

2.2.1 基于VHDL硬件描述语言,采用层次化设计方法实现。

系统设计的顶层如图3所示,其中的mux4(位宽为4 bit的4选1数据选择器)模块、Two_Bit_Counter(2位加法计数器)以及decoder(2-4线译码器)由VHDL硬件描述语言设计。由于这3个模块实现起来比较简单,在此不再列出VHDL语言代码。将各底层模块通过Create schematic symbol生成原理图符号,通过原理图输入完成顶层设计。

图2 基于中小规模集成电路实现4位动态显示整体仿真图

图3 基于混合输入的顶层设计原理图

2.2.2 通过VHDL语言将该功能作为一个模块进行设计。

设计由时序逻辑进程、模4计数器进程、2-4线译码器电路和数据选择器构成,具体设计如下:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

Use ieee.std_logic_unsigned.all;

entity dyn_display is

Port (clk: in STD_LOGIC;

rst: in STD_LOGIC;

D3: in STD_LOGIC_VECTOR (3 downto 0);

D2: in STD_LOGIC_VECTOR (3 downto 0);

D1: in STD_LOGIC_VECTOR (3 downto 0);

D0: in STD_LOGIC_VECTOR (3 downto 0);

Ena_out : out STD_LOGIC_VECTOR (3 downto 0);

D_out : out STD_LOGIC_VECTOR (3 downto 0));

end dyn_display;

architecture Behavioral of dyn_display is

signal cnt: std_logic_vector (1 downto 0);

begin

Count: process (rst,clk) --计数器进程

begin

ifrst= ′0′ then

cnt<= "00";

elsifclk′event andclk= ′1′ then

cnt<=cnt+ ′1′;

end if;

end process;

withcntselect --组合逻辑,译码器

Ena_out<= "0111" when "00" ,

"1011" when "01" ,

"1101" when "10" ,

"1110" when others ;

mux_4: process (cnt,D3,D2,D1,D0) --组合逻辑,数据选择器

begin

ifcnt="00" then

D_out <=D3;

elsifcnt="01" then

D_out<=D2;

elsifcnt="10" then

D_out<=D1;

else

D_out<=D0;

end if;

end process mux_4 ;

end Behavioral;

程序中D3、D2、D1、D0分别对应图3中BCD3、BCD2、BCD1、BCD0,Ena_out对应图3中Y0Y1Y2Y3,D_out对应图3中DCBA。

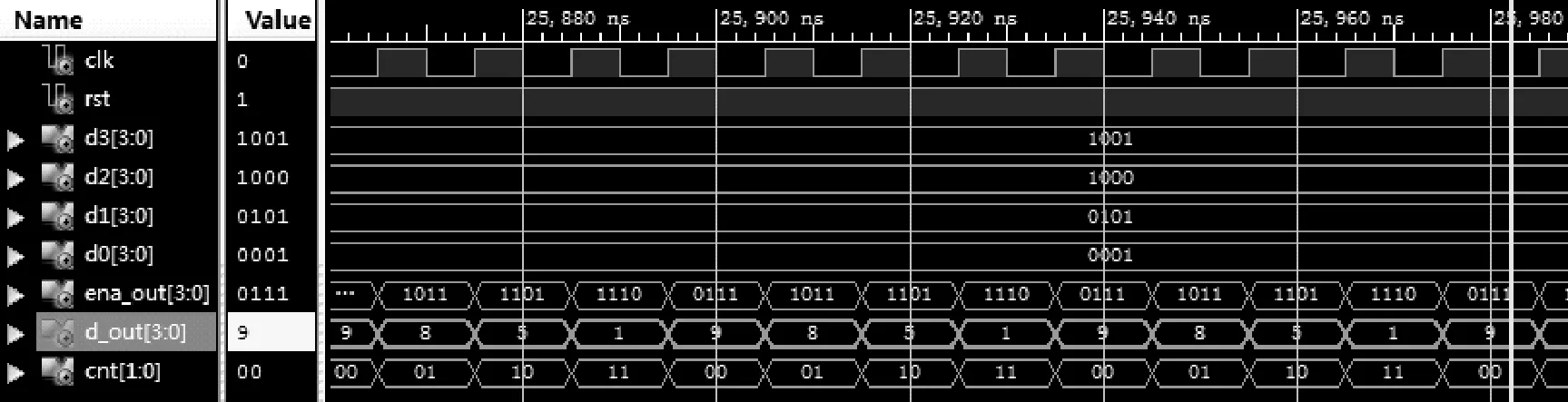

2.2.3 基于FPGA方案的实验仿真

激励信号需给出待测模块的所有输入的逻辑关系,包括输入数据信号D0、D1、D2、D3,时钟信号clk、清零信号clr。测试仿真图如图 4所示。

图4 4位动态显示ISE仿真图

3 结束语

把传统的基于中小规模集成电路的电子电路设计与现代FPGA电路设计做比较,锻炼了学生基于模块化设计数字电路的能力以及调测复杂电路的能力。本实验案例将组合逻辑和时序逻辑结合,通过VHDL语言设计这一典型案例,该案例可以作为其他单元电路设计的模板,突出了基于硬件描述语言设计硬件电路的灵活性。

案例教学法作为一种交互式的教学方法,引入到电工电子实验课程的教学中,增强了学生学习的兴趣,使学生主动参与学习,提高了学生对实际工程的认知能力和解决问题的综合能力。

[1]蔡立娟, 张瑜, 姜淑荣.“电子技术”课程实验教学改革的探索与实践[J].教育与职业, 2011(3): 172-173.

[2]孙科学, 张瑛, 唐珂, 等.Multisim11在电工电子实验中的应用[J].科技视界, 2014(34): 39-39.

[3]吴戈.新课程理念下改进电工电子实验教学方法的研究[J].教育与职业, 2011(36): 164-165.

[4]吴新开, 于立言, 俞建中.电工电子创新实验教学体系的研究与实践[J].实验室研究与探索, 2004, 23(3): 51-53.

[5]彭安华.电工电子实验教学改革探索[J].中国现代教育装备, 2010(1): 97-99.

[6]李锡, 林连山, 麻志滨, 等.加强实验教学改革与创新,推动电工电子实验中心建设[J].实验技术与管理, 2012, 29(7): 118-120.

[7]郭志雄.电工电子实践教学改革的探索与实践[J].教育与职业, 2013(2):155-156.

[8]曹海平, 管图华.基于CDIO理念的电工电子实训教学改革与实践[J].实验室研究与探索, 2013, 32(1): 140-142.

[9]邱欣寅, 袁志骞.应用型本科FPGA课程教学模式的探索[J].教育教学论坛, 2014(5): 210-211.

[10]刘外喜, 刘文喜, 喻萍, 等.基于在线实验室的教学模式的研究[J].微型机与应用, 2011, 30(14): 51-53.

[11]周莉莉, 周淑阁, 井娥林.FPGA课程教学方法的探讨与研究[J].实验室科学, 2013, 16(3): 65-66.

[12]张瑜, 蔡立娟, 韩春玲.新课程理念下电工电子教学改革初探[J].教育与职业, 2012(5): 114-115.

[13]孙科学, 张瑛, 唐珂, 等.基于FPGA的电工电子实践课程的改革与探索[J].电子制作, 2015(15): 68-70.

A Reform and Exploration in the Electrical and Electronic Experimental Course Using FPGA

SUN Kexue, GUO Yufeng, LIU Yuanjian, XIAO Jian, CHEN Jing

(College of Electronics Science and Engineering, Nanjing University of Posts and Telecommunications, Nanjing 210023, China)

Focus on the problems existing in the electrical and electronic experimental teaching in colleges and universities, in order to improve students’ practice ability, this paper introduces the programmable logic devices in electrical and electronic experimental course.The traditional electronic circuit design is compared with FPGA design, thus it exercises the students’ ability of designing digital circuit based on modular, and the debugging level for complex circuits.Combing the combinatorial logic with temporal logic, we design a typical case with the dynamic display using VHDL language.This case can be used as a template for other unit circuit design, and highlights the flexibility of designing a hardware circuit based on a hardware description language.Practice shows that the case teaching method, as an interactive teaching method, enhances students’ interest in learning and makes students take part in learning actively and improve students’ comprehensive ability of cognition and solving problems.

electrical and electronic experimental; FPGA; case teaching; programmable device

2015-06-05;修改日期:2016-11-25

江苏省高等教育教改研究课题(2015JSJG226, 2015JSJG227);电子信息类专业教学指导委员会研究课题(2016-Y14);南京邮电大学重点教学改革项目(JG03314JX54, JG03314JX53, JG03315JX07);南京邮电大学实验室工作研究课题(2016XSG02);江苏高校品牌专业建设工程资助项目(TAPP)资助。

孙科学(1981-),男,硕士,副教授,主要从事电子电路设计,嵌入式系统与通信软件设计方面的研究。

G642.0

A

10.3969/j.issn.1672-4550.2017.01.025