一种基于FPGA的多路视频合成及传输方法

王康景,陈卫松,方立军

(安徽师范大学 物理与电子信息学院,安徽 芜湖241000)

一种基于FPGA的多路视频合成及传输方法

王康景,陈卫松,方立军

(安徽师范大学 物理与电子信息学院,安徽 芜湖241000)

针对大型监控系统中实现多路视频数据合成单路的传输问题,提出了一种基于FPGA的多路视频合成及传输的设计方案。根据以太网协议,将不同视频流作相应的封装,缓存在各路对应的包FIFO中,通过采用轮询机制读取包FIFO中的视频数据帧,暂存在总的包FIFO中,并通过千兆以太网发送,实现多路视频数据流合成单路传输。实验结果表明,该设计方案可实现视频数据快速准确的传输,极大地提高了传输效率和可靠性。

FPGA;包FIFO;高速缓存;视频监控;轮询

0 引言

近年来,随着视频传输和网络监控技术的发展,视频监控在工业和安防等领域得到了广泛的应用。在视频监控系统中,监控摄像头的数量越来越多,覆盖的区域也越来越大。传统的视频传输方式将单个摄像头采集到的数据通过单根线路进行传输,对于庞大的监控网络来说,极其浪费资源[1]。如何在保证视频数据传输可靠性的前提下,降低线路传输的数量、提高传输的效率成为一个关键的问题。

针对以上问题,本文先给出了系统的总体设计方案,并详细地分析包FIFO的设计和多路数据合成的原理。通过对FPGA灵活快速地操作,实现多路数据合成单路,并进行可靠的远程传输,本设计方案适用于大型视频监控系统[2]。

1 系统原理及结构

图1为系统总体框架图。FPGA采集多路输入的视频数据[3],并根据IEEE802.3以太网协议分别对视频数据进行封装[4]。将封装后的数据帧快速缓存在包FIFO中,采用轮询机制[5],检测并判断各路包FIFO中empty信号的状态,以帧为单位读取包FIFO中的数据,缓存至下一级总的包FIFO内。发送模块读取包FIFO内部的数据帧,进行CRC校验码的计算[6],并添加至数据帧中,同时在数据帧前加入前导码和帧定界符,通过千兆以太网物理芯片发送出去[7]。

图1 系统总体框架图

每路封装的视频数据帧中加入了数据流号的标志,使得在接收端能够解析出视频数据[8],根据标志送入不同的终端处理。只要各路数据带宽的总和不大于千兆以太网[9]传输带宽,就不会产生视频图像的突变现象,从而提高了传输效率和传输的可靠性。

2 包FIFO的设计

视频数据流的时钟速率要远低于发送时钟的频率,实现数据流的合并必须进行异步时钟域处理[10]。一般异步处理采用异步字节FIFO或者包FIFO,而异步字节FIFO[11]只适用于数据量较少、单字节读写的情况,对于以数据帧为单位的读写及高速的数据帧缓存[12]操作,需要采用包FIFO。

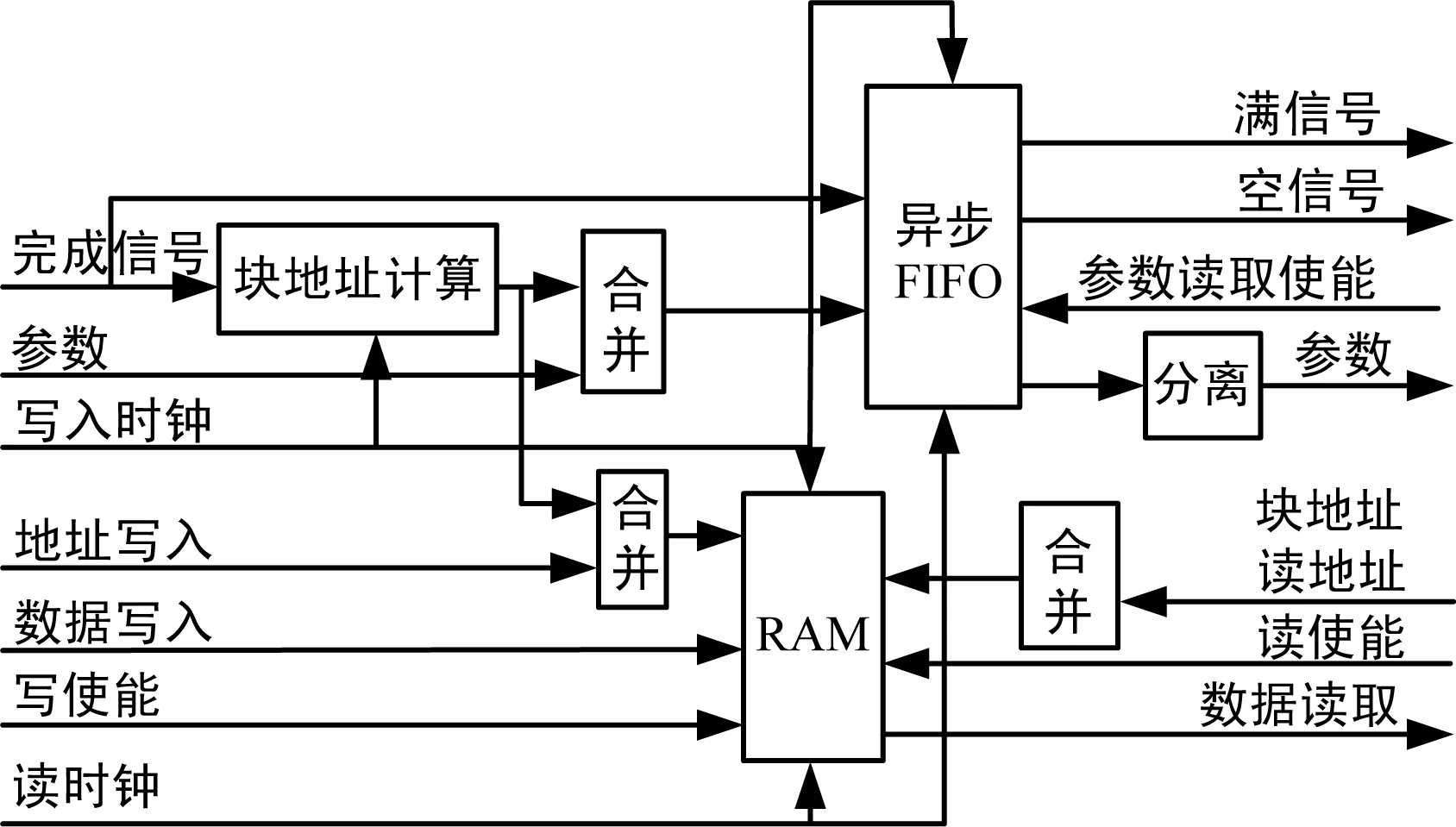

将包FIFO分为4个块,每块的存储大小相等,其中地址的高2位表示块地址。图2是该设计中的包FIFO,它是由异步字节FIFO、RAM以及其他逻辑单元组成。

图2 包FIFO内部结构

图2中,异步FIFO用于缓存块地址、视频数据流的参数及数据包的长度,RAM用于缓存视频数据帧。对包FIFO的读写操作如下:

当一帧数据写入时,先把视频数据帧写入RAM中,同时将视频数据流的参数及数据帧的长度计算出来,暂存于参数寄存器中。一帧数据帧写完后,检测完成指示信号是否有效。若完成信号有效,把该信号作为异步FIFO写使能信号,将视频数据流的参数及块地址写入异步FIFO中,并对块地址进行加1处理;若完成信号无效,则不对异步FIFO及块地址进行操作,之前写入RAM中的数据会被下一次的数据写入覆盖。当读取包FIFO中的数据帧时,先读取异步FIFO中的数据(包括数据帧的块地址、参数及其长度)。根据读取的数据的长度,发出对RAM[13]读取的使能和地址信号。将块地址作为高位,与读地址进行位合并,读取RAM中缓存的视频数据。

通过以上对包FIFO的读写控制,既能够对视频数据帧进行缓存,又能够进行异步时钟域的处理,从而大大提高了数据传输的可靠性。

3 多路合并的实现

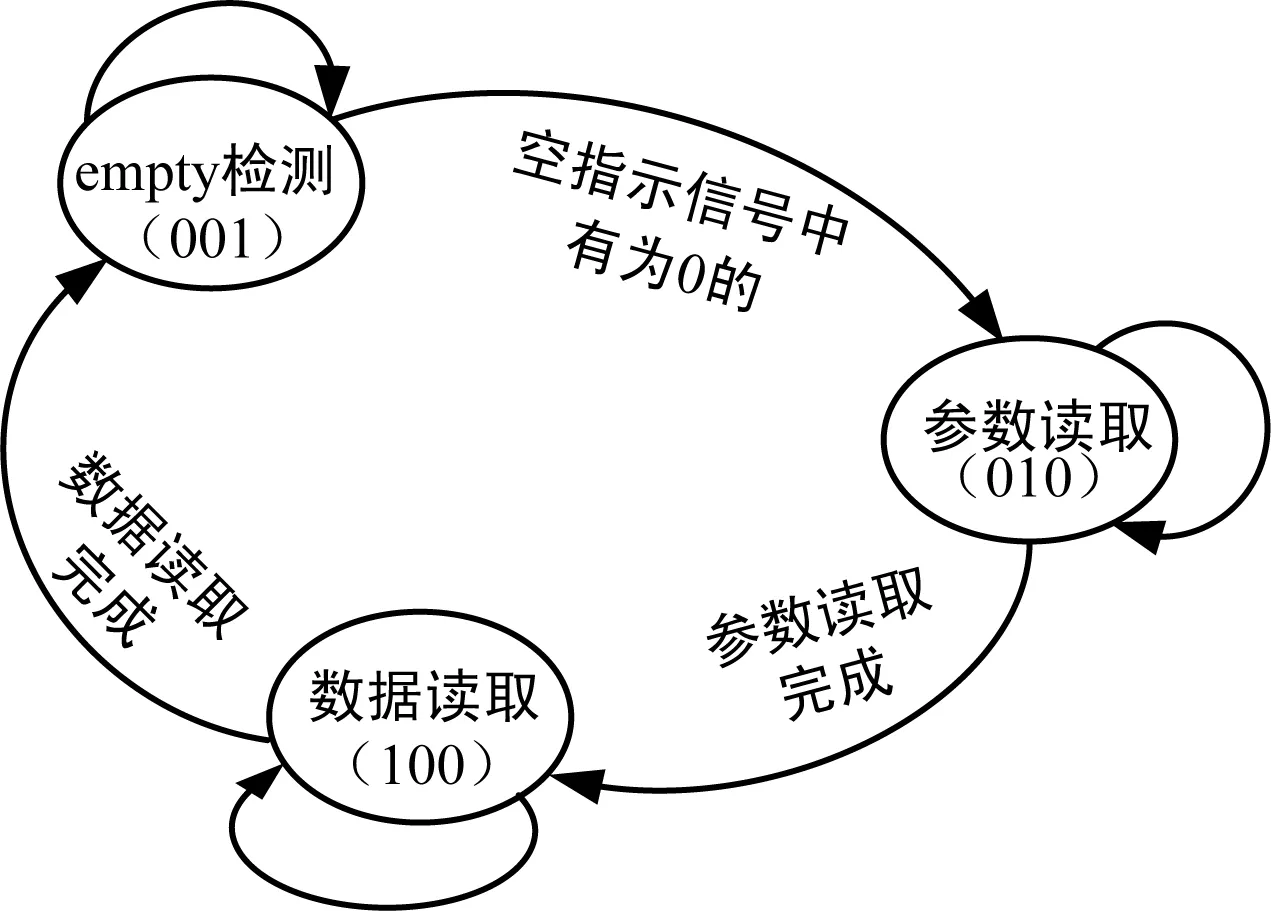

经封装的各路视频数据帧缓存在各路对应的包FIFO中,合并的目的是采用时分复用[14]的思想及轮询机制,将各路的视频数据帧合并成单路,进行相应传输。状态机[15]具有高效稳定的特点,能够将复杂的控制逻辑分解成有限个稳定状态,因此对于高速信号处理十分适用。在本设计中,采用三段式状态机实现合并的功能,并通过参数来设置合并的路数,其结构原理图如图3所示。

图3 多路合并实现原理

初始状态通过循环对各路包FIFO的empty进行检测,若检测到empty信号为0,说明该路包FIFO中至少有一帧数据,则暂存对应的序列号,并跳转至下一状态。向对应包FIFO中的异步FIFO发出有效的读使能信号,读取视频数据帧的块地址、数据帧长度及参数,完成该状态之后,跳转至下一状态。根据视频数据帧的长度信息,向包FIFO中的RAM发出有效的读使能及读地址信号,将块地址与读地址进行位合并,作为RAM读地址,读取暂存其中的视频数据帧,并输入下一级的包FIFO中。读取完成之后,向下一级包FIFO给出完成信号,同时将序列号加1跳转至empty信号检测状态,继续执行以上的状态。

各路视频数据流的带宽总和低于千兆以太网的发送带宽,轮询机制使得各路包FIFO中视频数据能够有效及时地发送出去,包FIFO不会出现满状态,即数据不会存在丢失现象。同时也不会产生延时,从而能够保证高可靠性传输。

4 实验结果及分析

本实验通过像素为30 W的2个摄像头OV7670采集视频数据,将封装完成之后视频数据流合并成单路,并通过千兆以太网物理芯片发送出去;接收端对接收的视频数据帧进行解析校验,并根据数据帧中的数据流号标志传输至相应的终端系统,通过VGA实时显示[16],其硬件电路如图4所示,经接收端解析校验后的单路视频图像如图5所示。

图4 视频传输的硬件系统

图5 接收实时显示的图像

该实验结果表明视频数据流在合并的过程中并未丢失,对视频图像显示的质量没有造成影响。同时,在该系统中,噪声对视频图像影响较小,相对于一般道路上的视频监控图像,清晰度有所改善。

5 结束语

本文基于FPGA实现了千兆以太网多路视频合成及传输的系统,对具有异步处理及缓存功能的包FIFO和多路视频数据帧合成单路传输的实现进行了详细的阐述及分析,并通过实验结果很好地论证了系统的性能。多路视频合成及传输方法在视频传输系统中的应用,不仅提高视频图像传输的可靠性,而且对视频传输的效率也有很大的提高。该方法提高了产品的质量,同时降低了产品设计和维护成本,对多种视频传输和监控系统等更多领域的应用与研究具有重要意义。

[1] 黄凯奇,陈晓棠,康运锋,等.智能视频监控技术综述[J].计算机学报,2015,38(6):1093-1118.

[2] 邵应昭,任爱锋,初秀琴.基于FPGA的视频监控系统[J].电子技术应用,2008,34(5):20-22.

[3] 张龙滨,黎福海.一种基于FPGA的实时视频采集与远程传输系统[J].电视技术,2011,35(17):45-47.

[4] 冯永茂,徐秀知,陈 宇,等.基于快速以太网物理层的实时高速数字视频传输[J].电子器件,2007,30(1):144-147,151.

[5] 柳虔林,赵东风,丁洪伟,等.轮询系统的演进及发展[J].无线电通信技术,2013,39(2):55-59.

[6] 杨利娟,陈多观.循环冗余校验CRC的分析及硬件实现[J].苏州科技学院学报:自然科学版,2010,27(4):51-53.

[7] 王立莹,王俊芳,曹 琨,等.VLAN及在千兆以太网MAC中的实现[J].无线电工程,2013,43(1): 1-3.

[8] 李前进,张 熙,王寅龙,等.基于直接线性变换法的视频图像解析[J].无线电工程,2013,43(3): 47-50.

[9] 韦 宏,付友涛,孔凡鹏,等.基于FPGA的千兆以太网设计[J].现代电子技术,2012,35(18):56-59.

[10]王晓婷.跨时钟域设计方法研究[D].西安:西安电子科技大学,2012.

[11]黄忠朝,赵于前.一种实现高速异步FIFO的FPGA方法[J].计算机工程与应用,2010,46(3):13-15.

[12]向厚振,张志杰,王 鹏.基于FPGA视频和图像处理系统的FIFO缓存技术[J].电视技术,2012,36(9):41-43.

[13]孙培燕,李克俭,蔡启仲,等.FPGA数据总线宽度不相等的双口RAM的设计[J].科学技术与工程,2014,14(35):249-253.

[14]孔繁青.时分复用设备动态帧结构技术研究[J].无线电通信技术,2005,31(4):12-14.

[15]孔 昕,吴武臣,侯立刚,等.基于Verilog的有限状态机设计与优化[J].微电子学与计算机,2010,27(2):180-183.

[16]魏晓辉.基于FPGA的实时视频图像采集与VGA显示系统设计研究[D].西安:西安电子科技大学,2015.

A Method of Multi-channel Video Synthesis and Transmission Based on FPGA

WANG Kang-jing,CHEN Wei-song,FANG Li-jun

(Anhui Normal University,College of Physics and Electronic Information,Wuhu Anhui 241000,China)

In view of the transmission problem of multi-channel video data synthesis in large-scale monitoring system,a kind of multi-channel video synthesis and transmission method based on FPGA is proposed to achieve multi-channel video data synthesized in single channel.Different video streams are encapsulated correspondingly according to Ethernet protocol.The encapsulated data is cached in the package FIFO of corresponding channel.A polling mechanism is used to control the reading of the data in packet FIFO.The data is temporarily stored in the total package FIFO and sent through the Gigabit Ethernet.Accordingly synthesis of multi-channel video data stream is achieved.Experiment results show that this design scheme can achieve rapid and accurate transmission of video data.It also greatly improves the transmission efficiency and reliability.

FPGA;package FIFO;caching;video surveillance;polling

10.3969/j.issn.1003-3114.2017.01.11

王康景,陈卫松,方立军.一种基于FPGA的多路视频合成及传输方法[J].无线电通信技术,2017,43(1):44-46.

2016-09-23

国家自然科学基金项目(61401004)

王康景(1992—),男,本科,主要研究方向:通信工程。陈卫松(1973—),男,博士,副教授,主要研究方向:视频及音频信号处理。

TP393

A

1003-3114(2017)01-44-3