基于信息复用的多路x265视频编码系统设计

程栋彬,高志勇,张小云

(上海交通大学 电子工程系 图像通信与网络工程研究所,上海200240)

基于信息复用的多路x265视频编码系统设计

程栋彬,高志勇,张小云

(上海交通大学 电子工程系 图像通信与网络工程研究所,上海200240)

为了满足不同网络环境下的用户需求,视频节目往往需要经过多次编码以产生不同码率的多个码流。这种多次独立编码方式存在计算资源消耗大和效率低等问题,利用视频在不同码率编码时存在的编码信息相关性,设计了基于编码信息复用的多路x265视频编码系统,使多个从编码器复用主编码器产生的编码信息,如编码单元(CU)的层次划分信息、预测单元(PU)的模式判别信息以及运动估计参考帧信息等,从而大幅提高多路编码效率。该系统支持单路视频输入,进行基于信息复用的多路编码后,同时输出不同码流的多路码流。实验结果表明,与传统的多次独立x265编码相比,该系统在保证视频质量的前提下,对高清1080p和准高清720p视频分别节省了43.32%和52.79%的编码时间。

视频编码;HEVC;x265;编码信息复用;多路编码;多线程

视频内容从发送源端到终端,用户往往需要应对各种不同的网络传输环境和终端设备类型等应用因素,包括网络类型、网络带宽、设备显示屏大小等,因此对于同一视频内容,视频服务提供商往往需要对其进行多次编码以得到多种码率的视频以满足各种用户需求。另一方面,在视频编码领域,目前广泛使用的H.264/AVC[1]标准正逐渐被新一代高效率视频编码标准HEVC(High Efficiency Video Coding)[2]取代,HEVC相比H.264能提高1倍左右的视频压缩率,但也引入了3~10倍的编码复杂度。基于HEVC标准的x265[3]是一款面向实用的高效视频编码器,它通过多线程机制支持帧级并行和行级并行编码,并集成了大量的算法优化、汇编加速、单指令多数据实现等,从而极大地提高了编码速度。然而,在Intel的高性能8核处理器上,x265编码器仍无法实现高清视频的实时编码,在更多核的服务器上运行时x265仍面临并行效率和处理器使用率较低的问题。因此,利用新一代HEVC高效编码技术对同一视频进行多次独立编码以产生不同码率的多路码流,面临着计算复杂度极高、资源消耗大、编码效率低等问题。

基于上述现状,本文利用视频在不同码率编码时存在的编码信息相关性,设计了基于编码信息复用的多路x265视频编码系统,使多个从编码器复用单个主编码器产生的编码信息,如编码单元(CU)的层次划分信息、预测单元(PU)的模式判别信息以及运动估计参考帧信息等,从而大幅提高多路编码效率。另外,通过多路x265编码器的并行执行,本系统提高了并行效率和处理器使用率,进一步降低了总编码时间。

1 系统设计和架构

1.1 系统框架

多路x265视频编码系统结构框图如图1所示,系统输入原始的YUV格式视频,经过多路编码器输出该视频的多种码率码流。系统中的多路编码器分为两类,分别是x265主编码器和x265从编码器。主编码器在编码的同时保存并输出编码信息,从编码器则获取主编码器输出的编码器信息,并利用它们简化自身的编码运算。整个系统由一个主编码器和若干个从编码器组成,一路输入视频通过包含1个主编码器和N个从编码器的x265多路编码系统,一次性编码输出N+1路不同码率的视频码流。

图1 多路x265视频转码系统框架示意图

多路x265视频编码器系统有两大核心机制,首先是主编码器到从编码器的信息复用机制,该机制有效地降低了从编码器的编码复杂度;其次是多线程实现的多路编码器机制,该机制使得这些编码器在并行多路编码的同时又能够实现信息交互。本系统中复用的编码信息包括编码单元(CU)层次划分、预测单元(PU)的模式判别,以及运动估计参考帧[2],这些模块都是编码过程中计算复杂度很高的环节,复用这些模块的信息能最大程度地减少编码时间。

主编码器产生尽可能准确的编码信息,因此主编码器设置的码率应适当偏大,使生成的信息更准确有效。同时,为了尽可能让从编码器与主编码器相关性最大,应使主编码器设置的码率接近所有码率的中间值。综上,在固定码率编码时,一般将主编码器的码率设为中等偏大;在固定量化参数(QP) 编码时,一般将主编码器的量化参数设为中等偏小。

1.2 主从编码器信息复用控制

x265编码器的重要特性之一就是多线程并行编码,具体地分为多帧并行和WPP(Wavefront Parallel Processing)行级并行[3]。多帧并行指的是x265主线程开启多个帧级线程,每个帧级线程编码一帧。具体地,每个帧级线程开启多个行级线程,每个行级线程编码一个CTU[2]行。在多核处理器环境下,x265编码器同时存在多个线程在并行编码多个帧中的多个CTU行,这是下述的信息复用控制机制的设计基础。

主从编码器通过内存作为编码信息的传递渠道,其信息传递机制类似于多线程并发问题中的生产者-消费者模型。考虑到单个x265编码器的并行性,因此该模型中无论是生产者还是消费者的数目都不唯一,而且它们访问内存进行读写的时间顺序无法确定。为了保证编码信息传递的正确性和高效性,在主编码器产生编码信息时,应当对其按照图像序列号(POC)[4]和编码树单元(CTU)的位置进行标记,从编码器读取信息时,则按照当前编码单元所在的POC和CTU位置坐标去内存中相应位置取得相应数据。

如图2为本系统设计的主从编码信息传递机制示意图,中间立体多帧结构表示编码复用信息缓冲区,每个正方形区域用于存储一个CTU的所有复用信息,左下角编号i用于标记存储的图像序列号POC,阴影部分表示主编码器已经使用的空间,从编码器按照图像序列号i和CTU的坐标(x,y)从中读取。值得强调的是,由于主从编码器对复用信息缓冲区的读写实际上是多线程间同步问题和临界资源的访问问题,因此需要对其中的CTU复用信息用线程锁加以保护,确保同一时间只有单个线程对其进行操作。

图2 主从编码器信息传递示意图

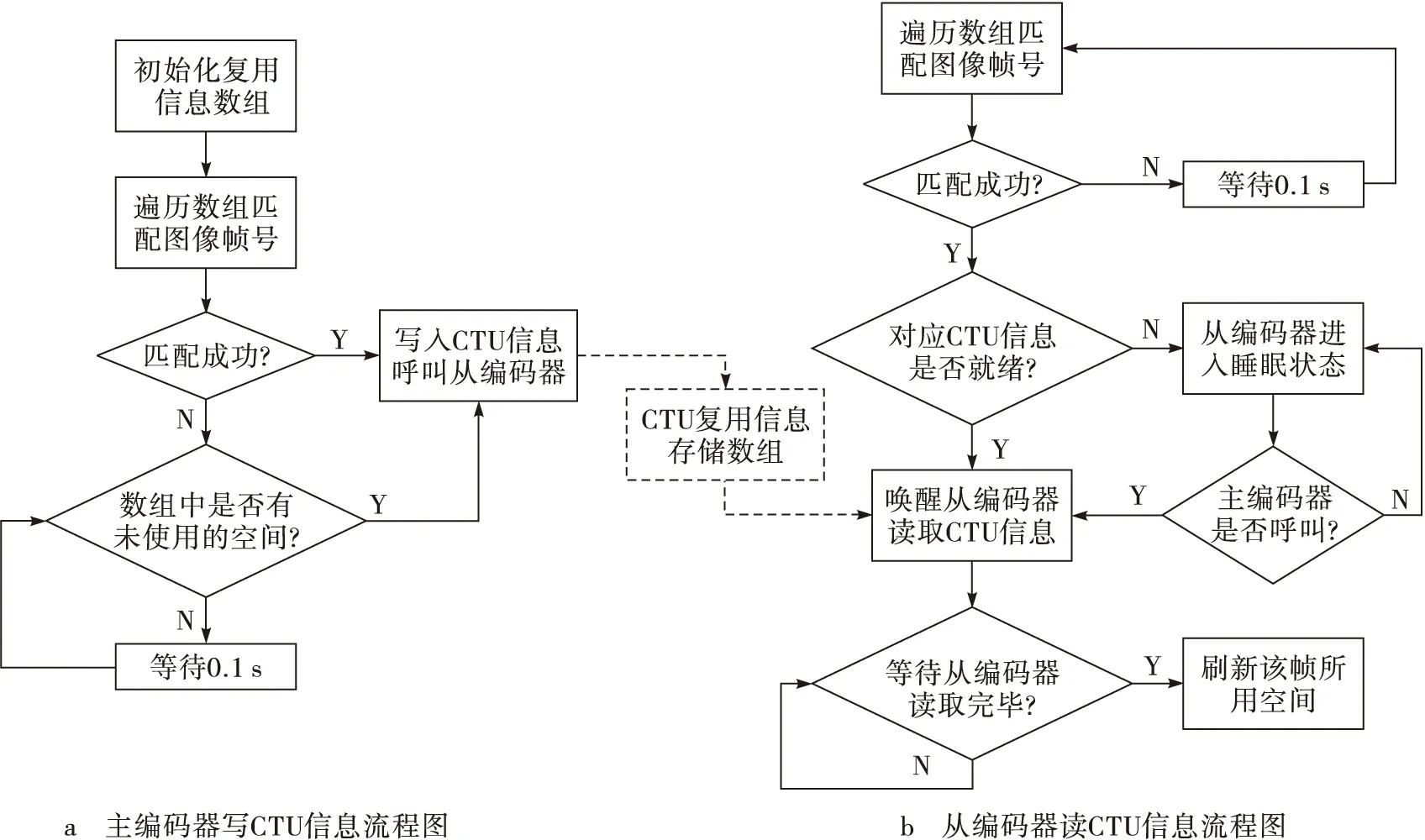

图3为主从编码器信息传递流程图,图3a为主编码器输出信息到CTU信息缓冲区流程图,主要过程是将复用的编码信息按照当前POC以及CTU的坐标放到缓冲区的特定位置中,然后呼叫并唤醒可能在等待该信息的从编码器。图3b为从编码器从CTU信息缓冲区中获取编码器信息流程图,主要过程是按照POC以及CTU坐标在缓冲区中找到特定位置后,如果信息已经就绪则直接读取,否则进入睡眠状态等待主编码器的呼叫。另外,读取过程中需要统计每个位置中CTU信息的读取次数,当该次数等于从编码器个数时,则刷新该部分空间以便重用。

图3 主从编码器读写CTU信息传递流程图

上述的主从编码器复用信息传递机制充分地考虑了x265编码器的并行性,以CTU信息为基本复用单元,对其标记图像序列号POC以及CTU的坐标,准确和高效地实现了信息传递。此外,通过对从编码器读取信息次数进行统计,保证了每个从编码器都能获得正确的编码信息。

2 主从编码器信息复用算法

HEVC是为高清、超高清视频序列而设计的编码标准,相比H.264/AVC的16×16像素大小的分块方式[1],HEVC编码树单元CTU达到64×64像素大小。同时,它引入了更为灵活的像素块划分结构,包括编码单元(CU)、预测单元(PU)、变换单元(TU)[2]等。这些基于四叉树结构的编码方式能得到更准确的划分模式,然而在递归地划分和搜索最佳模式时,每种可能的CU、PU、TU模式都需要进行RDO(Rate-Distortion Optimization)[2]的计算,因此引入了极为庞大的计算量。正因为HEVC编码器中上述过程占据相当部分的计算量,于是本系统对CU层次划分信息、PU模式判别信息、运动估计参考帧信息进行了复用。

2.1 CU层次划分信息

(1)

本系统中首先在主编码器中针对该CTU执行完整的划分过程,并将划分结果输出,从编码器得到主编码器该CTU的CU层次划分结果后,将其作为自身CU划分的参考。考虑到在x265编码器中,同一个CTU内部不同子CU的量化参数(QP)保持不变,因此复用算法将QP作为衡量指标,其核心思想如式(1)所示。设主编码器的某个CU层次划分结果为Depth主,从编码器的对应CU层次划分结果为Depth从。记从编码器当前CTU的量化参数为QP从,主编码器的为QP主,若QP从

2.2 PU模式判别信息

将正方形的CU经过横向或者纵向的划分后得到的矩形像素块被称为预测单元(PU),PU的预测方式可分为四类,即Intra(帧内预测)、Inter(帧间预测)、Merge(合并相邻PU模式)、Skip(无残差模式)[5]这4种模式,对于每个PU,编码器需要依据RDO性能最佳的准则进行模式选择,该过程被称为PU模式判别。

本系统中首先由主编码器完成PU的模式判别过程,选出最佳模式并输出该信息,从编码器获知主编码器的PU模式判别结果后,按表1所示原则只对表中选中的模式进行判别和选择。例如,如果主编码器该PU的最佳模式是Intra,则从编码器的PU需要在Intra、Inter、Merge和Skip所有四种模式中进行判别和选择;如果主编码器选中了Merge模式,则从编码器只需要在Merge和Skip这两种模式中选择。简而言之,PU模式判别的四种模式从残差数据最多的Intra模式到无残差的Skip模式,它们所占用的码率开销依次降低,表1中的准则概括来说就是从编码器只在开销小于或等于主编码器的模式中进行判别和选择。

2.3 运动估计参考帧信息

对于预测单元PU的帧间预测模式(Inter),需要从参考帧中搜索找出同样大小的像素块作为当前块的预测值,使得真实值与预测值的残差最小,该过程被称为运动估计。运动估计往往选取多个参考帧进行搜索以达到最优,HEVC标准规定可以多达16个参考帧,实际应用中为降低计算复杂度通常设为3~5个,这些参考帧组成参考帧列表。PU的运动估计需要在参考帧中找到最佳匹配的像素块,该像素块所在的参考帧为最佳参考帧。而双向预测模式的B帧,则存在两个参考帧列表,并需要找出两个最佳参考帧[5]。

表1 PU模式判别复用算法的从编码器模式判别准则

主编码器从编码器IntraInterMergeSkipIntra√√√√Inter—√√√Merge——√√Skip———√

本系统的运动估计参考帧复用算法,首先主编码器对每个Inter模式的PU执行完整的运动估计,并将所有PU的最佳参考帧的帧号输出。从编码器在执行当前PU块的运动估计时,获取主编码器相应位置中所有PU的最佳参考帧(PU个数可能不唯一,因此最佳参考帧个数不唯一),并只在上述最佳参考帧列表中进行运动搜索匹配。对于双向预测的B帧,由于主从编码器帧结构相同,从编码器的当前帧同样是B帧,于是在前向和后向参考帧列表中,各自独立地选出最佳参考帧列表,然后完成前向和后向运动估计。该算法避免了从编码器在那些未被选中的参考帧中进行运动搜索,减少了搜索帧数,从而节省了运动估计的计算时间。

3 系统仿真与结果

本系统基于Intel多核处理器平台,中央处理器为Intel(R) Xeon(R) CPU E5-2697 v2 @2.7 GHz x24,Windows7操作系统。本系统基于x265开源代码的1.8版本进行开发,并调用其应用程序编程接口(API)得到两种功能的编码器,即x265主编码器和x265从编码器。多路编码系统支持x265的3种码率控制模式即固定量化参数(CQP)模式、固定码率(CBR)模式和固定质量(CRF)模式[3],为了评估本系统多路编码性能,测试时对每个测试序列使用1个主编码器、3个从编码器的结构,分别对应固定量化参数QP为22、27、32、37,以QP=27作为主编码器,并求出各自的平均码率、编码时间和处理器平均使用率。本系统的对照组为单路编码的原始x265编码器,对每个测试序列,同样分别采用上述4个量化参数进行4次编码,每次编码独立运行,并统计相应数据,所用的视频质量衡量指标为BDBR[6-7]。

表2给出了视频测试序列BasketballDrive在无复用的x265单路编码器多次编码的视频质量与时间结果。表3给出了BasketballDrive序列在本文的多路x265视频编码单次编码的多路输出结果。通过表2和表3中的结果计算可知,多路x265视频编码系统相比多次x265编码的BDBR仅为1.005%,即同等视频质量下码率仅增加1%,而全局编码时间节省为41.94%,与此同时,处理器平均使用率从66%增加到了79%。

表2 BasketballDrive测试序列在无复用的多次x265编码中的视频质量与时间性能

QP码率/(kbit·s-1)Avg-PSNR/dBY-PSNR/dBU-PSNR/dBV-PSNR/dB总编码时间/s处理器平均使用率/%2215914.2240.7739.5543.7845.03276282.3138.9737.7542.3342.90323136.8537.2335.9541.0541.11371675.0735.3433.8240.0439.7941.1166

表3 BasketballDrive测试序列在多路x265视频编码器中的视频质量与时间性能

QP码率/(kbit·s-1)Avg-PSNR/dBY-PSNR/dBU-PSNR/dBV-PSNR/dB总编码时间/s处理器平均使用率/%2216214.4940.8139.5743.9145.17276353.2139.0437.8042.4943.08323243.6237.2335.9741.0341.03371719.8435.2833.8839.7039.2425.6179

本系统共选取了5个分辨率为1 920×1 080和3个1 280×720的测试序列,测试结果如表4所示。无论是对1080p还是对720p测试序列,多路编码系统的平均BDBR都在0.5%左右,可认为同等码率下视频质量下降极其微小。此外,多路编码系统对两类序列均能提高处理器使用率,且对于更小的分辨率视频,该项提升更加显著。对于全局编码时间,1080p序列平均节省了43.32%,而720p序列平均则平均节省了52.79%。

表4 多路x265编码系统在不同序列下性能结果

测试序列时间节省/%视频质量BDBR/%处理器平均使用率/%原始x265多路编码1080p序列BasketballDrive41.94 1.0056679BQTerrace42.88 0.4896475Cactus43.50 1.3586378Kimono146.13 0.0277082ParkScene42.13-0.8165977平均值43.32 0.4136478720p序列FourPeople50.13 0.5564369Johnny53.68 0.1164468KristenAndSara54.57 0.8654871平均值52.79 0.5124570

4 结语

本文提出了基于主从编码器之间信息复用的多路x265视频编码系统,首先从系统框架、主从编码器信息复用控制等方面讲述了系统上层架构,阐述了上述结构的必要性和优越性;其次说明了包括CU层次划分、PU模式选择和运动估计参考帧等信息在内的编码信息复用算法,解释了主从编码器间信息复用算法的原理与过程。最后通过仿真与测试,给出了多路x265编码系统相比原始的多次x265编码的视频质量BDBR值、时间节省百分数、处理器使用率的变化等。

总之,多路x265视频编码系统利用主从编码器间编码信息的相似性,通过复用部分主编码器的编码信息,降低了从编码器的时间复杂度,提高了多核处理器使用率,成功地在视频质量几乎没有下降的情形下节省了一半左右的全局编码时间。

[1] POURZZAD M T, DOUTRE C, AZIMI M, et al. HEVC: the new gold standard for video compression: how does HEVC compare with H.264/AVC?[J]. IEEE transactions on consumer electronics magazine, 2012, 1(3):36-46.

[2] MCCANN K. High efficiency video coding (HEVC) test model 12 (HM 12) encoder description[S]. 2013.

[3] MulticoreWare Inc. x265 documentation[EB/OL].[2016-05-12]. http://x265.readthedocs.io/en/default/api.html.

[4] 毕厚杰. 新一代视频压缩编码标准——H.264/AVC[M].2版.北京:人民邮电出版社,2009,181-185.

[5] SULLIVAN G J, OHM J R, HAN W J, et al. Overview of the high efficiency video coding (HEVC) standard[J]. IEEE transactions on circuits and systems for video technology, 2012,22(12): 1649-1668.

[6] BJONTEGAARD G. Improvements of the BD-PSNR model [EB/OL].[2016-05-20]. http://www. researchgate. net/publ:catim/284626 737_Improvements-of-the-BD-PSNR-model.

[7] PATEUX S JUNG J. An excel add-in for computing Bjontegaard metric and its evolution[C]// Proc. of VCEG Meeting. Marrakech, MA:Citeseer, 2007:112-116.

[8] 姚佳,高志勇,张小云. 基于众核平台的多路超高清视频编码系统设计[J]. 电视技术, 2016, 40(4):7-11.

程栋彬,硕士生,主研视频编解码、视频转码等;

高志勇,博士生导师,主要研究高速图像与视频处理、数字电视等;

张小云,硕士生导师,主要研究视频编解码、高速视频处理等。

责任编辑:薛 京

Implementation and design of multi-channel x265 video encoding system based on encoding units’ information reusing

CHENG Dongbin, GAO Zhiyong, ZHANG Xiaoyun

(ImageCommunicationandNetworkEngineeringInstitute,ElectronicEngineering,ShanghaiJiaoTongUniversity,Shanghai200240,China)

To meet the demands of all consumers in different network conditions, the same video may need to be encoded for many times to produce different bitrate streams by video manufacturers. This kind of several times independent encoding leads to heavy computation expense and low encoding efficiency. In this paper, a multi-channel x265 video encoding system based on the similarity of encoding units’ information between different encoders is proposed. In the proposed system, number optional slave encoders reuse the encoding units’ information produced by one master encoder to substantially increase the multi-channel encoding efficiency, and these information mainly includes the following contents: the depth decision results of the coding units(CUs), the mode partition result of the prediction units(PUs), and the motion estimation reference frames for prediction units. This system has one raw video file as input, and result in multi encoded video streams of different bitrates at one time after information reusing encoding. Experimental results show that our system can separately save 43.32% and 52.79% encoding time for 1080P and 720P video sequences comparing with traditional several independent x265 encoders, while keeping the video quality almost not decreased.

video encoding; HEVC; x265; encoding information reusing; multi-channel encoding; multi-thread

程栋彬,高志勇,张小云.基于信息复用的多路x265视频编码系统设计[J]. 电视技术,2017,41(1):1-5. CHENG D B, GAO Z Y, ZHANG X Y.Implementation and design of multi-channel x265 video encoding system based on encoding units’ information reusing[J]. Video engineering,2017,41(1):1-5.

TN949.292

A

10.16280/j.videoe.2017.01.001

国家自然科学基金项目(61301116)

2016-06-07